- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- 32 bit flexbus bursts

32 bit flexbus bursts

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are having an issue with burst transfers on the Flexbus. We would like to transfer four 32 bit double words per burst. This is necessary to obtain the data throughput we need in our system. The reference manual does not show any specific timing diagrams for this type of transfer, but it does state in a table in section 32.4.12.2 that a port size of 32 bits can burst with 4 beats. Discussions with local FAEs suggest that this should work as we understand it.

I’ve defined chip select 2 for write burst accesses in our system. To that end, the chip select has been programmed as follows:

Register Value Description

FB_CSAR2 0x30020000 Sets the base address of the chip select to 0x30020000.

FB_CSCR2 0x00000108 No wait states, Burst writes enabled, auto terminated accesses

FB_CSMR2 0x00000001 Enables the chip select for range 0x30020000 to 0x3002FFFF, write are allowed.

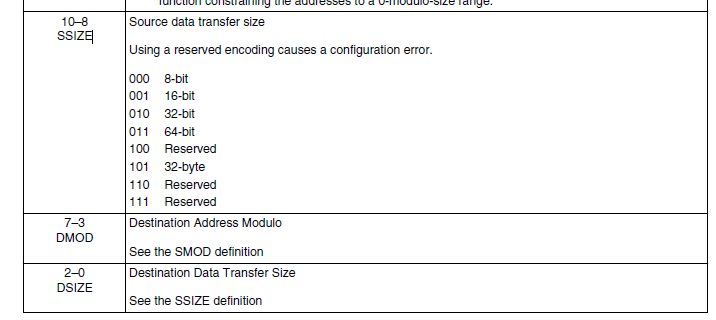

Additionally, we’ve set up a DMA to move multiple 32 bit double words out the port. When the DMA destination data transfer size is 32-bit, only single Flexbus accesses are observed. Does the DMA destination data transfer size need to be 32-byte to support bursting on the Flexbus? When we set the DMA destination data transfer size to 32-byte the DMA stalls and no transfers on the bus are observed. How does the DMA need to be configured to allow the Flexbus to transfer four 32-bit double words per burst?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

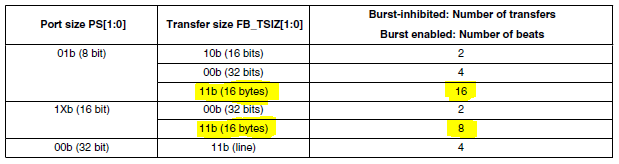

As I stated originally, we were assured by a Freescale FAE that we would be able to burst 4, 32 bit double words using the flexbus. That's one address clock, followed by 4 clocks of data (A different 32 bit double word of data for each clock). That as I read it it is 4 beats in line mode. Your last reply seems to be saying that the part isn't capable of 4 beats of 32 bit double words, which appears to be in direct contrast to what the table above says (see the last line, 00b is 4 beats.) Is the "4" in the table an error?

Your statement that our 32 bit burst is working is non-sensical. SInce the a single 32 bit double word being transferred in a burst is exactly the same as a 32 bit non-burst transfer. If that is what I wanted, I would not be trying to turn on burst mode.

We cannot use 8 or 16 bits in burst mode because that will cut our data throughput. I'm trying to get more data throughput, not the same or less. More than a single beat 32 bit (which looks the same burst mode enabled or not). I only tried the 8 and the 16 to see if the part could burst at all. It does seem to burst, but not for 4 beats at 32 bits.

I have a full 32 bit pipe to my FPGA, why would I want to burst at a smaller port size? I can tell you the answer, I do not. Bursting 32 bits at 4 beats is essential for my high bandwidth application. If bursting doesn't work, then what good is your part to me?

Is it possible to send data to a 32 bit Flexbus port in a 21111 configuration, or not? Yes, or No. If it is no, then your FAE's and your documentation are in serious error!

Is there a knowledgeable person to whom we can have a phone conversation? This back and forth exchange on the forum is taking much too long to resolve this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

please sent me some waveform including /FB_TBST and FB_TSIZs for 32 byte transfer with Flexbus burst enabled and disabled.

and

please try 64 bit DMA transfer ( hopefully you will see a burst with 2 beats) please send me and waveforms including /FB_TBST and FB_TSIZs also.

I need to discuss it with designer so I need those materials.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'll get something together soon, we are fighting our other DDR problem, and no time to do these tests at the moment.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

Finally I have confirmation from designers: Burst transfer between DMA and Flexbus is not possible. DMA is 64bit AHB bus master. Flexbus is 32bit data width AMBA AHB bus slave. The problem is the AMBA AHB 64bit width to AMBA AHB 32bit width bus converter on Vybrid can not convert input bursts with a data width of 64bits to output bursts with a data width of 32bits. Because of this, all requests that reach the FlexBus are single beat operations. Sorry for that.

The burst between Flexbus and the target memory is something else - it is are working when 8b or 16bit target memory port wide is used.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, this is what I thought. I am annoyed that we were promised that this would work by Freescale before we selected the Vybrid for our application. However, it is understood that the part is new and some specs may be in flux.

Fortunately, we were able to use non-burst mode. While we had very little margin, we have not seen an issue.

John Fielden

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I stated originally, we were assured by a Freescale FAE that we would be able to burst 4, 32 bit double words using the flexbus. That's one address clock, followed by 4 clocks of data (A different 32 bit double word of data for each clock). That as I read it it is 4 beats in line mode. Your last reply seems to be saying that the part isn't capable of 4 beats of 32 bit double words, which appears to be in direct contrast to what the table above says (see the last line, 00b is 4 beats.) Is the "4" in the table an error?

Your statement that our 32 bit burst is working is non-sensical. SInce the a single 32 bit double word being transferred in a burst is exactly the same as a 32 bit non-burst transfer. If that is what I wanted, I would not be trying to turn on burst mode.

We cannot use 8 or 16 bits in burst mode because that will cut our data throughput. I'm trying to get more data throughput, not the same or less. More than a single beat 32 bit (which looks the same burst mode enabled or not). I only tried the 8 and the 16 to see if the part could burst at all. It does seem to burst, but not for 4 beats at 32 bits.

I have a full 32 bit pipe to my FPGA, why would I want to burst at a smaller port size? I can tell you the answer, I do not. Bursting 32 bits at 4 beats is essential for my high bandwidth application. If bursting doesn't work, then what good is your part to me?

Is it possible to send data to a 32 bit Flexbus port in a 21111 configuration, or not? Yes, or No. If it is no, then your FAE's and your documentation are in serious error!

Is there a knowledgeable person to whom we can have a phone conversation? This back and forth exchange on the forum is taking much too long to resolve this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

I see, so in this case we talking about 32 bit line transfer (last line in the table). Flexbus itself should be able to transfer four 32-bit words in one line (or burst if you like).

Is /FB_TBST == 0 which is indicating burst transfer? I'm hesitating if it is possible, that you feed Flexbus with data too slow. What is the distance between each transfer of mentioned 64 single 32-bit word transfers? Could you send me some waveform including /FB_TBST and FB_TSIZs?

The data has to be transferred to Flexbus driver fast enough (from DMA or cache) - so it require burst from DMA to Flexbus. DMA can send data in burst only in selected data sizes for example 32bytes. see DSIZE in the table:

Not sure it will work since DMA uses 32 bytes and Flexbus 16 bytes - need to discuss it with designer if it will not work for you. So let me know it that helps.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have been using the DMA to transfer 32 bit words for a couple of weeks now. With the DMA, we get the single beat transfers back to back (no delay between the accesses).

The FB_TBST is being used at an nOE, but we could probably repurpose it temporarily. The SIZ bits are being used as GPIO for other purposes. We could probably look at those too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Opps, I meant to say, yes, we have setup the DMA to send 32 bytes to the flexbus. What we see are 8 single beat 32 bit transfers. Each transfer looks like a normal non-burst transfer with a total of 4 clocks (Address, data, with two clocks of buffer). With the DMA there are no additional clocks between each of the 8 transfers. Just not a 4 beat burst.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are not using Linux, or timesys for that matter. This is a question related to the hardware. Is there a flexbus knowledgable hardware person out there?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

jiri-b36968 can you help on this case?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

Table 32.4.12.2 describes bursting between Flexbus and external device depending of port size of the device. So when you have 32-bit data you can transfer them in 4 burst cycles when port size is 8-bit wide.

Transfer between DMA and Flexbus driver is something else. Flexbus driver is NIC slave. DMA is master on NIC. This transfer can be also burst-ed. When you transfer 32 bytes you can transfer them in 4 cycles since interface is 64-bit wide.

But I guess you are talking about burst transfer between Flexbus driver and external device.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Cool, why doesn't it work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have the DMA set up to push many 32 bit double words of data out through a port defined for 32 bit bursts, but we only see one 32 bit double word per access. We are looking for something not setup correct, but have run out of knobs to twiddle.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

please be clear. What does not work Burst during transfer between DMA and Flexbus? Or burst between Flexbus and external device?

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We set up the flexbus for 32 bursts. Then we program the DMA controller to send multiple 32 bit double words to the flexbus address range of interest (the one programmed for bursts). We never see a burst. We see a single 32 bit transfer, but never 4 beats during the same cycle.

If we set the DMA to send a single 32 bit double word, we see a single access normal access (1 clock ALE, 1 clock CS/data, 2 clocks nothing)

if we set the DMA to send 4 32 bit double words, we see 4 single accesses (each access having 1 clock ALE, 1 clock CS/data, and 2 clock of nothing)

If we set the DMA to send 64 32 bit double words, we see 64 single accesses.

We never see the CS last longer than a single clock and the data is always split over a number of single accesses equal to the number of double words sent.

It is critical to our project that we eliminate the some overhead on the flexbus accesses by using burst mode. Thus far, we've never seen a burst access of any kind. Has anyone actually used line mode and seen it work?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

OK so burst between Flexbus and your external device is not working for you. Your setting of FB_CSCR2 is: 0x00000108 which is BSTW=1 bus write enable, AA=1 auto acknowledge enabled, PS=00 32bit size.

Your data are 32 bit and you write to 32 bit wide port size. So bust write is finished in one cycle.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, so what am I doing wrong to not get a burst of 4 32 bit double words? As I understand it, the DMA can be set to transfer 32 or 64 bits of data per transfer, but not 128 that would be needed for 4 32 bit transfers. So, the unconfirmed (and highly doubtful at this point) assumption has been that the DMA is able to throw 32 words at the flexbus fast enough to allow a burst of 4. If the DMA could transfer 128 bits at a time, then it would make sense to try this setting, but how do we get 4 transfers from a 64 bit transfer.

By the way, we did multi beat bursts yesterday, but that was done using an 8 bit port setting (4 beats from 32 bits), and a 16 bit port setting (2 beats from 32 bits) on the chip select. But still no 32. This makes us fear that 4 beats at 32 is really not possible since the DMA cannot move more than 64 at a time.

We are continuing to hack at this issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi John,

yes John, the burst will be used when you transfer 32 bits through 8 bits wide bus (4 beats) or 32 bits through 16 bits wide port size (2 beats), but not for 32 bits through 32 bits wide bus. So it seems that burst between Flexbus and external device works for you.

Anyway you can extend your burst transfer to 16 bytes, but only for 8bits or 16 bits port size (you have set it to 32 bits)

So please change port size to 16 or 8 bits port size and then try your transfer. You can check burst length on FB_TSIZ lines.

/Jiri