- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- T-Series

- :

- Re: T1042 DDR Validation BIST Fails

T1042 DDR Validation BIST Fails

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

T1042 DDR Validation BIST Fails

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

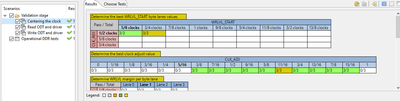

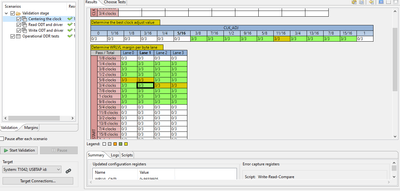

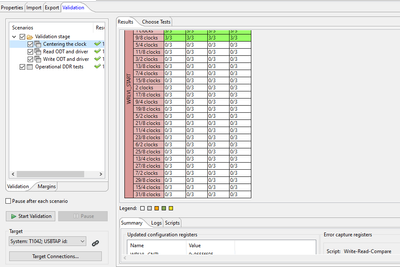

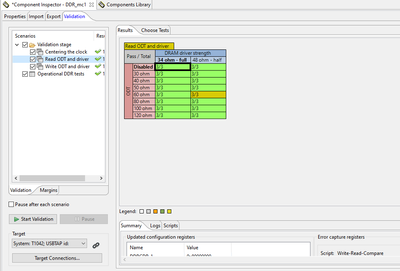

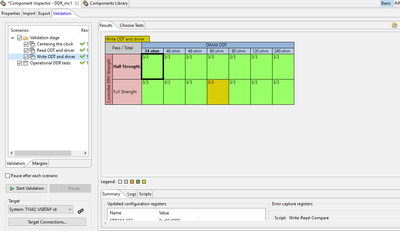

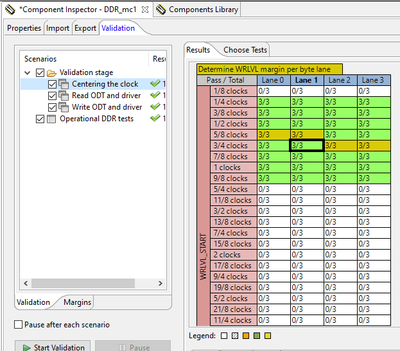

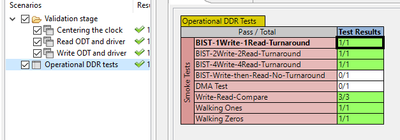

We are working on bring-up of a custom board with T1042NXE7PQB and four discrete DDR4 SDRAMs. When we run Validation using QCVS, the tests pass using the 'Write, Read, Compare' test x3 (default setting) and we get our updated properties from tuning. However, when we go to run the Operational DDR tests, we get failures on BIST-Write-then-Read-No-Turnaround and DMA Test (all others pass).

We also are not able to run from RAM in uBoot, we can load individual files, and our internal DRAM memory tests pass, but when we load uBoot into RAM and then go to execute, what we see in RAM is not what we wrote to it. It seems like this issue would at least be partially related to the BIST-Write-then-Read-No-Turnaround test, but we are not sure

Additional Details:

- DDR4 P/N is MT40A512M16LY-062EAAT_E

- Running at 1600MT/s (800MHz)

- Both test failures (BIST-Write-then-Read-No-Turnaround and DMA) fail with same log message: DDR_MTCR[MT_STAT] = 1, Data miscompare detected during test

- For tests that pass, only 2 of the 4Gb are used. If I try to increase the bus width to the full 64 we get 0x000080 error, Auto Calibration Error

- We followed AN5097 in designing the system and had the schematic reviewed by NXP and layout reviewed by internal DDR experts

- Voltages appear stable during tests, we can do more probing if it's possible there's a glitch or voltage excursion that causes the two test failures

- Logs for the two failed test below

Test Results:

#################### Result for: bist_w_r_no_turnaround_test ###### Run 1 #########################

ERROR: (DDR_MTCR[MT_STAT] = 1 : Data miscompare detected during test)

A data miscompare was detected at address: 0x000000007FFF7FC0

Test failed!

Err. capture registers:

0xE20, 0x01234567 0xE24, 0x89ABCDEF 0xE28, 0xFFFFFFFF 0xE40, 0x00000000

0xE44, 0x00000000 0xE48, 0x0000001D 0xE4C, 0x60FF2001 0xE50, 0x7FFF7FC0

0xE54, 0x00000000 0xE58, 0x00010000

Dump:

0xF00, 0x00000000 0xF04, 0x00000002 0xF08, 0x0000000B 0xF0C, 0x14000C20

0xF10, 0x00000000 0xF14, 0x00000000 0xF18, 0x00000000 0xF1C, 0x00000000

0xF20, 0x00000000 0xF24, 0x18001900 0xF28, 0x18001800 0xF2C, 0x00000000

0xF30, 0x00000000 0xF34, 0x00003000 0xF38, 0x00000000 0xF3C, 0x00000000

0xF40, 0x00000000 0xF44, 0x00000000 0xF48, 0x00000001 0xF4C, 0xD4000000

0xF50, 0x0B000B00 0xF54, 0x0C000C00 0xF58, 0x22002200 0xF5C, 0x24002600

0xF60, 0x1C000000 0xF64, 0x00000000 0xF68, 0x00000000 0xF6C, 0x00000000

0xF70, 0x00000000 0xF74, 0x00000000 0xF78, 0x00000000 0xF7C, 0x00000000

0xF80, 0x00000000 0xF84, 0x00000000 0xF88, 0x00000000 0xF8C, 0x00000000

0xF90, 0x00000000 0xF94, 0x00000000 0xF98, 0x00000000 0xF9C, 0x13001300

0xFA0, 0x14001400 0xFA4, 0x00000000 0xFA8, 0x00000000 0xFAC, 0x00000000

0xFB0, 0x00000003 0xFB4, 0x0F0E0D10 0xFB8, 0x0E0E0D0D 0xFBC, 0x0F0E0E10

0xFC0, 0x0F0F0E0D 0xFC4, 0x0F0E0E11 0xFC8, 0x0E0F0E0E 0xFCC, 0x0F0F0E10

0xFD0, 0x0E0E0F0E 0xFD4, 0x0F0F0F0F 0xFD8, 0x0F0F0F0F 0xFDC, 0x0F0F0F0F

0xFE0, 0x0F0F0F0F 0xFE4, 0x0F0F0F0F 0xFE8, 0x0F0F0F0F 0xFEC, 0x0F0F0F0F

0xFF0, 0x0F0F0F0F 0xFF4, 0x0F0F0F0F 0xFF8, 0x0F0F0F0F 0xFFC, 0x00000000

Data:

0x00000000

Target system was initialized 1 times and it took 3.437000 seconds.

Target system effective test execution took 1.150000 seconds.

#################### Result for: dma_test ###### Run 1 ############################################

Test failed!

Err. capture registers:

0xE20, 0x00000000 0xE24, 0x00000000 0xE28, 0x00000000 0xE40, 0x00000000

0xE44, 0x00000000 0xE48, 0x0000001D 0xE4C, 0x00000000 0xE50, 0x00000000

0xE54, 0x00000000 0xE58, 0x00010000

Dump:

0xF00, 0x00000000 0xF04, 0x00000002 0xF08, 0x0000000B 0xF0C, 0x14000C20

0xF10, 0x00000000 0xF14, 0x00000000 0xF18, 0x00000000 0xF1C, 0x00000000

0xF20, 0x00000000 0xF24, 0x18001800 0xF28, 0x18001800 0xF2C, 0x00000000

0xF30, 0x00000000 0xF34, 0x00003000 0xF38, 0x00000000 0xF3C, 0x00000000

0xF40, 0x00000000 0xF44, 0x00000000 0xF48, 0x00000001 0xF4C, 0xD4000000

0xF50, 0x0B000B00 0xF54, 0x0C000C00 0xF58, 0x22002200 0xF5C, 0x24002600

0xF60, 0x1C000000 0xF64, 0x00000000 0xF68, 0x00000000 0xF6C, 0x00000000

0xF70, 0x00000000 0xF74, 0x00000000 0xF78, 0x00000000 0xF7C, 0x00000000

0xF80, 0x00000000 0xF84, 0x00000000 0xF88, 0x00000000 0xF8C, 0x00000000

0xF90, 0x00000000 0xF94, 0x00000000 0xF98, 0x00000000 0xF9C, 0x13001300

0xFA0, 0x14001400 0xFA4, 0x00000000 0xFA8, 0x00000000 0xFAC, 0x00000000

0xFB0, 0x00000003 0xFB4, 0x0F0E0D10 0xFB8, 0x0E0E0D0D 0xFBC, 0x0F0E0E10

0xFC0, 0x0F0F0E0D 0xFC4, 0x0F0E0D11 0xFC8, 0x0D0F0E0E 0xFCC, 0x0F0F0E11

0xFD0, 0x0F0E0F0E 0xFD4, 0x0F0F0F0F 0xFD8, 0x0F0F0F0F 0xFDC, 0x0F0F0F0F

0xFE0, 0x0F0F0F0F 0xFE4, 0x0F0F0F0F 0xFE8, 0x0F0F0F0F 0xFEC, 0x0F0F0F0F

0xFF0, 0x0F0F0F0F 0xFF4, 0x0F0F0F0F 0xFF8, 0x0F0F0F0F 0xFFC, 0x00000000

Data:

0x0001B000 0x000000AA 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000 0x00000000

Target system was initialized 1 times and it took 4.349000 seconds.

Target system effective test execution took 0.015000 seconds.

Let me know if more details are needed to help troubleshoot

Thank you,

A. Kowalczyk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We managed to resolve it, but aren't entirely sure why

We changed the DDR setting 'Partial Array Self Refresh' to 'HalfArray (BA[2:0]=000, 001, 010 & 011). After this it came up and we have all tests passing, and plenty of margin

We still only have 2GB of the 4GB up and running, that might be a later post for a different issue, but for now 2GB is enough to start development.

Thank you,

A. Kowalczyk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Would you please regenerate DDR configuration code from Project->Build All in QCVS project and send InitDdrRegisters_1.c to me to do more investigation?

Would you please also send your modified u-boot source code related with DDR to me?