- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: What circumstances will cause the adc self-test algorithm return failure in S32K3xx

What circumstances will cause the adc self-test algorithm return failure in S32K3xx

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

What circumstances will cause the adc self-test algorithm return failure in S32K3xx

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am testing the ADC Self Test function on the S32K324 chip.

In order to test that the ADC can be detected when an error occurs, the ADC Reference high voltage is artificially set to zero on the hardware circuit to simulate ADC failure, but the ADC Self-Test algorithm still does not report an error (I use the AUTOSAR standard interface selftest API)

I confirmed that I removed the corresponding circuit because the ADC calibration did not pass and will enter dead loop.

I wonder what will cause the self test function failed and how I can test it.

B.R.

Guo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So in fact, in the autosar framework, the selftest api cannot detect whether the adc circuit outside the chip is working properly, but only whether the adc is working properly inside the chip. I think I got it. Thanks a lot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't understand you whether you are setting VREFH to low during self-test or only during calibration. Anyway ADC self-test algorithm S tests reference voltage, so it should lead failed self-test results.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I removed the VREFH circuit on the physical circuit. That means there is no input at this pin. Wheather that the VREFH needs to be grounded to make the self test error? I just simply disconnected VREFH pin. At the following image, I would like to show you how I start the self test after set the adc register to the correct value, and I hope it is helpful for you to find out why the self-test didn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is quite interesting, but it is possible that if you have VREFH unconnected, it may be evaluated as valid range due to induced voltage from other pins (not being completely sure). I would recommend you to try to terminate to GND.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Nope it still not work

I ground VREFH as you asked but self-test API still returns pass

To make the problem clearer, I would like to confirm to you whether I changed the circuit correctly: I ground the 16th pin of the MCU chip, other circuits do not change, I am using the S32K324 chip (S32K324 has 172 pins)

I would also like to know which error register would set 1 under “normal” circumstances?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I should fail is S0 as it converts band gap level according ADC reference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I still don't understand why self-test didn't work. After I turned on all the registers related to self-test as required by the chip reference manual, I could observe the repeated changes from 0 to 1 in the SELF_TEST_S (18bit) from MSR register by leaving the register in this state, which proves that selftest has started normally.

But the STSR1 register only has bit23 turned to 1(value: 0x00800000) which confirmed self-test end of conversion, I don't know after normal selftest ends, only bit23 in STSR1 will set 1 or the watch dog register should set to complete.

But according to your statement, bit11 in the STSR1 register, the Error Algorithm S step 0, will be set to 1 first?

I still need your help with this problem,I would like you to give me some ideas, or should I provide more clues?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have obtained an answer from SW developer, I am forwarding as it is:

"

The reason for the self-test executed successfully with VREFH tied to GND is that, the RTD Adc_Sar_Ip_SelfTest() only executes the self-test process but doesn't check the conversion data of each self-test algorithm step(such as S1), it means the error flag(such as STSR1[ERR_S1]) won't be set although the VREFH was tied to GND.

And the ADC also provides monitoring options for conversion data generated by self-test algorithms, for details, you could refer to "58.3.16.2.4 Self-test analog watchdog" in S32K3 RM.

To help the customer to complete this test, we need to enable the self-test analog watchdog and configure its low threshold value(15bit) which related to VERFH(self-test algorithm S1 and S2).

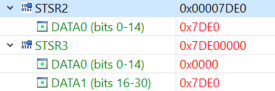

For example, I modified the RTD Adc_Sar_Ip_SelfTest() function by adding below code, then the self-test was failed because the conversion data(0x7DE0) of S1|S2 was less than the low threshold value which I configured(0x7FFF) before.

You could also find the conversion result when an error in step 1|2 of algorithm S has occurred as below.

"