- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K344 ADC: HAS_ADC_INTERLEAVE problem

S32K344 ADC: HAS_ADC_INTERLEAVE problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP engineer, Hello.

I am debugging the ADC function of S32K344_EVB, development environment: EBtresos 28.2.0+S32DS

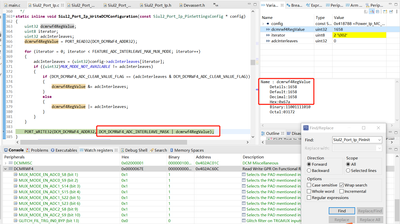

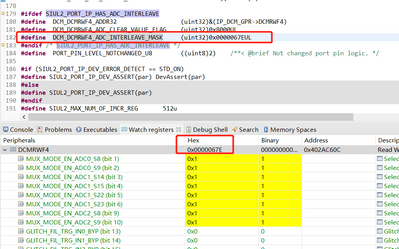

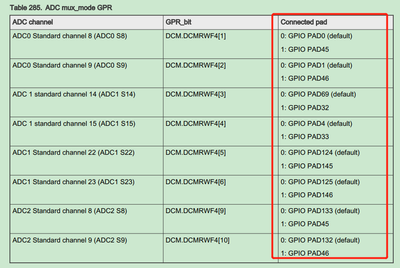

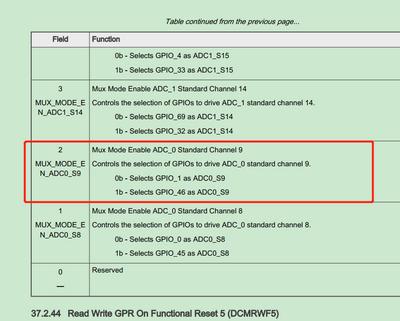

I want to use PIN_PTA1 as ADC0_S9 function, but I found that the acquisition ADC failed. Then I found that DCM.DCMRWF4[2] is set to 1 by MCAL program by default.

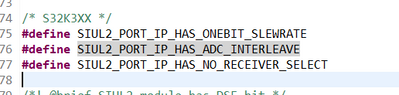

MCAL static code library: SIUL2_PORT_IP_HAS_ADC_INTERLEAVE is defined by default.

The logic in the static code:

PORT_WRITE32(DCM_DCMRWF4_ADDR32, DCM_DCMRWF4_ADC_INTERLEAVE_MASK | dcmrwf4RegValue);

0x0000067E | 0x0000067A = 0x0000067E ? (DCMRWF4.MUX_MODE_EN_ADC0_S9 = 1(is PTB14))

will enable all ADC INTERLEAVE in DCMRWF4 to 1.

What is the purpose of this logic, as the manual should all be set to 0 by default.

Shouldn't this logic be changed to something like the following:

PORT_WRITE32(DCM_DCMRWF4_ADDR32, DCM_DCMRWF4_ADC_INTERLEAVE_MASK & dcmrwf4RegValue);

0x0000067E & 0x0000067A = 0x0000067A (DCMRWF4.MUX_MODE_EN_ADC0_S9 = 0(is PTA1))

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Du_0224,

Thank you for the report.

And sorry for the inconvenience we bring you!

The problem of Siul2_Port_Ip_WriteDCMConfiguration has been reported to the RTD team before, but the fix version has not been released yet, so the customer needs to manually modify it temporarily.

You can see this similar discussion: S32K3_ADC_Channcal_configure_problem

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Du_0224,

Thank you for the report.

And sorry for the inconvenience we bring you!

The problem of Siul2_Port_Ip_WriteDCMConfiguration has been reported to the RTD team before, but the fix version has not been released yet, so the customer needs to manually modify it temporarily.

You can see this similar discussion: S32K3_ADC_Channcal_configure_problem

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Robin,

Thank you for your reply.

I have been able to use ADC properly by changing RTD_LLD manually.

I will follow up with RTD updates.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

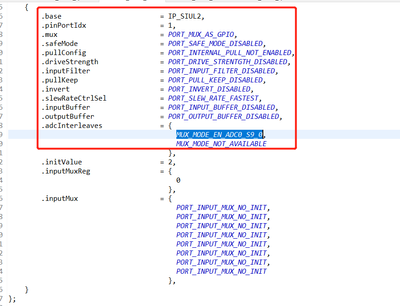

Attached is the PIN_PTA1 pin configuration for MCAL.