- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: MCU sleep mode

MCU sleep mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MCU sleep mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm developing a baremetal application and I'm thinking to put the mcu in sleep mode when idle using the WFI instruction.

As far as I understand, when calling WFI with mcu in RUN mode and DEEPSLEEP register set to 0, the mcu just goes to sleep (no STOP1 or STOP2 mode involved), is it correct?

I'm trying to figure out what's the behaviour of other peripherals when the mcu is in sleep: is there any operation that needs to be terminated before going to sleep?

For example, is it safe to call a WFI when there is an eeeprom write running at the same time?

Thanks and regards,

Riccardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, thanks for the answer.

I read the paragraphs, but I'm still not sure what to do.

Let me explain what i would like to do in my application. I want to measure the time the CPU remains idle, so my idea was to put the CPU (only the core, every other peripheral shall remain running) in sleep when there is nothing to do and be ready to resume as soon as an interrupt fires. In this way I could read the value of a timer (LPIT or FlexTimer) just before the wfi instruction and immediately after to get an estimate of the idle time. I'm not interested in any powersaving feature.

From what i read in the ARM documentation I should use the ARM sleep mode, but in the S32K reference manual there is no information about that. On the contrary it describes the STOP2 mode which also seems to be a good candidate for the job (core clock stopped, but almost everything else enabled).

What would be the best option for my pourposes?

Thanks,

Riccardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

For your purpose, the best option is, as you said, STOP2 because the bus clock remains active, but FTM (FlexTimer module) is OFF in the STOP modes.

The LPIT has full functionality in the STOP2, so, you can use it. However, the timers have some disadvantages.

The LPIT you can read only in the interrupt. The LPTM is only 16-bit and RTC is accurate when you have an external clock.

So, it depends on your application.

Also, I would like to recommend you to look at Table 38-4. Module operation in available power modes to see each module functionality in this mode.

Also, you can look at AN5425. There the STOP mode entry sequence can be seen.

https://www.nxp.com/docs/en/application-note/AN5425.pdf

AN5425SW

https://www.nxp.com/webapp/Download?colCode=AN5425SW&docLang=en

I hope it helps.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, Thanks for the answer.

No, sorry, I noticed that the FTM is required in my application and can't be stopped, so STOP2 is not applicable.

However from the application note AN5425, I understand that ARM Sleep mode is indeed available on the S32K (paragraph 2.1), but the document does not say what are the effects on other peripherals. Are they affected if I put the Core in Sleep?

I would like a clarification on that, please.

Thanks for the support,

Riccardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Riccardo,

The sleep mode which you are looking for is called "Wait mode" in the RM.

"Wait mode is not supported in this device. See Table 38-4. Module operation in available power modes for

details on available power modes."

Unfortunately, the S32K1xx device does not support WAIT, VLPW and low

leakage modes

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

If so then application note is incorrect, see paragraph 2.1

even if it doesn't explain much more. I think the reference manual is not very clear about this.

Also where in the manual can I find a definition of Wait mode and its association with ARM sleep?

Thanks,

Riccardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Riccardo,

It isn't very clear as you said. I will report to the apps team that "sleep mode" should be clearly described in the RM.

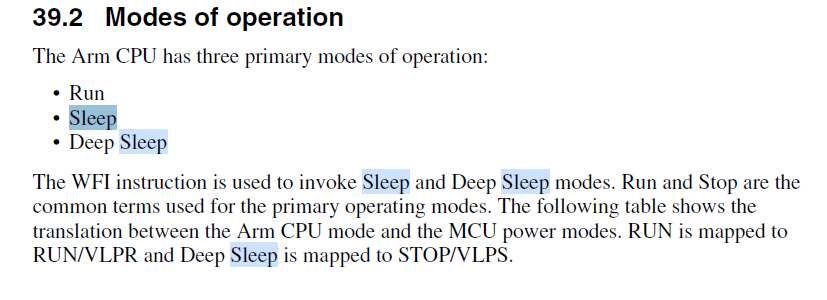

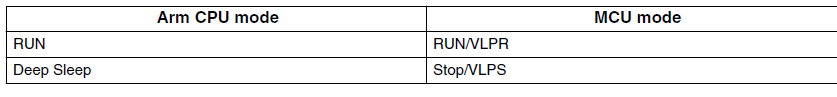

We can see the translation between ARM CPU mode and MCU power modes in section 39.2 Modes of operation. So, sleep mode is not there.

Also, the filed which represent sleep/wait power mode on the S32K1xx is empty in the AN5425 in Figure 1. Power modes comparison.

Best regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

thanks very much for the answer.

I hoped for an easier way to do what I had in mind. I need to figure out how to make the STOP 2 work in my case then.

Thanks again,

Riccardo

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Riccardo,

At first, I would like to mention a few points from RM rev. 11.

Also, please, look at the section 38.8 Module operation in available power modes, 39.2 Modes of operation and Table 39-1. Power modes

Deep Sleep is mapped to STOP/VLPS.

39.4.2.1 VLPS/Stop mode entry sequence

Entry into a low-power stop mode (Stop, VLPS) is initiated by a CPU executing the WFI

instruction. After the instruction is executed, the following sequence occurs:...

27.4.4 VLPR/VLPS mode entry

When entering VLPR/VLPS mode, the system clock should be SIRC. The FIRC, SOSC,

and SPLL must be disabled by software in RUN mode before making any mode

transition. Ensure that CMU is gated by its PCC.CGC before entering STOP/VLPS/CPO

mode.

PMC_REGSC[BIASEN] must be set to 1 when using VLP* modes.

Best regards,

Diana