- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Lpuart Baudrate is twice the specified value (S32K358, RTD 3.0.0)

Lpuart Baudrate is twice the specified value (S32K358, RTD 3.0.0)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm having an issue with the baudrate of the lpuart uart.

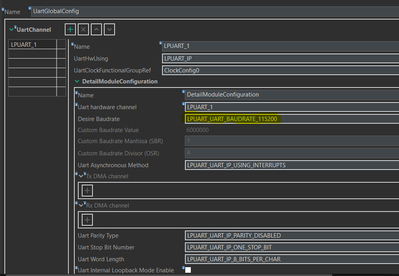

I took the example "LpuartFlexio_Uart_Ip_Example_S32K358" and removed the flexio part, so that the messages are just sent via the lpuart uart driver (LPUART1). Baudrate is set to 115200.

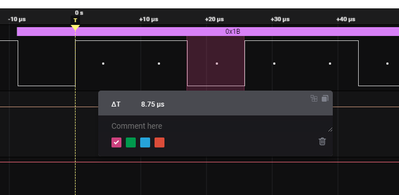

I flashed it on the BMU of the Reference Design and connected it via the USB-TTL Cable to my laptop. While debugging/running I only see the messages in the serial terminal if I set its (=puttys) Baudrate to double the value specified in S32DS (=230400). I also read out the signal via oscillioscope an calculated the baudrate from there, which was also something around 230400 (and not the specified 115200).

So why is the baudrate of the uart twice the value I set?

Kind Regards,

Andio

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

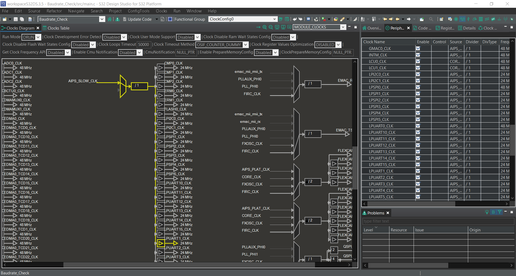

I just checked this morning and i think it's a bug from DS tool when the clock source display isn't correct.

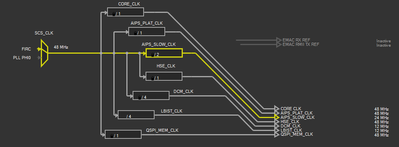

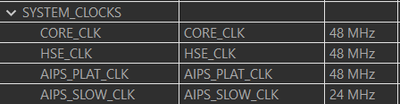

In RM, the clock source for K358 with UART1 is PLAT_CLK. So, the actual clock will be 48M and the issue happens.

I tried to reduce the PLAT_CLK to 24M and then the baud run correctly with 115200.

So i will raise this bug for fixing.

Please consider to change to PLAT_CLK with 24M for testing.

Thank you so much,

Nam.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I just checked this morning and i think it's a bug from DS tool when the clock source display isn't correct.

In RM, the clock source for K358 with UART1 is PLAT_CLK. So, the actual clock will be 48M and the issue happens.

I tried to reduce the PLAT_CLK to 24M and then the baud run correctly with 115200.

So i will raise this bug for fixing.

Please consider to change to PLAT_CLK with 24M for testing.

Thank you so much,

Nam.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andio,

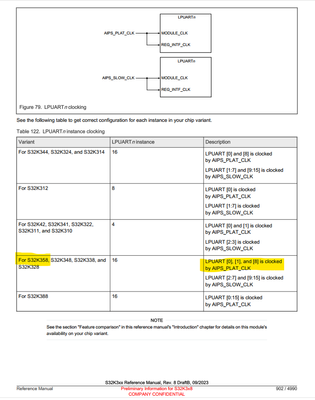

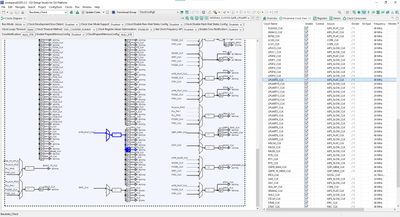

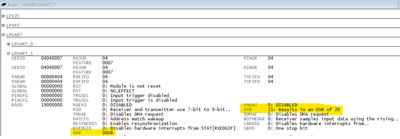

The clock of uart0 is configured in this table

As UART0, the clock supply have to be AIPS_PLAT_CLK

You can change the value of it, but you can't change to another source.

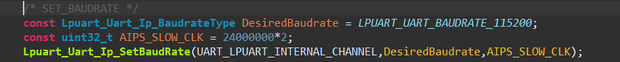

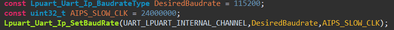

When you fetch directly value 24M Hz into the function Lpuart_Uart_Ip_SetBaudRate

The calculated OSR and SBR register will be saved for 24M valuation.

But when run time, the actual clock source is 48M which cause double of UART baudrate.

Please help me to reconfigure the PLAT_CLK to 24M if you still want to fetch the input of Lpuart_Uart_Ip_SetBaudRate as 24M, or change it to 48M as you've already done.

Sorry for this lately reply, please let me know if you have further questions.

Thank you,

Nam.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @NamLe ,

thank you for the reply.

I understand your point. However I'm using LPUART1 and not LPUART0.

Unlike LPUART0, LPUART1 uses AIPS_SLOW_CLK as clock supply, which is 24 MHz.

So I still don't get why the baudrate only fits when I use 48 MHz in the SetBaudrate function.

Do you have an idea why that may be the case?

Kind Regards,

Andio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @danielmartynek,

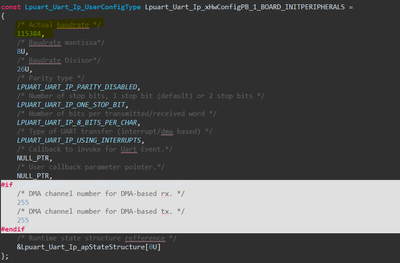

I developed a workaround in which I manually set the Baudrate of the LPUART with a doubled value of the actual Clockfrequency, so 2*24 = 48 [MHz]:

This actually sets the baudrate to 115200, which means i can now see the text in a serial terminal with the settings of "baudrate = 115200".

Additionally the return value of the function "Lpuart_Uart_Ip_GetBaudRate" in regards to LPUART1 is 115384.

So only now the baudrate behaves like expected.

Apparently for some reason only half of the input frequency is used to set the Baudrate.

Do you know why that might be happening?

Kind Regards,

Andio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andio,

That's interesting.

So i checked your project and run debugging, i saw the OSR and SBR were set as correct value as 25 and 8, which calculated for baudrate 115200 as desired value.

The UART1 clock is correct and it supposes to work normally.

Evenwhen fetch input with 48M, the registers value calculation are also correct.

Can you help me try these cases:

- Comment out the function set baudrate. I saw the registers are already deployed after Init function

- Try with 9600 baud.

I will check more in the next week.

Thank you,

Nam.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you for checking the project.

Commenting out the function does not change anything. (The only reason I called that function is to check if it would fix the issue.)

Sadly the same issue is also present with 9600 baud.

Kind Regards,

Andio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Again.

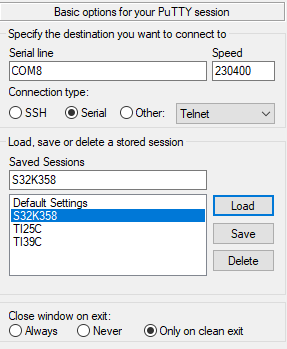

So I'm still having this issue and I couldn't find a fix for it yet. I created a simple project that initializes LPUART1 and prints out the baudrate via serial terminal called Baudrate_Check.

-Baudrate_Check project prints ("actual") baudrate of LPUART1: 115384

-Baudrate that has to be set in the serial terminal using putty (see "speed" in image) is 230400

Things i tried that did not fix it:

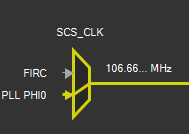

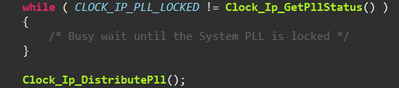

-Changing SCS_CLK source from FIRC to PLL

-Setting the baudrate in code

Sadly I'm all out of ideas for now.

I attached the Baudrate_Check project which is also based on the example "LpuartFlexio_Uart_Ip_Example_S32K358".

Also I didn't mention I'm currently using a PE Micro USB-ML-Universal debug probe for testing the code (GDB PEMicro Interface Debugging). Maybe there could be an issue with the debug configs?

Kind Regards,

Andio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @Andio,

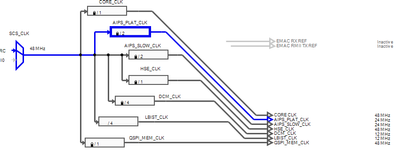

What is the system clock configuration?

Have you modified this in any way?

Thank you,

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Not sure where exactly the system clock configuration is, but I have not modified any clock configurations.

Maybe these pictures are important?:

Kind Regards,

Andio