- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello All,

Recently, I was debugging the issue of FTM triggering ADC sampling, using FTM3 to trigger ADC1 and PDB1. The current problem is that there is an output of FTM3, but neither PDB1 nor ADC1 is triggered.

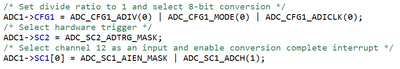

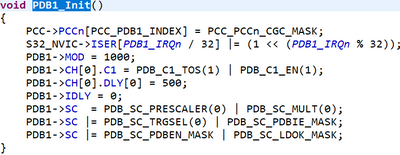

The following are my configuration items:

And Where is the configuration problem or missing configuration items?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

try to refer to simple S32DS "S32K144_Project_PDB" example. It configures PDB for continuous mode SW triggered, but you can test if ADC interrupt is correctly entered with configured period.

Or share your code, so we can test it.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

you should also route FTM trigger (init_trig or ext_trig) into PDB1 input using TRGMUX. Use

TRGMUX->TRGMUXn[TRGMUX_PDB1_INDEX] |= TRGMUX_TRGMUXn_SEL0(28); // use FTM3_INIT_TRIG as PDB1 HW trigger

FTM output trigger should be also enable within FTM External Trigger (EXTTRIG) register.

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hello PetrS,

It has been able to trigger the sampling interrupt of ADC, but the period of entering the interrupt is different from what I expected, which is much smaller than the expected period

/* SW=3, TRGMUX initialization to route FTM Init trigger signal into PDB0 trigger input */

void TRGMUX_Init()

{

//PCC->PCCn[PCC_TRGMUX_INDEX] = PCC_PCCn_CGC_MASK; // Enable clock for TRGMUX module

TRGMUX->TRGMUXn[TRGMUX_PDB1_INDEX] = TRGMUX_TRGMUXn_SEL0(0x1D); // Set FTM3 as a trigger source for PDB0

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

what is an expected period and the one you have?

Do you read ADC Data result register within ADC interrupt so COCO flag is cleared?

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Morning,

The interrupt cycle of my PDB is correct, which is 80kHz. Theoretically, my ADC interrupt cycle should also be 80kHZ, but according to the current test data, the ADC interrupt cycle is 400kHZ. In addition, I read the data register in the ADC interrupt

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

try to refer to simple S32DS "S32K144_Project_PDB" example. It configures PDB for continuous mode SW triggered, but you can test if ADC interrupt is correctly entered with configured period.

Or share your code, so we can test it.

BR, Petr