- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- 软件论坛

- :

- S32 Design Studio

- :

- Re: LPIT0 Ch1 Interrupt.

LPIT0 Ch1 Interrupt.

Hello,

I need to configure LPIT0_CH1 in S32K144-QN57U, after some attempts I was not able to make it work, can anyone help me to review next configuration :

Thank you, Antonio.

#define LPIT0_BASE (0x40037000u)

#define LPIT0 ((LPIT_Type *)LPIT0_BASE)

void NVIC_init_IRQs (void) {

S32_NVIC->ICPR[1] = 1 << (49 % 32);

S32_NVIC->ISER[1] = 1 << (49 % 32);

S32_NVIC->IP[49] = 0xF0;

}

void LPIT0_init (void) {

PCC->PCCn[PCC_LPIT_INDEX] = PCC_PCCn_PCS(6);

PCC->PCCn[PCC_LPIT_INDEX] |= PCC_PCCn_CGC_MASK;

LPIT0->MCR = 0x00000001;

LPIT0->MIER = 0x00000010;

LPIT0->TMR[1].TVAL = 10000000;

LPIT0->TMR[1].TCTRL = 0x10000001;

}

void LPIT0_Ch1_IRQHandler (void) {

LPIT0->MSR |= LPIT_MSR_TIF1_MASK; /* Clear LPIT1 timer flag 0 */

PTD->PTOR |= 1<<LED_GREEN; /* Toggle output on port */

}

已解决! 转到解答。

Hi Antonio,

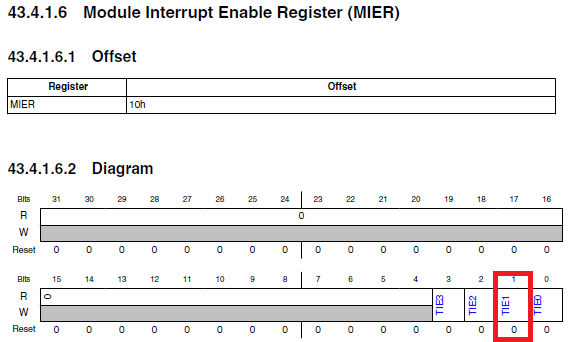

From the code snippet it seems the problem seems to be caused by wrong PIT interrupt enable register (MIER):

void LPIT0_init (void) {

PCC->PCCn[PCC_LPIT_INDEX] = PCC_PCCn_PCS(6);

PCC->PCCn[PCC_LPIT_INDEX] |= PCC_PCCn_CGC_MASK;

LPIT0->MCR = 0x00000001;

LPIT0->MIER = 0x00000002; // channel 1 enable (TIE1)

LPIT0->TMR[1].TVAL = 10000000;

LPIT0->TMR[1].TCTRL = 0x10000001;

}

Hope it helps,

Stan

Hi Antonio,

From the code snippet it seems the problem seems to be caused by wrong PIT interrupt enable register (MIER):

void LPIT0_init (void) {

PCC->PCCn[PCC_LPIT_INDEX] = PCC_PCCn_PCS(6);

PCC->PCCn[PCC_LPIT_INDEX] |= PCC_PCCn_CGC_MASK;

LPIT0->MCR = 0x00000001;

LPIT0->MIER = 0x00000002; // channel 1 enable (TIE1)

LPIT0->TMR[1].TVAL = 10000000;

LPIT0->TMR[1].TCTRL = 0x10000001;

}

Hope it helps,

Stan