- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- Re: How to understand the PLL FM?

How to understand the PLL FM?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to understand the PLL FM?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

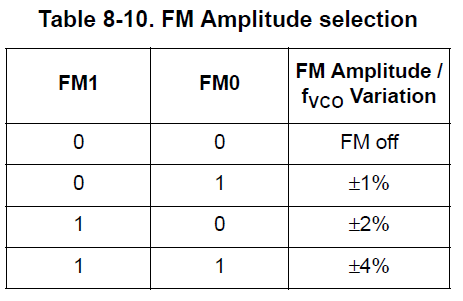

S12ZVM Reference Manual says "FM1 and FM0 enable frequency modulation on the VCOCLK. This

is to reduce noise emission". How to understand that ?

In my understand, for example, PLL output ( VCOCLK ) set as 10MHz and FM set as '01', actual VCOCLK is 10±0.1%. Is that correct? How about FM off?

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Diana,

Thanks for your reply. I have one more question about that.

How do VCOCLK change if FM is enabled? In some rules, such as sine wave, or random.

Best Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The frequency is in the triangle waveform.

I would like to at the note that if you don’t have a problem with EMC emission, rather don't use frequency modulation.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello dianabatrlova

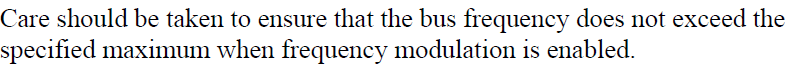

Actually, I have problems with EMC now. I saw below note in the manual. Does it mean that if I enable PM as '11', 4% variation, then bus clock must set to less than 46 MHz, considering that S12ZVM maximum bus clock is 50 MHz? If exceed the maximum clock, what will happen?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

At first, I would like to apologize for the delay with my response.

The bus clock frequency range of S12ZVM is 1MHz - 50 MHz. This range should not be exceeded.

For example, if you are using 46 MHz bus clock freq. and +-4% FM you should consider that the bus clock frequency will be 44.16 MHz - 47.84 MHz. So, in this case, we are in the specified range.

If the maximum frequency of the bus clock is exceeded we cannot guarantee the correct behavior of the device.

There is a description in NVM Electrical Parameters in the RM rev. 2.11:

"The time base for all NVM program or erase operations is derived from the bus clock using the FCLKDIV

register. The frequency of this derived clock must be set within the limits specified as fNVMOP. The NVM

module does not have any means to monitor the frequency and will not prevent program or erase operation

at frequencies above or below the specified minimum."

I hope it helps you.

Best Regards,

Diana

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The frequency modulation PLL function will reduce the noise amplitude because it spreads this over a greater frequency range. If FM function is enabled it must be taken that maximum bus frequency is not exceeded.

- If frequency modulation is off (by default) IPLL block, try hold VCOCLK on one stable frequency.

- Additional frequency modulation of VCOCLK spreads frequency spectrum around VCOCLK.

So, if modulation is set as ’01’ the VCOCLK variation will be within +/- 1 %.

I hope it helps you.

Best Regards,

Diana