- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- How to move or stop arch_timer interrupt?

How to move or stop arch_timer interrupt?

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to move or stop arch_timer interrupt?

04-02-2020

05:43 AM

2,594 Views

gyosunshim

Contributor III

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

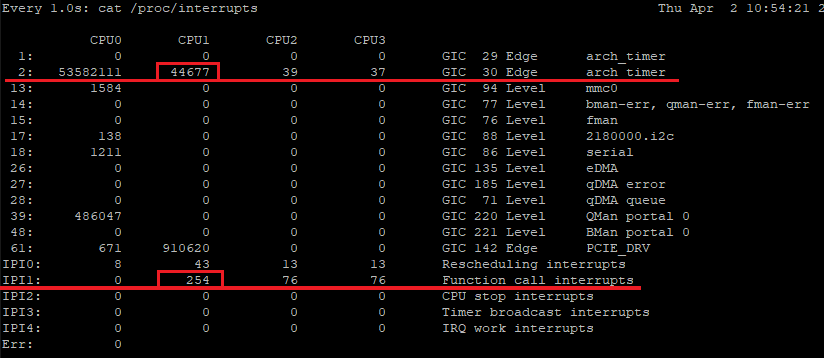

I am using QorIQ SDK version 2.0-1703 for LS1046A CPU.

We have used a number of methods to optimize jitter to reach our desired level.

Core 1-3 is isolated.

Is there a way to move or disable arch_timer to core 0 during interrupt?

The same goes for IPI1.

Thanks,

Best regards.

Gyosun.

2 Replies

04-02-2020

11:42 PM

2,462 Views

NXP TechSupport

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You could disable arch_timer in dts file.

timer {

compatible = "arm,armv8-timer";

interrupts = <GIC_PPI 13 (GIC_CPU_MASK_RAW(0xf) |

IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 14 (GIC_CPU_MASK_RAW(0xf) |

IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 11 (GIC_CPU_MASK_RAW(0xf) |

IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 10 (GIC_CPU_MASK_RAW(0xf) |

IRQ_TYPE_LEVEL_LOW)>;

status = "disabled";

};

12-07-2022

12:55 AM

1,225 Views

ekim

Contributor I

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Is there any side-effects when arch_timer disabled? After disabled it, will use arch_mem_timer to sync all of cores?