- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- Identification and Security

- i.MX Processors

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- CodeWarrior

- Wireless Connectivity

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- Home

- :

- Software Forums

- :

- Processor Expert Software

- :

- Re: LS1028A 4port SGMII VSC8504

LS1028A 4port SGMII VSC8504

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP experts.

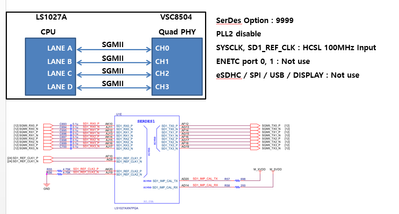

I developing the custom board based on ls1028ardb board

and attached vsc8504 phy to ls1028a cpu.

the vsc8504 phy uboot driver is added on uboot/drivers/net/phy/vitesse.c

<figure1> is block diagram, how to connect vsc8504 to cpu

<figure 1>

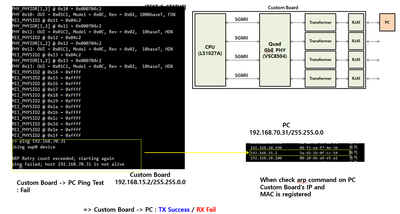

and ping test on uboot,

<figure2> is test configuration

Runnnig Wireshark on PC Side.

the custom board arp request packet is captured by wireshark

and pc send reply packet, but custom board can't receive the reply

but sometimes can receive about once in a hundred

Please refer and feedback.

what i should do?

===================== RCW ==========================

CLK_OUT_PMUX=0

63 ASLEEP_PMUX=0

64 RESET_REQ_PMUX=0

65 IIC1_PMUX=0

66 HOST_AGT_PEX1=0

67 HOST_AGT_PEX2=0

68 GP_INFO=0

69 EC1_SAI4_5_PMUX=0x1

70 EC1_SAI3_6_PMUX=0x1

71 USB_DRVVBUS_PMUX=1

72 USB_PWRFAULT_PMUX=1

73 USB3_CLK_FSEL=0x27

74 ENETC_RCW=0x3

75 SPI3_PMUX=0x1

76 GTX_CLK125_PMUX=1

77 SRDS_PLL_PD_PLL1=0

78 SRDS_PLL_PD_PLL2=1

79 /*

80 *SRDS_PRTCL_S1_L0=0x9

81 *SRDS_PRTCL_S1_L1=0x9

82 *SRDS_PRTCL_S1_L2=0x9

83 *SRDS_PRTCL_S1_L3=0x9

84 */

85 SRDS_PRTCL_S1_L0=9

86 SRDS_PRTCL_S1_L1=9

87 SRDS_PRTCL_S1_L2=9

88 SRDS_PRTCL_S1_L3=9

89 SRDS_PLL_REF_CLK_SEL_S1=0

90 SRDS_S1_REFCLK_SRC_SEL=0

===================== DTS ==========================

150 &mscc_felix_port0 {

151 label = "swp0";

152 phy-handle = <&sw_phy0>;

153 phy-mode = "sgmii";

154 status = "okay";

155 managed = "in-band-status";

156 };

157

158 &mscc_felix_port1 {

159 label = "swp1";

160 phy-handle = <&sw_phy1>;

161 phy-mode = "sgmii";

162 status = "okay";

163 managed = "in-band-status";

164 };

165

166 &mscc_felix_port2 {

167 label = "swp2";

168 phy-handle = <&sw_phy2>;

169 phy-mode = "sgmii";

170 status = "okay";

171 managed = "in-band-status";

172 };

173

174 &mscc_felix_port3 {

175 label = "swp3";

176 phy-handle = <&sw_phy3>;

177 phy-mode = "sgmii";

178 status = "okay";

179 managed = "in-band-status";

180 };

181

182 &mscc_felix_port4 {

183 ethernet = <&enetc2>;

184 status = "okay";

185 };

186

187 &mdio0 {

188 status = "okay";

189 /*

190 rdb_phy0: phy0 {

191 reg = <0>;

192 };

193 */

194 /* VSC8504 QSGMII PHY */

195 sw_phy0: phy@10 {

196 reg = <0x10>;

197 };

198 sw_phy1: phy@11 {

199 reg = <0x11>;

200 };

201

202 sw_phy2: phy@12 {

203 reg = <0x12>;

204 };

205

206 sw_phy3: phy@13 {

207 reg = <0x13>;

208 };

209 };

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

it's solved

thanks