- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- QorIQ Processing Platforms

- :

- P-Series

- :

- Re: P2041 DDR3 Auto Calibration Error / DDR_ERR_DETECT[ACE]

P2041 DDR3 Auto Calibration Error / DDR_ERR_DETECT[ACE]

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a P2041 based custom board with 72bit memory interface. This design already verified and has been used for years. My question is about DDR_ERR_DETECT register ACE bit. This bit is related with auto calibration. What is the content of auto calibration process? Does it contains initialization steps write/read leveling and more? I have ACE problem at two my boards. I know that there is a single bit error on DQ (i can detect by the help of DDR controller error registers) due to soldering or things related with production not design. Can one of the problematic dq (error on this signal randomly occurs) can cause ACE error? I think ACE is related with this dq but i wanted to be sure about it. For that reason, i need to learn content of ACE. Also, is it possible to see at which calibration step i got error?

Edit: I observed that boards can continue to work even if they have ACE error (if you disable ACE interrupt). How is it possible or way to learn which step we have errors.

Thanks for replies.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

please see attached. this is the DDR3/3L initialization flow.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ACE = 1 means the DDR initialization failed.

it is not clear that customer has ACE=1 only on two boards in their production line that has been working for years?

can you quantify how many boards are passing and how many boards fail with ACE=1?

for sure a manufacturing issue (cold solder, or other HW issues) can cause a board to have ACE. if we bypass the ACE the boards may work but it may fail for in correct or no initialization.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Moreover,

Is auto calibration performed at start up only or is it a periodically performed operation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi again,

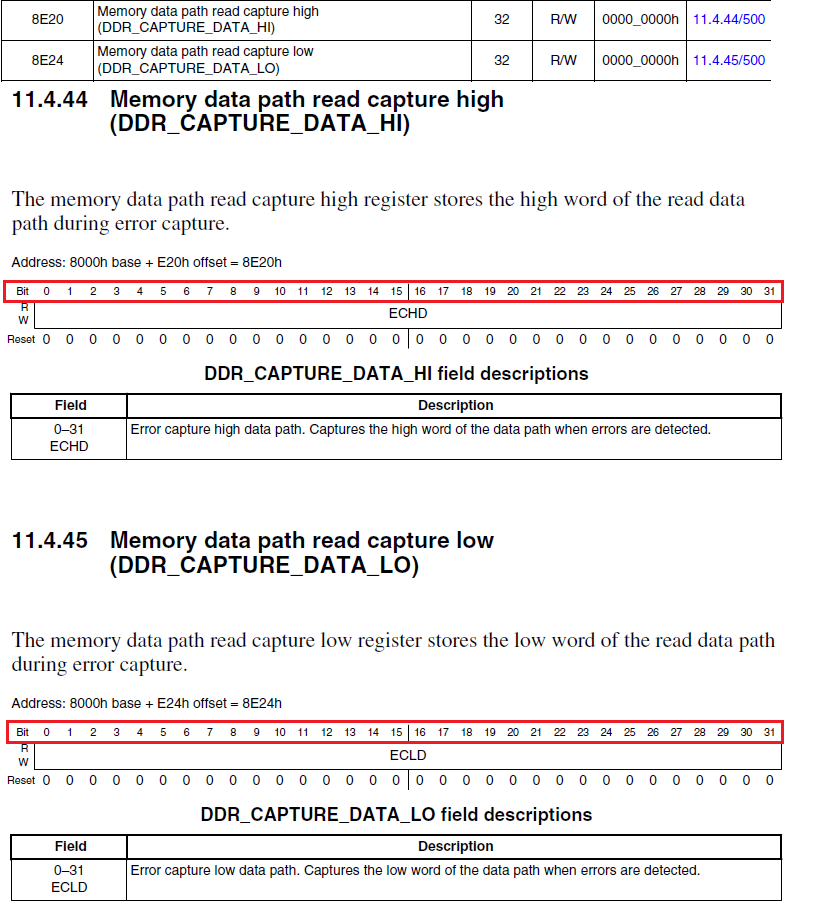

We also need one more information related with this issue. As you know, there are error registers in ddr controller (reference manual). We need to understand which physical dq (ddr data bus of P2041) pin is related with DDR_CAPTURE_DATA_HI/LO. Could you share pin mapping between P2041 physical dq pins to register bits. You can check registers and mentioned bits of registers. The required mapping from dq to bit is indicated by rred rectangular.

Ex: DDR_CAPTURE_DATA_HI[0] (left most of register) is DQ[63] of P2041.

Extra information: We use 64+8ECC configuration and reference manual gives register definition from 0 to 31. When register of P2041 is read by JTAG debugger. [0] bit maps to msb of read data.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for reply. You can be sure of that it is verified design and there has been already multiple of hundered (>>100) produced board and has been used in field. This error is observed on a few boards and we want to be sure about the error. We have been checking all posibilities. But, we want to learn following topics;

-What is auto calibration and which operations it includes (leveling or etc). I will be happy if you share operation processed in auto calibration.

-As i understand from your reply, it is possible to fail ACE while there is data bus (ex: dq[x]) error on bus. Is it correct?

Have a nice day,