- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions Knowledge Base

- :

- Introduction to I2C Interface

Introduction to I2C Interface

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Introduction to I2C Interface

Introduction to I2C Interface

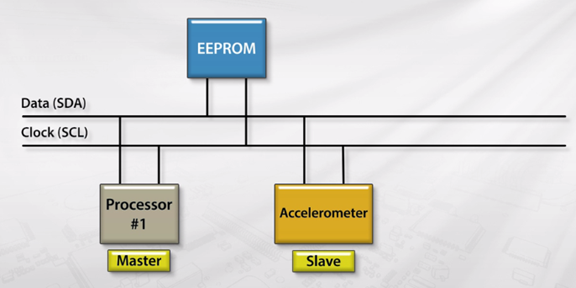

I2C is a common way to interface a processor with a peripheral such as EEPROM, accelerometer, or communication device, and can even be used to communicating with another processor.

Quick Review of I2C

I2c: inter-integrated circuit, meaning that is a communication channel between integrated circuit devices, typically from a microprocessor to a peripheral device, such as a memory chip, some type of sensor, a data converter or maybe a display. By design, i2c isn’t intended for high throughput connections, so you won’t see it used for something like chip ram, rather it is typically used when relatively small amount of data is being sent or received.

There are only two conductors through the i2c bus, the first is a serial clock line which is usually written as SCL, as the name implies, SCL is a clock signal sent on this line. The second is a serial of data line, or SDA, and the data sender on this line will be synchronized with a clock signal making it easier for the receiver to decoding incoming data, and i2c connections is one to one link, with one device being as a master and the other being a slave. But multiple devices can be connected to the same bus with different one to one pairs communicating on the channel.

Only one pair can be communicating at a time of course, and having more than one device capable of being a master will acquire additional synchronization to avoid conflicts.

With i2c, the communication is poll response, meaning the master will poll slave with either data that wants to send to slave or send a command request the slave sends specific information back, only the master can initiate communication and part of the job is to provide the clock signal, which should does not only when is transmitting, but also when the slave is transmitting back.

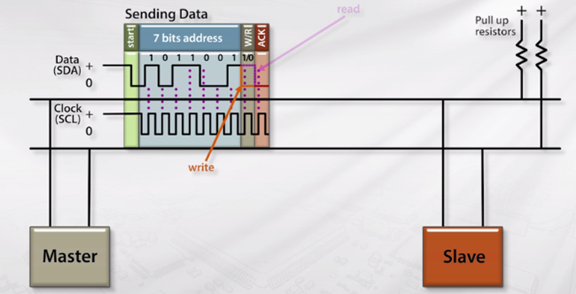

Sending Data with I2C

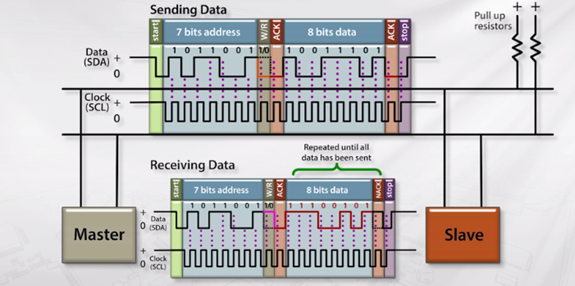

The clock and data lines have pull up resistors, so when the bus is idle and both of the wires will be in high state. To begin a transmission, a master pulls a data line low which is refer to as a start condition , the master then drives the clock signal while sent 7 address bits on the data line. The address bits are followed immediately by either a 0 to indicate the master wants to send the data or a 1 meaning the master would like to read the data back from the slave, the seven address bits must closely bound to a slave device that is on the bus of course, and the device with margin address will set as an acknowledge or an ACK bit on the data line to indicate that has receive the request which is done by holding the data line low.

At this stage, one of two things going to happen. If the master wants to send data or a command to address the slave , he will continue on with first byte to transmit , data bits will sent out and again the address slave or add the ACK bit at the end , this continues until the master is done sending it’s commanding data. And there is no fixed limit to size of the message.

If the master is just sending data and is not expecting receive response back from the slave, it will indicate that is done by signaling a STOP condition, after the last data byte is sent. However, instead of sending data, the master maybe expecting the salve to immediately to reply back and signals this request, with a read bit have the address, In this case, slave acknowledge address and then sent out a byte of data synchronize to the master’s clock , once the byte is complete, the master will indicate acknowledgement of the data, and this continues until the master receives the amount of data it was expecting. It signals to the device the expected amount of data has been received by not acknowledging a last byte. And instead leaves the data line high, which is called the NAK for not acknowledge.

Finally the master terminates the communication by signaling a stop condition and stops generation of the clock signal.

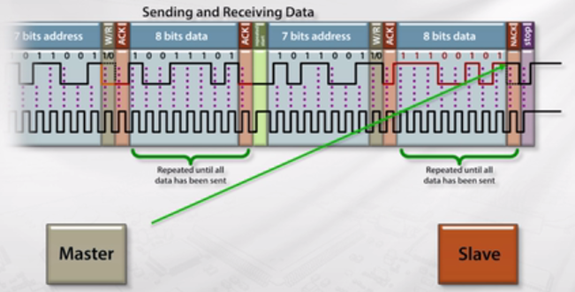

And the last thing to cover is the case when the master like to send either data or a command and immediately receive data back from the slave. So a combination of previous two scenarios, the first part of the transaction is identical to just sending data with master sending out the number of bytes has to transmit, and the slave acknowledge each byte. However, the stop condition is not asserted at the end of transmission, and the master will send a start bit , which is called a repeatedly start bit. The seven address bits will send again followed by a read setting which the slave acknowledge. The slave then send the data with the master’s address on each byte until the last byte which isn’t acknowledged, and the session is terminated with a stop bit.

Note:

This document is the 11th Installment of the "Essentials of MQX RTOS Application Development" training course. Please watch the vedio for more details