- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- about AIPS for UART DMA

about AIPS for UART DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

about AIPS for UART DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am now using 5748G EVB to write a UART DMA demo. I noticed that a similar demo on 5744p there is AIPS_A_init() and AIPS_B_init(). But I don't quite know how to use this module. Is it the same on 5748GEVB? Here is the code for 5744P.

void AIPS_A_Init(void)

{

// All Master Can go through AIPS_A and all peripheral have no protection

// Master Privilege Register A

AIPS_A.MPRA.R = 0x77777777;

// Peripheral Access Control Register

AIPS_A.PACR[0].R = 0x0;

AIPS_A.PACR[1].R = 0x0;

AIPS_A.PACR[2].R = 0x0;

AIPS_A.PACR[3].R = 0x0;

//AIPS_A.PACR[4].R = 0x0; - Reserved, not implemented

AIPS_A.PACR[5].R = 0x0;

AIPS_A.PACR[6].R = 0x0;

AIPS_A.PACR[7].R = 0x0;

// Off-Platform Peripheral Access Control Register

AIPS_A.OPACR[0].R = 0x0;

AIPS_A.OPACR[1].R = 0x0;

AIPS_A.OPACR[2].R = 0x0;

AIPS_A.OPACR[3].R = 0x0;

AIPS_A.OPACR[4].R = 0x0;

AIPS_A.OPACR[5].R = 0x0;

AIPS_A.OPACR[6].R = 0x0;

AIPS_A.OPACR[7].R = 0x0;

AIPS_A.OPACR[8].R = 0x0;

AIPS_A.OPACR[9].R = 0x0;

AIPS_A.OPACR[10].R = 0x0;

AIPS_A.OPACR[11].R = 0x0;

AIPS_A.OPACR[12].R = 0x0;

AIPS_A.OPACR[13].R = 0x0;

AIPS_A.OPACR[14].R = 0x0;

AIPS_A.OPACR[15].R = 0x0;

AIPS_A.OPACR[16].R = 0x0;

AIPS_A.OPACR[17].R = 0x0;

AIPS_A.OPACR[18].R = 0x0;

AIPS_A.OPACR[19].R = 0x0;

AIPS_A.OPACR[20].R = 0x0;

AIPS_A.OPACR[21].R = 0x0;

AIPS_A.OPACR[22].R = 0x0;

AIPS_A.OPACR[23].R = 0x0;

AIPS_A.OPACR[24].R = 0x0;

AIPS_A.OPACR[25].R = 0x0;

AIPS_A.OPACR[26].R = 0x0;

AIPS_A.OPACR[27].R = 0x0;

AIPS_A.OPACR[28].R = 0x0;

AIPS_A.OPACR[29].R = 0x0;

AIPS_A.OPACR[30].R = 0x0;

AIPS_A.OPACR[31].R = 0x0;

}

/*******************************************************************************

Function Name : AIPS_B_Init

Engineer : Martin Kovar

Date : Dec-16-2015

Parameters : NONE

Modifies : NONE

Returns : NONE

Notes : Setup access right for Masters and Peripherals on AIPS

Issues : NONE

*******************************************************************************/

void AIPS_B_Init(void)

{

// All Master Can go through AIPS_B and all peripheral have no protection

// Master Privilege Register A

AIPS_B.MPRA.R = 0x77777777;

// Peripheral Access Control Register

AIPS_B.PACR[0].R = 0x0;

AIPS_B.PACR[1].R = 0x0;

AIPS_B.PACR[2].R = 0x0;

AIPS_B.PACR[3].R = 0x0;

//AIPS_A.PACR[4].R = 0x0; - Reserved, not implemented

AIPS_B.PACR[5].R = 0x0;

AIPS_B.PACR[6].R = 0x0;

AIPS_B.PACR[7].R = 0x0;

// Off-Platform Peripheral Access Control Register

AIPS_B.OPACR[0].R = 0x0;

AIPS_B.OPACR[1].R = 0x0;

AIPS_B.OPACR[2].R = 0x0;

AIPS_B.OPACR[3].R = 0x0;

AIPS_B.OPACR[4].R = 0x0;

AIPS_B.OPACR[5].R = 0x0;

AIPS_B.OPACR[6].R = 0x0;

AIPS_B.OPACR[7].R = 0x0;

AIPS_B.OPACR[8].R = 0x0;

AIPS_B.OPACR[9].R = 0x0;

AIPS_B.OPACR[10].R = 0x0;

AIPS_B.OPACR[11].R = 0x0;

AIPS_B.OPACR[12].R = 0x0;

AIPS_B.OPACR[13].R = 0x0;

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The MPC5748G contains also the AIPS (peripheral bridge).

You can configure it in similar way as you see in the MPC5744P example.

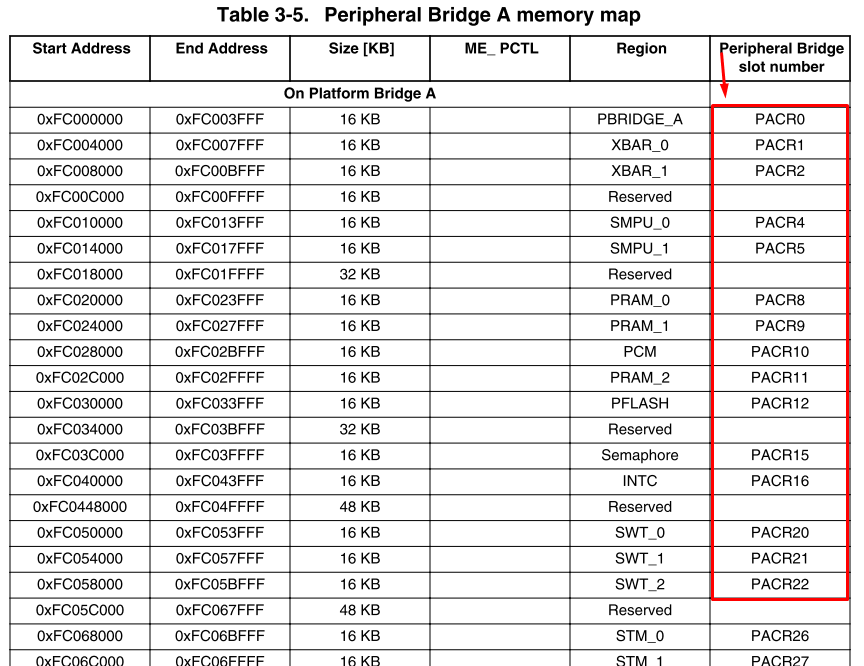

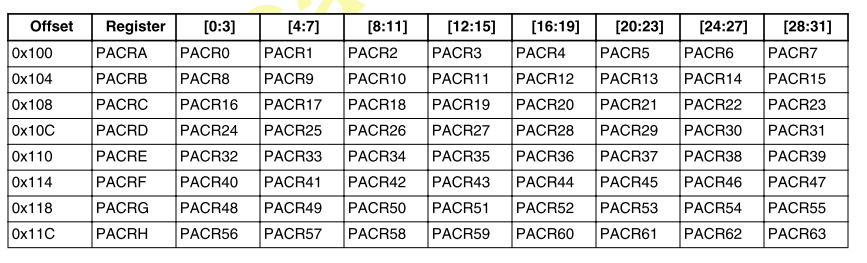

It is well described in Reference manual: 3.6.1 Peripheral Bridge A memory map

If want to access peripherals you need to grant access to them for particular masters exactly like in MPC5744P demo code.

Peter