- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

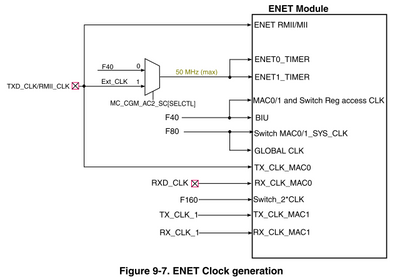

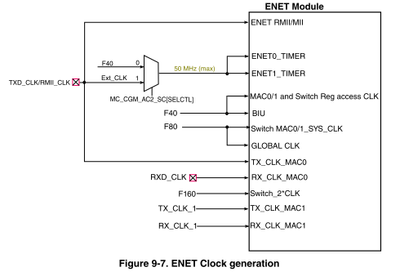

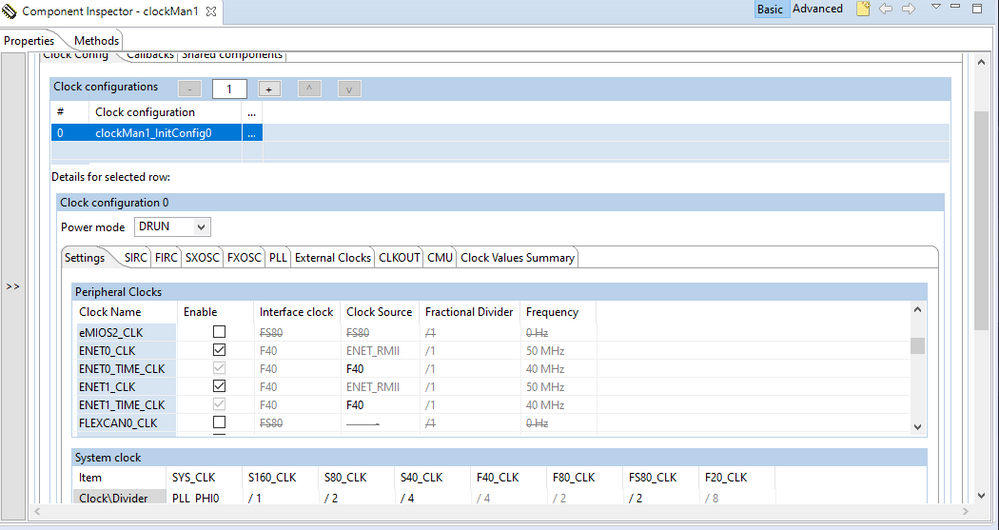

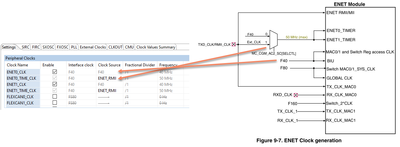

I need help adding Ethernet to the DEVKIT-MPC5748G. I configured all of the pins to exactly how the lwip_mpc5748g demo but I can not make the clock configuration match. the demo has ENET0_CLK set to ENET_RMII with a frequency of 50 MHz. The one I created has the clock source set to F40 with a frequency of 40 MHz. What am I doing wrong? Is there any documentation on how to configure the ethernet?

已解决! 转到解答。

Thanks for the clarification. The difference between what you had and what the demo was setup scared me. I was afraid I would configure the ethernet in a way it would not work on occasionally and you know that kind of bug is a nightmare to debug. Also I hope you are felling better.

I'm sorry for delayed response, I was out of office due to some health issues.

I will ask SDK team if they can fix this.

In fact, the only configurable clock is ENETx_TIMER:

If you have other clocks like F40 or F80 set to its maximum, there will be no problem.

The timer clock is then an auxiliary clock signal for the ENET module that is not needed for normal operation. It is used for IEEE 1588 Time-Sensitive Networking (TSN) applications, which our ENET module supports in hardware. This clock is specifically used for time-stamping IEEE 1588 datagrams.

Regards,

Lukas

Ignore the error. I figured out why I was getting it. The demo for the LWIP SDK 3.0.3 doesn't have enough RAM assigned in the linker file to it based on the configuration. I reduce the amount of RAM assigned to the FreeRTOS and it was able to compile.

That is not what I get for 3.0.3. Also I needed reinstall my IDE because it was acting funny and now the LWIP demo will only compile under Flash build setting not RAM. If I build it under RAM is get the following compile error.

Description Resource Path Location Type

Ld error: lwip_mpc5748g.elf section `.bss' will not fit in region `SRAM' lwip_mpc5748g C/C++ Problem

Ld error: region `SRAM' overflowed by 141456 bytes lwip_mpc5748g C/C++ Problem

Ld error: region `SRAM' overflowed by 36912 bytes lwip_mpc5748g C/C++ Problem

make: *** [makefile:71: lwip_mpc5748g.elf] Error 1 lwip_mpc5748g C/C++ Problem

That is enabled and the frequency is set to the correct value. I tried my best to make it match the LWIP demo but there are settings I can't make match. I also get a warning when I set the PH1 Divider to /4 even though the demo has it configured that way. I attached my code. I hope you can figure out why I can not make my project match the demo.

It looks like you used demo from SDK 3.0.0 for comparison, right? This one seems to be wrong, PHI1 needs to be 80MHz, so divider /8 must be used:

I can see that this is fixed in 3.0.3. so the warning is correct. The same about ENET_CLK:

So, go on with your current configuration.

Regards,

Lukas