- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5775E SDADC sample not correct

MPC5775E SDADC sample not correct

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5775E SDADC sample not correct

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My init code :

void sdADC_Init()

{

sdadc_init(Mcal_SDADC_OSR_24, Mcal_SDADC_Gain_2, Mcal_SDADC_FTHLD_8, Mcal_SDADC_DIFF);

}

void sdadc_init(uint8_t pdr, uint8_t gain, uint8_t fifo_thld, uint8_t inp_mode)

{

/*####################################

* SD ADC 1 CONFIGURATION

####################################*/

SDADC_1.SFR.R = 0x1B; // clear all the status flags

SDADC_1.FCR.B.FRST = 1; // generate reset to flush FIFO

SDADC_1.FCR.B.FTHLD = fifo_thld; // FIFO threshold - overcome generates FIFO full event flag

SDADC_1.FCR.B.FSIZE = 3; // FIFO size: 0 - 1 word, 1 - 4 words, 2 - 8 words, 3 - 16 words

SDADC_1.FCR.B.FOWEN = 0; // disable FIFO overwrite

SDADC_1.FCR.B.FE = 1; // enable FIFO

SDADC_1.RSER.B.DFFDIRS = 1; // DMA request on data FIFO full

SDADC_1.RSER.B.DFFDIRE = 1; // data FIFO full request enable

SDADC_1.MCR.B.MODE = inp_mode; // input mode: 0 - differential, 1 - single-ended

SDADC_1.MCR.B.PDR = pdr; // Oversampling rate

SDADC_1.MCR.B.PGAN = gain; // Gain

SDADC_1.MCR.B.HPFEN = 1; // High-pass filter enabled

SDADC_1.MCR.B.EN = 1; // internal SDADC modulator enabled

SDADC_1.OSDR.B.OSD = 1; // set the output settling delay

SDADC_1.CSR.B.ANCHSEL = 0; // analog input channel AN[x] selection

SDADC_1.MCR.B.TRIGEN = 1; // enable HW trigger

/*####################################

* SD ADC 2 CONFIGURATION

####################################*/

SDADC_2.SFR.R = 0x1B; // clear all the status flags

SDADC_2.FCR.B.FRST = 1; // generate reset to flush FIFO

SDADC_2.FCR.B.FTHLD = fifo_thld; // FIFO threshold - overcome generates FIFO full event flag

SDADC_2.FCR.B.FSIZE = 3; // FIFO size: 0 - 1 word, 1 - 4 words, 2 - 8 words, 3 - 16 words

SDADC_2.FCR.B.FOWEN = 0; // disable FIFO overwrite

SDADC_2.FCR.B.FE = 1; // enable FIFO

// DMA settings

SDADC_2.RSER.B.DFFDIRS = 1; // DMA request on data FIFO full

SDADC_2.RSER.B.DFFDIRE = 1; // data FIFO full request enable

SDADC_2.MCR.B.MODE = inp_mode; // input mode: 0 - differential, 1 - single-ended

SDADC_2.MCR.B.PDR = pdr; // Oversampling rate

SDADC_2.MCR.B.PGAN = gain; // Gain

SDADC_2.MCR.B.HPFEN = 1; // High-pass filter enabled

SDADC_2.MCR.B.EN = 1; // internal SDADC modulator enabled

SDADC_2.OSDR.B.OSD = 1; // set the output settling delay

SDADC_2.CSR.B.ANCHSEL = 0; // analogue input channel AN[x] selection

SDADC_2.MCR.B.TRIGSEL = 0; // SDADC_1 trigger output selected as an input trigger for SDADC

SDADC_2.MCR.B.TRIGEDSEL = 1; // rising edge of trigger input selected

SDADC_2.MCR.B.TRIGEN = 1; // enable HW trigger

}

void sdadc_start(void)

{

// start the SDADC_1 by SW trigger

SDADC_1.STKR.R = 0xFFFF;

}

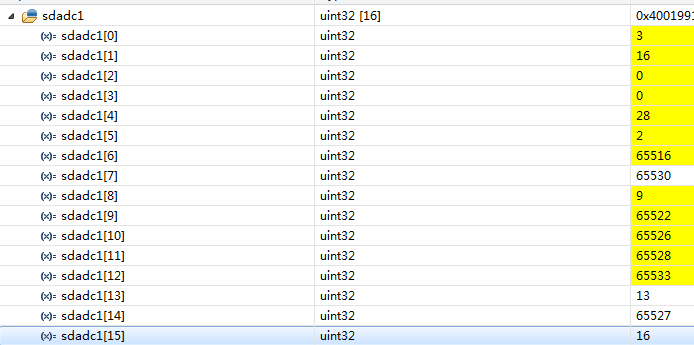

uint32 sdadc1[16];

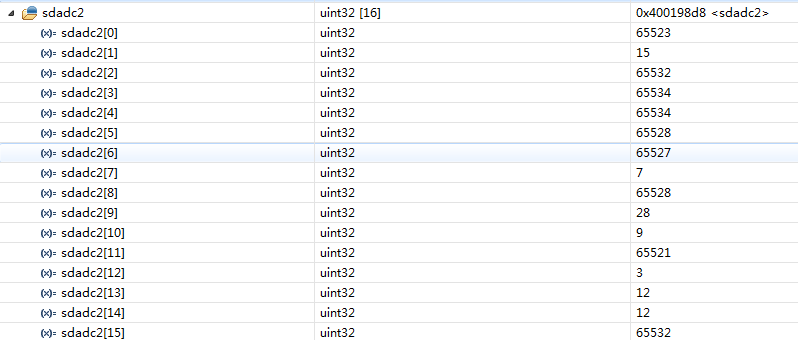

uint32 sdadc2[16];

void edma_init(void)

{

uint8_t hsr_ch = 48; // this number TBD

// DMA B ch 36 - SDADC0 result ready

// DMA B ch 37 - SDADC1 result ready

// DMA channels for eQADC:

// DMA settings for SDADC_0 request

DMA_B.TCD[36].SADDR.R = (uint32_t)&SDADC_1.CDR.R;

DMA_B.TCD[36].ATTR.B.SMOD = 0; /* source address modulo*/

DMA_B.TCD[36].ATTR.B.SSIZE = 2; /* source data size: 32bit */

DMA_B.TCD[36].ATTR.B.DMOD = 0; /* destination address modulo: 32 datawords each 4 bytes */

DMA_B.TCD[36].ATTR.B.DSIZE = 2; /* destination data size: 32bit */

DMA_B.TCD[36].SOFF.R = 0; /* source address signed offset */

DMA_B.TCD[36].NBYTES.MLNO.R = 32; /* inner "minor" byte count */

DMA_B.TCD[36].SLAST.R = 0; /* TCD Last Source Address Adjustment */

DMA_B.TCD[36].DADDR.R = (vuint32_t)sdadc1; /* destination address */

DMA_B.TCD[36].CITER.ELINKYES.B.ELINK = 0; /* Enable channel-to-channel linking on minor-loop complete */

DMA_B.TCD[36].CITER.ELINKYES.B.LINKCH = hsr_ch; /* Minor Loop Link Channel Number */

DMA_B.TCD[36].CITER.ELINKYES.B.CITER = 4; /* current major iteration count */

DMA_B.TCD[36].DOFF.R = 4; /* signed destination address offset */

DMA_B.TCD[36].DLASTSGA.R = -128; /* last destination address adjustment /scatter gather address */

DMA_B.TCD[36].BITER.ELINKYES.B.ELINK = 0; /* enable channel-to-channel linking on minor loop complete */

DMA_B.TCD[36].BITER.ELINKYES.B.LINKCH = hsr_ch; /* Minor Loop Link Channel Number */

DMA_B.TCD[36].BITER.ELINKYES.B.BITER = 4; /* beginning major iteration count */

DMA_B.TCD[36].CSR.B.MAJORELINK = 1; /* enable channel-to-channel linking on major loop complete */

DMA_B.TCD[36].CSR.B.MAJORLINKCH = hsr_ch; /* Major Loop Link Channel Number */

// DMA settings for SDADC_1 request

DMA_B.TCD[37].SADDR.R = (uint32_t)&SDADC_2.CDR.R;

DMA_B.TCD[37].ATTR.B.SMOD = 0; /* source address modulo*/

DMA_B.TCD[37].ATTR.B.SSIZE = 2; /* source data size: 32bit */

DMA_B.TCD[37].ATTR.B.DMOD = 0; /* destination address modulo: 32 datawords each 4 bytes */

DMA_B.TCD[37].ATTR.B.DSIZE = 2; /* destination data size: 32bit */

DMA_B.TCD[37].SOFF.R = 0; /* source address signed offset */

DMA_B.TCD[37].NBYTES.MLNO.R = 32; /* inner "minor" byte count */

DMA_B.TCD[37].SLAST.R = 0; /* TCD Last Source Address Adjustment */

DMA_B.TCD[37].DADDR.R = (vuint32_t)sdadc2; /* destination address */

DMA_B.TCD[37].CITER.ELINKNO.B.ELINK = 0; /* Disable channel-to-channel linking on minor-loop complete */

DMA_B.TCD[37].CITER.ELINKNO.B.CITER = 4; /* current major iteration count */

DMA_B.TCD[37].DOFF.R = 4; /* signed destination address offset */

DMA_B.TCD[37].DLASTSGA.R = -128; /* last destination address adjustment /scatter gather address */

DMA_B.TCD[37].BITER.ELINKNO.B.ELINK = 0; /* Disable channel-to-channel linking on minor loop complete */

DMA_B.TCD[37].BITER.ELINKNO.B.BITER = 4; /* Beginning major iteration count */

DMA_B.TCD[37].CSR.B.MAJORELINK = 0; /* Disable channel-to-channel linking on major loop complete */

}

void edma_start(void)

{

/* Enable eDMA channels*/

DMA_B.SERQ.R = 36; /* SDADC0 result ready */

DMA_B.SERQ.R = 37; /* SDADC1 result ready */

}

The SDADC_AN[0] connent to 1.25V voltage, the SDADC_AN[1] connect to GND. and the sdadc read back value:

I have change the SDADC_AN[0] to other voltages, but the adc read value was not effect .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

firstly I would ask whether you have ever SDADC running for instance with simple configuration used in my example here:

Example MPC5777C-SDADC_simple GHS614

I have certain doubts about SDADC configuration, I am missing send key to reset ADC to start sampling, also I guess OSDR would require different values. Is your code based on certain example code?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My code is based solely on register descriptions in the technical manual and has not run any other test Demo.