- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MPC5746R DECFILTER howto?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I've been struggling with the decimation filter on the MPC5746R.

I have been using the Reference Manual, AN4209 and the MPC5676R example posted a few days ago by davidtosenovjan

Is there any working example code for a standalone application ? (i.e. polled, not interrupt or DMA.)

Are there any more training materials?

What I got particularly stuck on is the behaviour of the status register and bits IDF, IBIF, ODF, OBIF. I'm still unclear from the RM which ones I should be checking. I _was_ trying to use IBIF and OBIF but they are rarely set. Now I check and clear both pairs and FINALLY got some data to go in and out of the filter. What is correct usage of these bits?

James

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

You should poll IBIC and OBIC and clear both flags by IDFC and ODFC. I would however rather expect using of interrupts or DMA approaches.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I was using polling to then feed the data to an SPI DAC that uses a different data format and therefore cannot use DMA.

Those input MUXing options are a complete surprise to me, I didn't think of looking there at all as the manual says (seemed to say?) there are no links in hardware.

Any chance of getting your useful clarification added? and the references to more than two filter blocks removed?

James

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There is no internal data bus between ADC and DECFILTER (on MPC5777C and several MPC56xx devices called 'Parallel Side Interface'), that's what was mentioned by 'no direct hardware interface'. But there is a hardware interface between eTPU/eMIOS and DECFILTER (triggers).

Regarding MCR[ISEL]=0, I will report it as a documentation error. Thanks for pointing it out.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

OK, I understand that now. As I said, a documentation update to make that explicitly clear with your words "there is a hardware interface between eTPU/eMIOS and DECFILTER (triggers)." and referencing the input MUXing spreadsheet would certainly help.

One more question, hopefully my last ( ! )

What are INTAG and OUTTAG used for? The only references I can find are in sections 36.4.5 and 36.4.6 ? (On the 5777C they appear to used by the eQADC.)

James

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Also, the Ref manual says

"The integrator halt and enable states can be controlled in the following

ways:

• by hardware, through external signals"

Can anyone provide more detail on these external signals? I have a strong feeling that this text is incorrect for this chip. For comparison I looked at the MPC5777C and it has hardware links to the eTPU for those signals. The MPC5746R DECFILTER does not have any links to other modules according to the introduction to the section.

Rather than just copying/pasting module descriptions it would be helpful if the manual authors would edit them to remove superfluous and misleading text. The section about head/middle/tail filters is a good example, someone added a note to say ignore "middle" because the rest of the page has text and diagrams showing filter combinations that are impossible on the 5746R. This is not helpful in understanding a complex module. Instead of adding a note... fix the text!!

Likewise the description of MCR[ISEL] seems contradictory. The specific section says that value 0 is reserved, but the introduction shows value 0 might be used in a cascade combo?

James

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

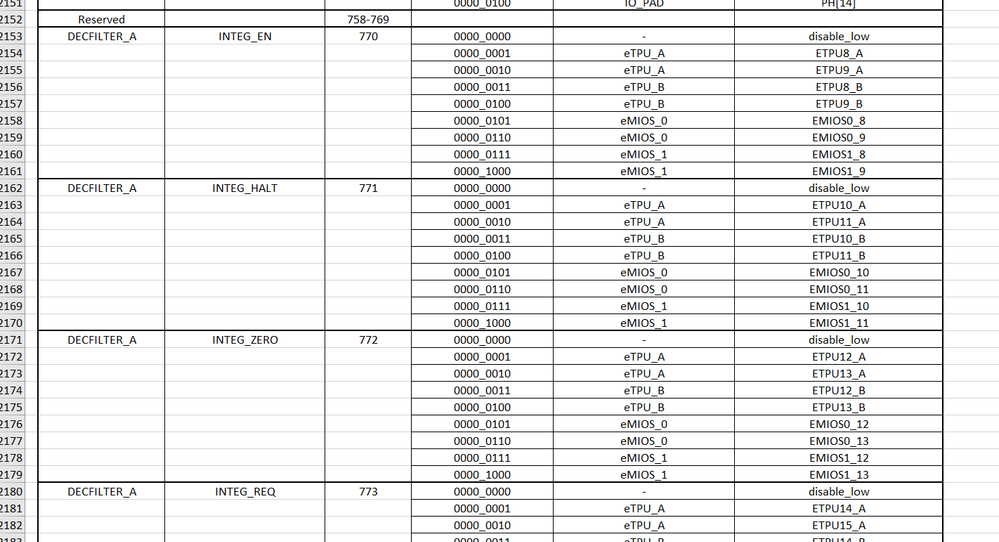

Hi, routing on this device is made slightly different way and it is described in excel sheet embedded in the RM.

In the tab 'Input Muxing' you may see eTPU/eMIOS routing to decimation filters' integrators.

Regarding MCR[ISEL], you are right. Because on this device there is no direct hardware interface from the SAR and Sigma-Delta ADCs to the Decimation Filters on the device (because this device does not have eQADC module normally offering this feature). MCR[ISEL]=0 is not an option.