- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Flash Questions On MPC5744P

Flash Questions On MPC5744P

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Flash Questions On MPC5744P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello , I have a project on Can Flash Boot Loader Routine. I have some wonders.

Because in my demo flash boot loader, some functions of FBL routine is replaced in the SRAM . I wonder that when the FBL is excuted from flash , the entire flash section can not be erased and programed.

If the flash loader routine is excuted from one section in the flash, Could the FBL routine erase the another section and program the app in that section ?

Thank you very much !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

there's only one rule - you can't access partition which is being programmed or erased. The partitions are described in Table 5-4:

https://www.nxp.com/docs/en/reference-manual/MPC5744PRM.pdf

So, the code must be executed from another partition or from RAM memory. If interrupts are used, either disabled them or ensure that it will not access programmed partition during the flash operation.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Lukas, Thank you very much !

I have find two demo about MPC5748G of flash manipulation on your website, one is using SSD and another is not .

Could you please give some Instruction Document on the SSD ? And I also need the SSD source files, Could you provide for me ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

SSD user manual can be found in this package:

https://www.nxp.com/webapp/Download?colCode=C55_NVM_SSD

SSD source files are not provided.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

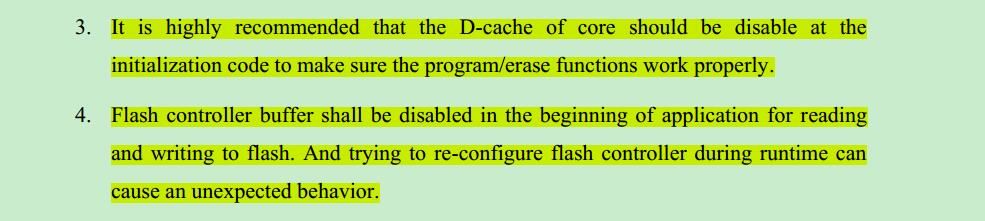

Hello , I have check the User's Manual of the SSD.

About the 3.3 Notes and Limitations.

On the 3, how to disable the D-cache ? I have check the SSD demo just disable the flash controller buffer, but not disable the D-cache.

Could you give me some advice?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

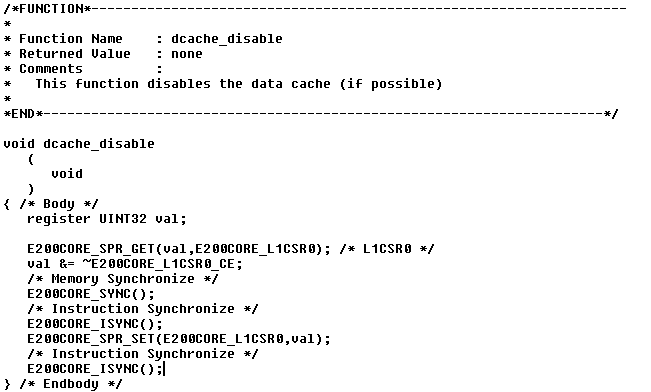

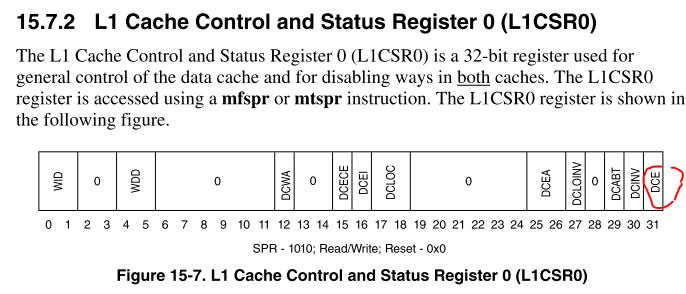

see this file:

c:\Program Files (x86)\Freescale\Standard Software Driver v1.1.0\MPC57xx\Demos\Demo_code\common\DCache.c

Function "dcache_disable" disables the data cache. It writes L1CSR0 register:

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much!

Besides, If I don't use SSD, just manipulate the register to erase and program the flash. The Notes and Limitations 3 and 4 mentioned above are unnecessary ,right ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No, it doesn't matter if you use SSD drivers or if you write the flash registers by your own code. The result is the same.

For example, let's say that that there are some data in flash, you read them by your SW, so they are cached in data cache memory. If you erase that block now (and it doesn't matter if you do that by SSD drivers or by own code), the cache is not informed about that, so there are still old data. There's no HW coherency unit. You need to either invalidate the cache manually or this area must be set as cache inhibited. Or disable the cache completely but this is usually not an option due to performance.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much !

Regards,

Meng