- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi everyone, I am trying to make data cache to be used as ram in mpc5777c for that purpose I've invalidated and enable the dcache in copy back mode, then I've created a tlb entry at address 0x40040000 and set it as cacheable

The dcache code goes like this:

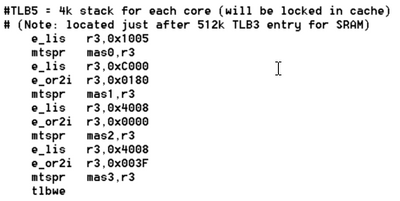

the tlb entry is:

e_lis r3, 0x1005 /* Select TLB entry #, define R/W replacment control */

mtspr 624, r3 /* Load MAS0 with 0x1006 0000 for TLB entry #6 */

/* Define description context and configuration control:*/

/* VALID=1, IPROT=0, TID=0, TS=0, TSIZE=1 (4KB size) */

e_lis r3, 0x8000 /* Load MAS 1 with 0x8000 0100 */

e_ori r3, r3, 0x0100

mtspr 625, r3

/* Define EPN and page attributes: */

/* EPN = 0x4004 0000, WIMAGE = all 0's */

e_lis r3, 0x4004 /* Load MAS2 with 0x4004 0000 */

mtspr 626, r3

/* Define RPN and access control for data R/W */

/* RPN = 0x4004 0000, U0:3=0, UX/SX=0, UR/SR/UW/SW=1 */

e_lis r3, 0x4004 /* Load MAS3 with 0x4004 000F */

e_ori r3, r3, 0x003F

mtspr 627, r3

tlbwe

After doing all this I dont see any difference though when writing at memory address 0x40040000 nothing happens even after removing the tlb I dont see any change.

I've changed the memory to 0x40040000 just for checking the data is written on the ram but not in the dcache (I am using trace32 as debugger) the dcache shows nothing but 0 as defined in the dcache code.

BR,

Indra

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

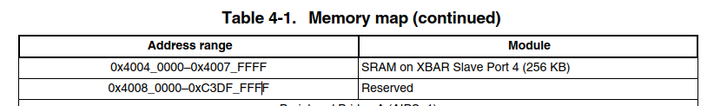

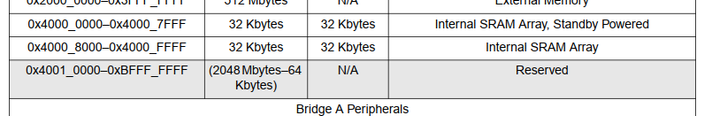

The problem is that in the cookbook, used virtual and physical address is 0x4004_0000 but on MPC5777C there is SRAM space on that address.

Cookbook used MPC55xx and there is nothing in the memory map for that area. That's the point.

You need to choose different address, but how I already answered on address 0x4008_0000, SW startup may configure stack located in cache as we are doing it this way on MPC5777C device.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I am not sure what you are trying to do, but this is usually done by startup code, as this area is used for core stack (as this derivative does not have TCM memories).

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry foe the confusion what I want to achieve is to use dcache as ram to increase the available ram size. i referred a cookbook it says to use cache as ram the cache is invalidated and enabled in copyback mode. All I want is to increase my ram size my using dcache 16kb memory as ram is that possible

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I see. You can use the rest of cache for increasing SRAM capability for instance as TLB6 or increase the area used for stack to 16k. A procedure described in cookbook in correct in principle.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi @davidtosenovjan I've implemented everything as per the cookbook i.e. 1. making a tlb entry 2. Invalidating and enabling the cache in copyback mode 3. loacking the cache line

after this I've tried to write at the memory location but here the data is written to both cache and the main memory. Correct me if I did something wrong

BR,

Indra

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The problem is that in the cookbook, used virtual and physical address is 0x4004_0000 but on MPC5777C there is SRAM space on that address.

Cookbook used MPC55xx and there is nothing in the memory map for that area. That's the point.

You need to choose different address, but how I already answered on address 0x4008_0000, SW startup may configure stack located in cache as we are doing it this way on MPC5777C device.