- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- CAN-FD 64 bytes on MCP5748G

CAN-FD 64 bytes on MCP5748G

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This is a continuation of this thread , the TX/RX for CAN-FD frame of 8 bytes works fine, i want to configure the module tu support 64bytes. the changes made so far are :

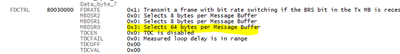

FDCTR

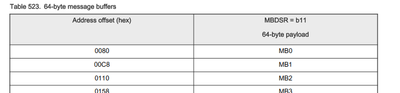

Increase message buffer to support 64 bytes

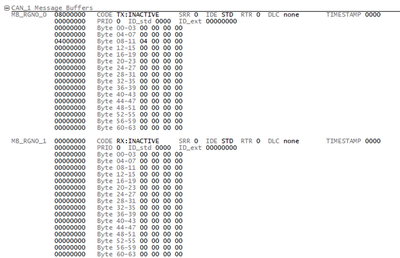

MB0 and MB1 seems to have the correctly lenght in the register view :

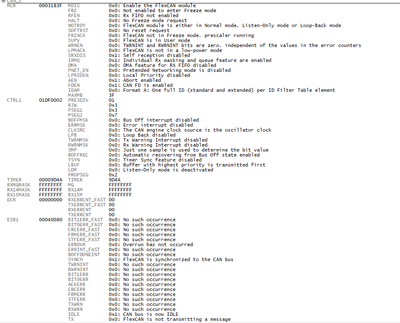

No interrupppt is triggered once i send a CAN frame from canoe. i think other configuration could be needed , below is the code for the config :

ErrorCode FlexCANDevice::init()

{

/* enable the FlexCAN module, reset and freeze */

fpDevice->MCR.R = (0

| CAN_MCR_FRZ /* enabled to enter Freeze mode */

| CAN_MCR_HALT /* enter freeze mode if FRZ bit is set */

//| CAN_MCR_SOFTRST /* soft reset */

//| CAN_MCR_SRXDIS /* self reception enable */

| CAN_MCR_BCC /* individual Rx masking and queue */

| 0x0000003F);

/* double check that we are actually in freeze mode */

while(0 == fpDevice->MCR.B.FRZACK) {};

while(0 == fpDevice->MCR.B.NOTRDY) {};

fpDevice->MCR.R = (0

| CAN_MCR_FRZ /* enabled to enter Freeze mode */

| CAN_MCR_HALT /* enter freeze mode if FRZ bit is set */

| CAN_MCR_SRXDIS /* self reception disabled */

| CAN_MCR_BCC /* individual Rx masking and queue */

| CAN_MCR_AEN /* Safe Tx abort enable */

| CAN_MCR_FDEN /* CAN FD enabled */

| 0x0000003F); /* enable 64 MBs */

// Set CAN Bit Timing Register (CAN_CBT. P-1747)

fpDevice->CBT.B.BTF = 1; // Enable extended bit time definitions

fpDevice->CBT.B.EPRESDIV = fConfig.bitrate_cbt.presDiv;

fpDevice->CBT.B.ERJW = fConfig.bitrate_cbt.rjw;

fpDevice->CBT.B.EPROPSEG = fConfig.bitrate_cbt.propSeg;

fpDevice->CBT.B.EPSEG1 = fConfig.bitrate_cbt.pSeg1;

fpDevice->CBT.B.EPSEG2 = fConfig.bitrate_cbt.pSeg2;

// Set CAN FD Bit Timing register (CAN_FDCBT. P-1768)

fpDevice->FDCBT.B.FPRESDIV = fConfig.bitrate.presDiv;

fpDevice->FDCBT.B.FRJW = fConfig.bitrate.rjw;

fpDevice->FDCBT.B.FPROPSEG = fConfig.bitrate.propSeg;

fpDevice->FDCBT.B.FPSEG1 = fConfig.bitrate.pSeg1;

fpDevice->FDCBT.B.FPSEG2 = fConfig.bitrate.pSeg2;

// Set CAN FD Control register (CAN_FDCTRL .P-1766)

fpDevice->FDCTRL.R = 0;

fpDevice->FDCTRL.B.FDRATE = 1; // bit rate switching enable

fpDevice->FDCTRL.B.TDCEN = 0;

//fpDevice->FDCTRL.B.TDCOFF = 32;

fpDevice->FDCTRL.B.MBDSR0 = fConfig.payload;

// Enable CAN ISO

fpDevice->CTRL2.B.ISOCANFDEN = 1;

// Setup message buffers

fRxInterruptMask = 0;

uint32_t mask = 1;

// Setup MB0 for sending

setupMessageBuffer(0, CANTxBuffer::CODE_INACTIVE, false);

// Setup MB1 for receiving

setupMessageBuffer(1, CANRxBuffer::CODE_EMPTY, false);

fRxInterruptMask |= mask;

mask <<= 1;

return CAN_ERR_OK;

}

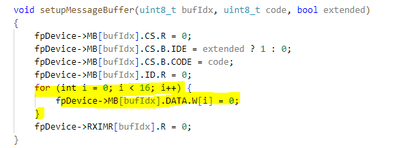

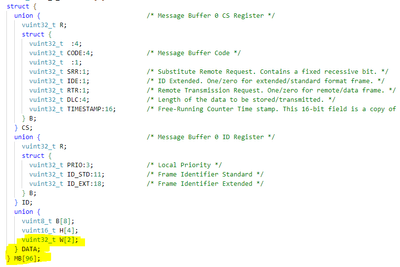

void setupMessageBuffer(uint8_t bufIdx, uint8_t code, bool extended)

{

fpDevice->MB[bufIdx].CS.R = 0;

fpDevice->MB[bufIdx].CS.B.IDE = extended ? 1 : 0;

fpDevice->MB[bufIdx].CS.B.CODE = code;

fpDevice->MB[bufIdx].ID.R = 0;

for (int i = 0; i < 16; i++) {

fpDevice->MB[bufIdx].DATA.W[i] = 0;

}

fpDevice->RXIMR[bufIdx].R = 0;

}

Thank you.

Best regards.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes, you have to, if want to use this structure.

You shared below

debugger shows MBs in right manner for 64byte payload but your init is wrong. Empty CODE for RX MB is on wrong offset.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

be sure you are using right offset for MBs for higher payload setting. From the last picture it is evident you have still offset for 8byte payload setting. See chapter 73.6.5 FlexCAN message buffer memory map for more info

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @PetrS

Thanks for the hint. offset is corrected now

but i could not receive interrupt when sending FD fram with 64byte payload , it works only with 8 bytes?

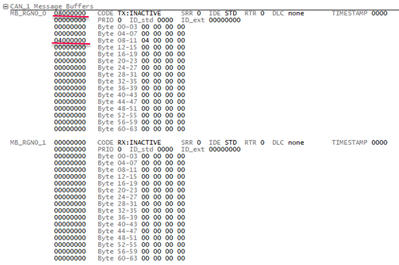

this is the register view :

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

show repaired MB area, and specify what is send from CAN tool. Do you see any error detected there?

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @PetrS

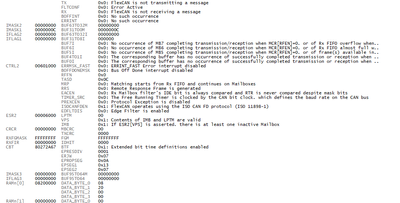

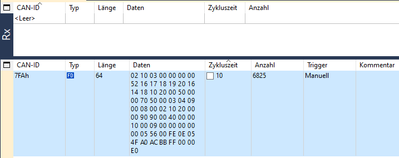

No the tool does not report any error, the data inside the frame is :

shouldn't we modify also the message buffer initialisation since we use 32-64 bytes ?

Best regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes, you have to, if want to use this structure.

You shared below

debugger shows MBs in right manner for 64byte payload but your init is wrong. Empty CODE for RX MB is on wrong offset.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @PetrS ,

Yes you are right, the address Offfset for the MB is wrong.

i could not find/oversee in datasheet where i can set the address offset for each MB ? i could only set the

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I already mentioned it in previous reply.

BR, Petr