- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso IDE

- :

- LPC54606 ENET MAC timestamp trigger interrupt

LPC54606 ENET MAC timestamp trigger interrupt

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC54606 ENET MAC timestamp trigger interrupt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

In LPC54606 manual "36.7.11.8.2 System time correction"

To synchronize or update the system time to reduce system-time jitter (fine correction

method), complete the following steps:

1. With the help of the algorithm explained in Section 36.7.8.9 “System time register

module”, calculate the rate by which you want to make the system time increments

slower or faster.

2. Update the MAC timestamp addend register Table 813 with the new value and set bit

5 of the MAC timestamp control register Table 806.

3. Wait for the time for which you want the new value of the addend register to be active.

You can do this by enabling the timestamp trigger interrupt after the system time

reaches the target value.

4. Enable the timestamp interrupt in bit 12 of MAC interrupt enable register Table 789.

I don't understand "enabling the timestamp trigger interrupt after the system time reaches the target value"

1 which reg should i set the target second and nanosecond? i cann't find in the manual.

2 how do I install the callback function for timestamp interrupt trigger ?

I see in the fsl_enet.c(SDK 2.4.1) function ENET_IRQHandler, sames there is only one callback hold by "handle->callback", but there are multiple interrupt events,

void ENET_IRQHandler(ENET_Type *base, enet_handle_t *handle)

{

/* Check for the interrupt source type. */

/* DMA CHANNEL 0. */

if (base->DMA_INTR_STAT & ENET_DMA_INTR_STAT_DC0IS_MASK)

{

...

handle->callback(base, handle, kENET_RxIntEvent, 0, handle->userData);

....

}

/* DMA CHANNEL 1. */

if (base->DMA_INTR_STAT & ENET_DMA_INTR_STAT_DC1IS_MASK)

{

...

handle->callback(base, handle, kENET_RxIntEvent, 1, handle->userData);

...

}

#ifdef ENET_PTP1588FEATURE_REQUIRED

/* MAC TIMESTAMP. */

if (base->DMA_INTR_STAT & ENET_DMA_INTR_STAT_MACIS_MASK)

{

if (base->MAC_INTR_STAT & ENET_MAC_INTR_STAT_TSIS_MASK)

{

if (handle->callback)

{

handle->callback(base, handle, kENET_TimeStampIntEvent, 0, handle->userData);

}

}

}

...

}

I see in ethernetif.c:

static void enet_init(struct netif *netif, struct ethernetif *ethernetif,

const ethernetif_config_t *ethernetifConfig)

{...

/* Create the handler. */

#if USE_RTOS && defined(FSL_RTOS_FREE_RTOS)

ENET_EnableInterrupts(ethernetif->base, kENET_DmaTx | kENET_DmaRx);

ENET_CreateHandler(ethernetif->base, ðernetif->handle, &config, &buffCfg[0], ethernet_callback, netif);

#endif...

use "ENET_CreateHandler" to install callback for timestamp interrupt trigger event? if so , what the value of "enet_config_t *config, enet_buffer_config_t *bufferConfig" should input?

thanks very much.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I try to find the same registers (registers to set time to trig an interrupt TSTRIG bit of MAC_TIMESTAMP_CTRL).

I follow documentation, but find nothing.

LPC54s018

Any advice will be welcome

regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You can check the MCUXpresso SDK API Reference Manual for reference.

https://mcuxpresso.nxp.com/api_doc/dev/329/group__lpc__enet.html

Have a nice day!

Sol

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sol

thanks for helping.

I go through enet.c and enet.h detailly, bug found no unswer.

is this a bug?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

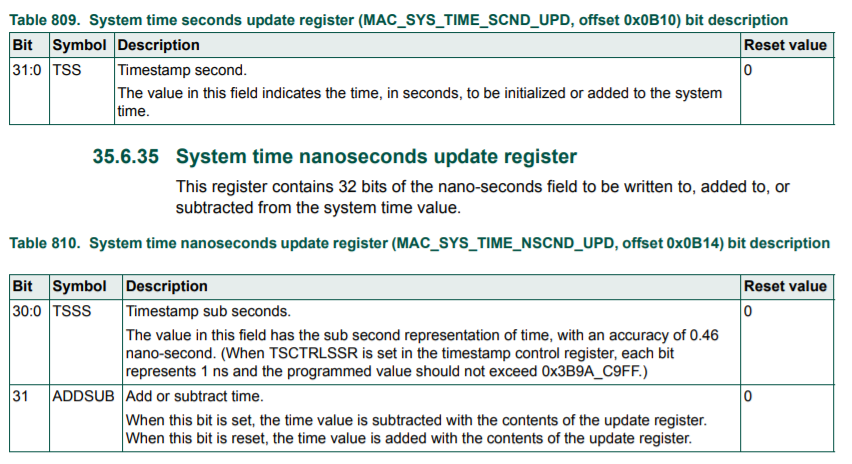

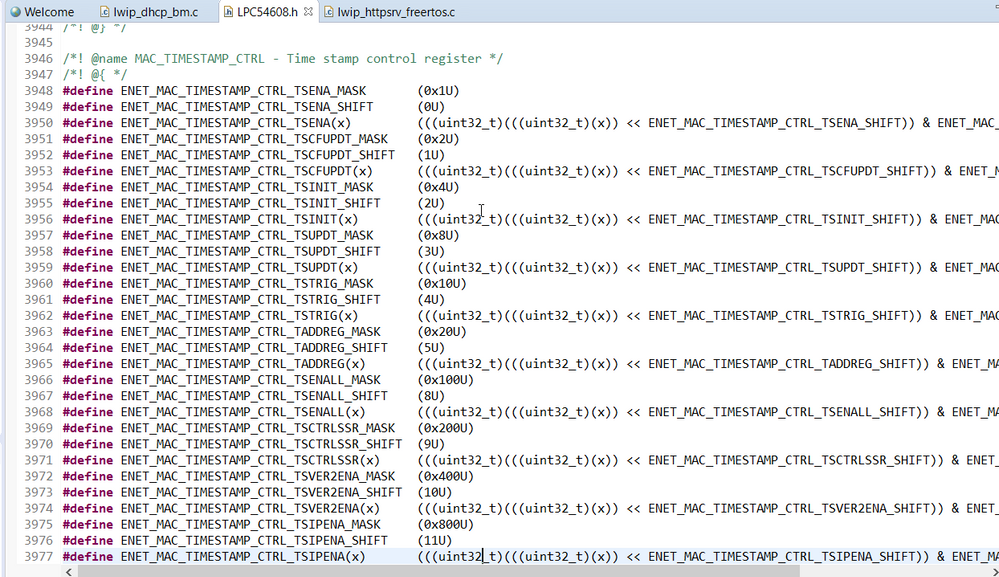

The bit TSTRIG in the MAC timestamp control register Enable timestamp interrupt trigger.

the bit TSUPDT in the same register Update timestamp. When this bit is set, the system time is updated (added or subtracted) with the value specified in MAC system time seconds update Table 809 and MAC system time nanoseconds update Table 810. This bit should be zero before updating it. This bit is reset when the update is complete in hardware. The timestamp higher word register (if enabled during core configuration) is not updated. Access restriction applies. Setting 1 sets. Self-cleared. Setting 0 has no effect.

The lpc54608.h file contains the definitions for the Time stamp control register.

I hope this helps,

Regards

Soledad

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Soledad

Thanks helping.

There are 2 method described in LPC54606 manual "36.7.11.8.2 System time correction", " coarse correction method " and " fine correction method ", your reply explains " coarse correction method ", I asked " fine correction method ".

I just do't understand the flow described in the manual.

thanks again.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for the delay.

In the fine correction method, a slave clock’s frequency drift with respect to the master clock (as defined in IEEE 1588) is corrected over a period of time instead of in one clock, as in coarse correction. This helps maintain linear time and does not introduce drastic changes (or a large jitter) in the reference time between PTP sync message intervals. In this method, an accumulator sums up the contents of the addend register. The arithmetic carry that the accumulator generates is used as a pulse to increment the system time counter. The accumulator and the addend are 32-bit registers. Here, the accumulator acts as a high-precision frequency multiplier or divider.

The system time update logic requires a 50 MHz clock frequency to achieve 20 ns accuracy. The frequency division is the ratio of the reference clock frequency to the required clock frequency. Hence, if the reference clock is, for example, 66 MHz, this ratio is calculated as 66 MHz / 50 MHz = 1.32. Hence, the default addend value to be set in the register is 232 / 1.32, 0xC1F07C1F. If the reference clock drifts lower, to 65 MHz for example, the ratio is 65 / 50, or 1.3 and the value to set in the addend register is 232 / 1.30, or 0xC4EC4EC4. If the clock drifts higher, to 67 MHz for example, the addend register must be set to 0xBF0B 7672. When the clock drift is nil, the default addend value of 0xC1F0 7C1F (232 / 1.32) must be programmed.

Have a nice day!

Sol

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

could someone help on this,thanks.