- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- Identification and Security

- i.MX Processors

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- CodeWarrior

- Wireless Connectivity

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Re: SDRAM low power mode

SDRAM low power mode

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SDRAM low power mode

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

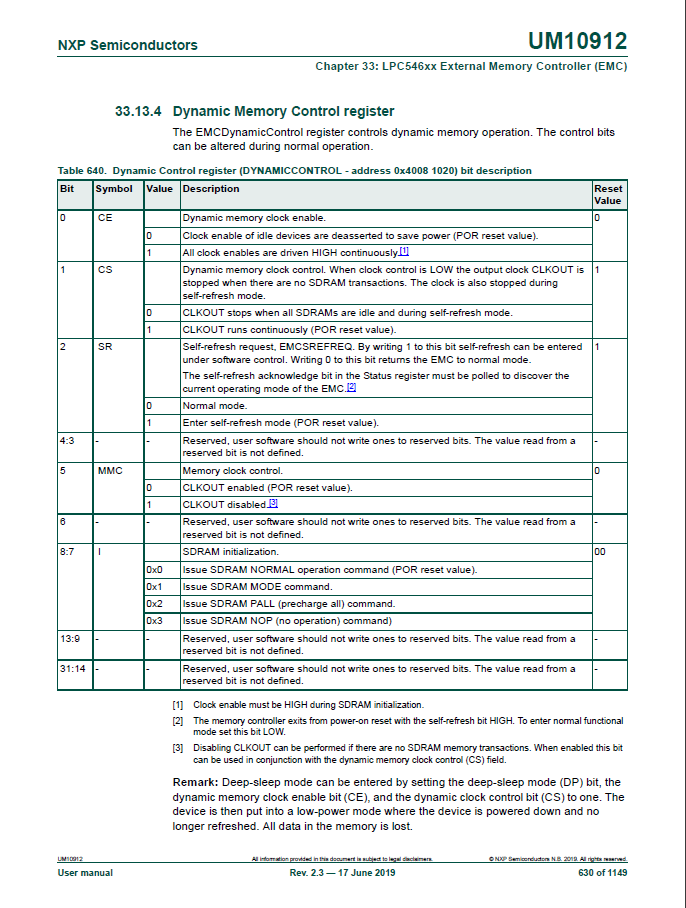

In the user manual (UM10912) it states that the external memory controller (EMC) can put the connected device into low power mode. See remark at the bottom of the attached page. I am able to set the CE and CS bits using the fsl_emc driver included in the SDK, but where is the DP bit and how does one set it?

I have tried the following functions prior to putting the LPC device to sleep, but results in terms of current consumption are not consistent.

EMC_EnableDynamicMemControl(EMC, true);

EMC_EnterSelfRefreshCommand(EMC, true);

EMC_EnterLowPowerMode(EMC, true);

I am using Micron SDRAM. According to their datasheet, power-down requires a CKE high to low transition while all banks are idle. Do I need to ensure that all banks are idle before the above commands? If so, what is the best way to achieve that?

LPC54607

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Matt,

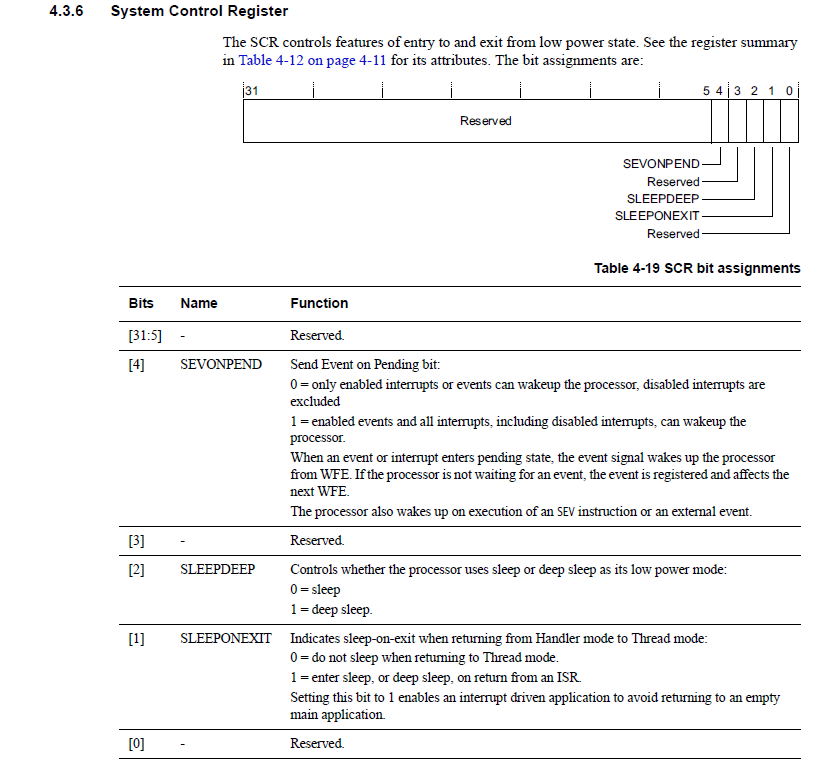

I suppose that the Deep Sleep bit is located at the SCR register, which is part of the Cortex-M4 core registers.

You can use the structure to access the bit:

SCB->SCR|=1<<2;

The SCB is defined in core_cm4.h if you use SDK package.

Hope it can help you

BR

XiangJun Rong

typedef struct

{

__IM uint32_t CPUID; /*!< Offset: 0x000 (R/ ) CPUID Base Register */

__IOM uint32_t ICSR; /*!< Offset: 0x004 (R/W) Interrupt Control and State Register */

__IOM uint32_t VTOR; /*!< Offset: 0x008 (R/W) Vector Table Offset Register */

__IOM uint32_t AIRCR; /*!< Offset: 0x00C (R/W) Application Interrupt and Reset Control Register */

__IOM uint32_t SCR; /*!< Offset: 0x010 (R/W) System Control Register */

__IOM uint32_t CCR; /*!< Offset: 0x014 (R/W) Configuration Control Register */

__IOM uint8_t SHP[12U]; /*!< Offset: 0x018 (R/W) System Handlers Priority Registers (4-7, 8-11, 12-15) */

__IOM uint32_t SHCSR; /*!< Offset: 0x024 (R/W) System Handler Control and State Register */

__IOM uint32_t CFSR; /*!< Offset: 0x028 (R/W) Configurable Fault Status Register */

__IOM uint32_t HFSR; /*!< Offset: 0x02C (R/W) HardFault Status Register */

__IOM uint32_t DFSR; /*!< Offset: 0x030 (R/W) Debug Fault Status Register */

__IOM uint32_t MMFAR; /*!< Offset: 0x034 (R/W) MemManage Fault Address Register */

__IOM uint32_t BFAR; /*!< Offset: 0x038 (R/W) BusFault Address Register */

__IOM uint32_t AFSR; /*!< Offset: 0x03C (R/W) Auxiliary Fault Status Register */

__IM uint32_t PFR[2U]; /*!< Offset: 0x040 (R/ ) Processor Feature Register */

__IM uint32_t DFR; /*!< Offset: 0x048 (R/ ) Debug Feature Register */

__IM uint32_t ADR; /*!< Offset: 0x04C (R/ ) Auxiliary Feature Register */

__IM uint32_t MMFR[4U]; /*!< Offset: 0x050 (R/ ) Memory Model Feature Register */

__IM uint32_t ISAR[5U]; /*!< Offset: 0x060 (R/ ) Instruction Set Attributes Register */

uint32_t RESERVED0[5U];

__IOM uint32_t CPACR; /*!< Offset: 0x088 (R/W) Coprocessor Access Control Register */

} SCB_Type;

#define SCS_BASE (0xE000E000UL)

#define SCB_BASE (SCS_BASE + 0x0D00UL)

#define SCB ((SCB_Type *) SCB_BASE )

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the response, but the SCR bit control you are describing is for the main micro controller (Cortex-M) sleep mode. I am specifically trying to use the LPC's external memory controller to place the external SDRAM in sleep or lowest possible power state. I do not need to preserve any data in the external SDRAM in this case.

This statement from the manual implies that the DP bit is in the EMCDynamicControl register:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Matt,

It is said that bit 13 in EMC Control register is DP bit, but in UM10912, it is "Reserved".

Pls refer to the ticket:

https://community.nxp.com/message/753832?commentID=753832#comment-753832

Hope it can help you

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In my case, it seems bit 13 is not having any effect. I cannot fully isolate power to the SDRAM in my system, but with either of the following I can get power consumption to very low levels most(*) of the time:

Option A:

EMC->DYNAMICCONTROL |= 0x00002007; /* set DP, CE, CS, and SR bits */

EMC_Deinit(EMC);

// Bit 13 (DP) does not seem to have any effect, but it is required to set bit 2 (SR)

Option B (use library functions):

EMC_EnableDynamicMemControl(EMC, true);

EMC_EnterSelfRefreshCommand(EMC, true);

EMC_Deinit(EMC);

Note that Option B is equivalent to Option A without bit 13.

(*) Less than half the time, I see an increased current consumption of about ~3mA @ 3.3V. This may be due to one of the other peripherals in the system. I have not yet been able to isolate all of those and confirm they are in their lowest power states.