- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Priorities of the channels of the LPC82x MRT timer

Priorities of the channels of the LPC82x MRT timer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all,

I am using two channels of the MRT timer with the "Repeat interrupt mode" to run two different part of my code at different rates. My question is: how is the priority handled between two channels of the MRT timer? for instance I have MRTch1 running at 1kHz (with 2us of execution time) and MRTch2 running at 10kHz (with 40us of execution time), how can I make MRTch1 at higher priority than MRTch2?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As you know that the all MRT channels share the same interrupt vector for LPC82x, in other words, all MRT channels enter the same ISR, there is not priority concept for different MRT channels.

In the ISR, you have to check the MRT->IRQ_FLAG register to know the interrupt source and take action for different flag.

Assume two interrupt events of MRT module happen, the LPC82x will enter ISR, both flags in the MRT->IRQ_FLAG will be set, you can take action in the ISR for the two interrupt events

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As you know that the all MRT channels share the same interrupt vector for LPC82x, in other words, all MRT channels enter the same ISR, there is not priority concept for different MRT channels.

In the ISR, you have to check the MRT->IRQ_FLAG register to know the interrupt source and take action for different flag.

Assume two interrupt events of MRT module happen, the LPC82x will enter ISR, both flags in the MRT->IRQ_FLAG will be set, you can take action in the ISR for the two interrupt events

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok I see now.

Is there the possibility to have the sct timer generating a pwm on a given pin with a given duty cycle and to have an interrupt triggered on the rising and falling edges of that pwm?

Best regarda

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

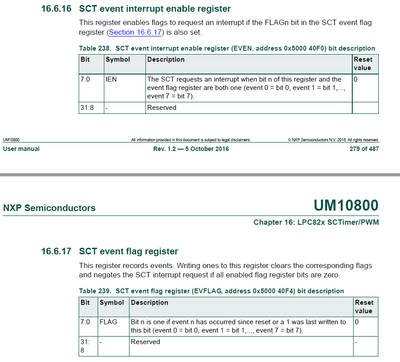

Of course, only events can trigger interrupt for the SCT module.

You can set the corresponding bits in SCT->EVEN register to enable a specific event generate interrupt.

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry for this follow up

so I will try to have the SCT timer creating a pwm and triggering an interrupt at each rising and falling edges of the pwm. Does the SCT timer have an interrput priority higher than the MRT timer? can I modify the priority order?

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I suggest you generate PWM with edge-alignment mode, so the rising edge and falling edge are controlled by different events for SCTimer module. Each event can fire an interrupt.

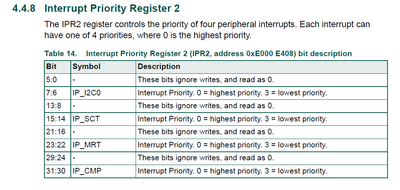

As you know that the SCTimer is interrupt source, the MRT is another interrupt source, each interrupt source has an independent 8 bits interrupt priority register, so you can program each interrupt source priority by programming the 8 bits interrupt priority register.

You can program IPR2 to configure the SCT and MRT interrupt priority.

I copy from UM10800.pdf

Hope it can help you

BR

XiangJun Rong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This sounds a good way forward!

How can I evaluate the jitter of the SCT timer? let's say that I would like to generate a 100Hz pwm with 30Mhz system clock. I set the ctrl and matchrel registers to get the 100Hz period

SCT0->CTRL|=(199<<5); // to get a 150kHz clock to SCT

SCT0->MATCHREL[0]=1500; // to get about 100Hz period

Which is the expected accurcay on the 100Hz frequency using the Internal IRC oscillator?

It seems that increasing the values of MATCHREL register increase the jitter of the PWM

Thanks

Best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

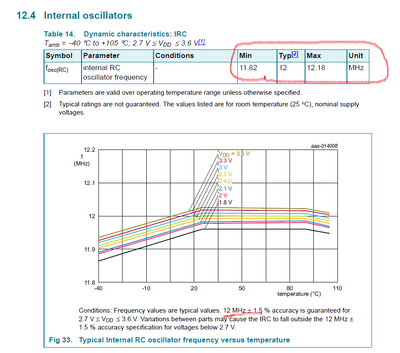

The PWM signal clock frequency accuracy is solely dependent on the IRC clock frequency accuracy, which is used to drive SCT module via PLL or not.

This is IRC clock frequency accuracy 12MHz+/-0.15% for LPC82x.

If the output PWM is 100Hz, the jitter will be 100Hz*(+/-1.5%), in other words, ranging from 98.5Hz to 101.5Hz.

Hope it can help you

BR

XiangJun Rong