- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

-

- Home

- :

- CodeWarrior

- :

- CodeWarrior for QorIQ

- :

- Re: Memory access failed

Memory access failed

Hi,

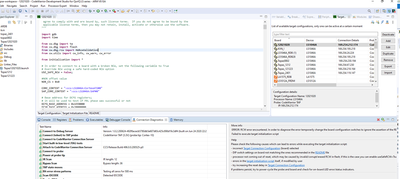

While bringing-up LS1046A-based custom board using CodeWarrior, we encounter “Memory access failed” error.

As shown in the target initialization file, we set the USE_SAFE_RCW = True; But, we got: Memory access fail.

"""

Copyright 2016 Freescale Semiconductor, Inc.

Copyright 2016-2019 NXP.

All Rights Reserved

This software is owned or controlled by NXP and may only be used strictly in accordance with the

applicable license terms. By expressly accepting such terms or by downloading, installing,

activating and/or otherwise using the software, you are agreeing that you have read, and that you

agree to comply with and are bound by, such license terms. If you do not agree to be bound by the

applicable license terms, then you may not retain, install, activate or otherwise use the software.

"""

import gdb

import time

from cw.dbg import ta

from cw.dbg import flash

from cw.dbg.rcw import HWRcwValidation

from cw.utils import cw_info, cw_warn, cw_error

from initialization import *

# In order to connect to a board with a broken RCW, set the following variable to True

# Override RCW using a safe hard-coded RCW option

USE_SAFE_RCW = True;

#NOR offset value

NOR_CS = 0x0

CORE_CONTEXT = ":ccs:LS1046A:CortexA72#0"

SAP_CORE_CONTEXT = ":ccs:LS1046A:SAP#0"

# Base address for DCFG registers;

# it will be used to test if PBL phase was successful or not

DCFG_BASE_ADDRESS = 0x1EE0000

DCSR_BASE_ADDRESS = 0x20000000

# Target access object

TA = ta.create()

###################################################################

# Prepare environment/convenience variables

###################################################################

def Prepare_Env():

set_init_params(context=CORE_CONTEXT, dcsr_addr=DCSR_BASE_ADDRESS)

gdb.execute("set $ddr_addr = 0x80000000")

gdb.execute("set $ocram_addr = 0x10000000")

###################################################################

# Reset

###################################################################

def Reset():

if USE_SAFE_RCW:

# Please make sure SERDES REF CLK is set to 100 MHz (SW4[1:2] = 00)

# Set rcw_src to the hard-coded RCW option matching the board's DIP SW

# regarding SYSCLK and differential/single-ended clock source

# use this when SYSCLK = 66 MHz, single-ended clock source

# TA.rcw.set_source(0x9A)

# use this when SYSCLK = 66 MHz, differential clock source

# TA.rcw.set_source(0x9B)

# use this when SYSCLK = 100 MHz, single-ended clock source

# TA.rcw.set_source(0x9E)

# use this when SYSCLK = 100 MHz, differential clock source

TA.rcw.set_source(0x9F)

# add here if you need to override other particular RCW values

# TA.rcw.set_data({1: 0x40282830, 9: 0x00C12980, 10: 0x00002580})

TA.rcw.apply()

else:

try:

user_reset = gdb.parse_and_eval("$reset")

user_reset_delay = int(gdb.parse_and_eval("$reset_delay"))

except gdb.error:

user_reset = 1

user_reset_delay = 0

if user_reset:

try:

gdb.execute("cw_reset %d" % user_reset_delay)

except gdb.error as exc:

# check if PBL phase was successful;

# note 1: target accesses must be executed through SAP core

# note 2: a PBL error can be detected only when RESET_REQ is set to 'Do nothing'

TA.set_context(SAP_CORE_CONTEXT)

HWRcwValidation(TA, DCFG_BASE_ADDRESS).check_for_pbl_error()

# if check_for_pbl_error does not detect the error, forward the initial exception

raise exc

Init_BRR()

# RCPM_CESRD sticky bit which will get set when you deassert EVT_B0

# REMOVE EXTERNAL DEBUG REQUEST which we issue in ccs on ccs::reset_to_debug

CCSR_BE_M(0x20160704, 0x80000000)

CCSR_BE_M(0x20160708, 0x80000000)

CCSR_BE_M(0x2016070C, 0x80000000)

# Safeguard against reset skid on CMSISDAP

# Clear PC

TA.reg.write(CORE_CONTEXT, "PC", 0)

# Clear MMU, caches, aligment checks, WNX in SCTLR_EL3

SCTLR_EL3 = TA.reg.read(CORE_CONTEXT, "SCTLR_EL3").to_int()

SCTLR_EL3 = SCTLR_EL3 & 0xFFF7EFF0

TA.reg.write(CORE_CONTEXT, "SCTLR_EL3", SCTLR_EL3)

###################################################################

# CCI Initialization

###################################################################

def Init_CCI():

# Set Terminate all barrier transactions bit of CCI-400 Control Register

# (needed for dsb instruction to succeed when doing coherent reads/writes)

# It will be disabled after DDR is initialized

CCSR_LE_M(0x01180000, 0x00000008)

# Enable snoop requests and DVM messages for A53 cluster slave interface 4

CCSR_LE_M(0x01185000, 0x00000003)

###################################################################

# Boot Release

###################################################################

def Init_BRR():

# TODO: when we can detect the current context,

# release all cores for SMP, current core for AMP

# First set the secondary cores to debug mode after release

DCSR_BE_M(0x16002C, 0x0000000E)

# Write to BRR to release cores

CCSR_BE_M(0x1EE00E4, 0x0000000F)

# Clear the halt request for the secondary cores

DCSR_BE_M(0x16001C, 0x0000000E)

# Make sure the gdb threads are refreshed just after the BRR initialization

TA.rc.refresh_threads()

# Make sure the cores are stopped

TA.rc.halt()

###################################################################

# DDR Initialization

###################################################################

def A008511_Erratum():

CCSR_BE_M(0x01080F94, 0x80000000)

def A009803_Erratum():

DDR_BASE = 0x01080000

# 1. Configure the DDR registers as normal with parity enabled

CCSR_BE_M(0x01080114, 0x00401070 | 0x00000020)

# 2. Set ERR_DISABLE[APED]

CCSR_BE_M(0x01080E44, 0x00 | 0x00000100)

# 3. Set DDR_SDRAM_CFG[MEM_EN]

CCSR_BE_M(0x01080110, 0x45200000 | 0x80000000)

# 4. Poll for DEBUG_2[30] to be set

while True:

time.sleep(0.2)

debug_2_value = CCSR_BE_D(DDR_BASE + 0xF04)

if debug_2_value & 0x2 != 0:

break

# 5. Clear ERR_DIS[APED]. Parity checking is now enabled

CCSR_BE_M(0x01080E44, 0x00 & (0xFFFFFFFF ^ 0x00000100))

def A009942_Erratum():

debug_29_value = CCSR_BE_D(0x01080F70)

debug_29_value |= 0x0070006F

CCSR_BE_M(0x01080F70, debug_29_value)

def Init_DDRC():

'''DDR controller initialization routine'''

#DDR_SDRAM_CFG

CCSR_BE_M(0x01080110, 0x45200000)

#CS0_BNDS

CCSR_BE_M(0x01080000, 0x7F)

#CS1_BNDS

CCSR_BE_M(0x01080008, 0x008000BF)

#CS2_BNDS

CCSR_BE_M(0x01080010, 0x00C000FF)

#CS3_BNDS

CCSR_BE_M(0x01080018, 0x0100013F)

#CS0_CONFIG

CCSR_BE_M(0x01080080, 0x80010312)

#CS1_CONFIG

CCSR_BE_M(0x01080084, 0x0202)

#CS2_CONFIG

CCSR_BE_M(0x01080088, 0x0202)

#CS3_CONFIG

CCSR_BE_M(0x0108008C, 0x0202)

#CS0_CONFIG_2

CCSR_BE_M(0x010800C0, 0x00)

#CS1_CONFIG_2

CCSR_BE_M(0x010800C4, 0x00)

#CS2_CONFIG_2

CCSR_BE_M(0x010800C8, 0x00)

#CS3_CONFIG_2

CCSR_BE_M(0x010800CC, 0x00)

#DDR_SDRAM_CFG_2

CCSR_BE_M(0x01080114, 0x00401070)

#DDR_SDRAM_MODE

CCSR_BE_M(0x01080118, 0x01010211)

#DDR_SDRAM_MODE_2

CCSR_BE_M(0x0108011C, 0x00)

#DDR_SDRAM_MODE_3

CCSR_BE_M(0x01080200, 0x00)

#DDR_SDRAM_MODE_4

CCSR_BE_M(0x01080204, 0x00)

#DDR_SDRAM_MODE_5

CCSR_BE_M(0x01080208, 0x00)

#DDR_SDRAM_MODE_6

CCSR_BE_M(0x0108020C, 0x00)

#DDR_SDRAM_MODE_7

CCSR_BE_M(0x01080210, 0x00)

#DDR_SDRAM_MODE_8

CCSR_BE_M(0x01080214, 0x00)

#DDR_SDRAM_MD_CNTL

CCSR_BE_M(0x01080120, 0x00000000)

#DDR_SDRAM_INTERVAL

CCSR_BE_M(0x01080124, 0x18600618)

#DDR_DATA_INIT

CCSR_BE_M(0x01080128, 0xDEADBEEF)

#DDR_SDRAM_CLK_CNTL

CCSR_BE_M(0x01080130, 0x02800000)

#DDR_INIT_ADDR

CCSR_BE_M(0x01080148, 0x00000000)

#DDR_INIT_EXT_ADDR

CCSR_BE_M(0x0108014C, 0x00000000)

#TIMING_CFG_0

CCSR_BE_M(0x01080104, 0x8055000C)

#TIMING_CFG_1

CCSR_BE_M(0x01080108, 0xBBB48E44)

#TIMING_CFG_2

CCSR_BE_M(0x0108010C, 0x0049111C)

#TIMING_CFG_3

CCSR_BE_M(0x01080100, 0x010C1000)

#TIMING_CFG_4

CCSR_BE_M(0x01080160, 0x00220001)

#TIMING_CFG_5

CCSR_BE_M(0x01080164, 0x04401400)

#DDR_ZQ_CNTL

CCSR_BE_M(0x01080170, 0x8A090705)

#DDR_WRLVL_CNTL

CCSR_BE_M(0x01080174, 0x86750609)

#DDR_SR_CNTR

CCSR_BE_M(0x0108017C, 0x00000000)

#DDR_WRLVL_CNTL_2

CCSR_BE_M(0x01080190, 0x090A0A0B)

#DDR_WRLVL_CNTL_3

CCSR_BE_M(0x01080194, 0x0B0C0C00)

#DDR_ERR_DISABLE

CCSR_BE_M(0x01080E44, 0x00)

#DDR_ERR_INT_EN

CCSR_BE_M(0x01080E48, 0x00)

#DDR_ERR_SBE

CCSR_BE_M(0x01080E58, 0x00010000)

#DDRCDR_1

CCSR_BE_M(0x01080B28, 0x80040000)

#DDRCDR_2

CCSR_BE_M(0x01080B2C, 0x81)

#DDR_SDRAM_CFG_3

CCSR_BE_M(0x01080260, 0x00)

#TIMING_CFG_7

CCSR_BE_M(0x0108016C, 0x13340000)

#TIMING_CFG_8

CCSR_BE_M(0x01080250, 0x02336800)

#DQ_MAP0

CCSR_BE_M(0x01080400, 0x32C57554)

#DQ_MAP1

CCSR_BE_M(0x01080404, 0xD4BB0BD4)

#DQ_MAP2

CCSR_BE_M(0x01080408, 0x2EC2F554)

#DQ_MAP3

CCSR_BE_M(0x0108040C, 0xD8000000)

#DDR_SDRAM_MODE_9

CCSR_BE_M(0x01080220, 0x0701)

#DDR_SDRAM_MODE_10

CCSR_BE_M(0x01080224, 0x04800000)

#DDR_SDRAM_MODE_11

CCSR_BE_M(0x01080228, 0x00)

#DDR_SDRAM_MODE_12

CCSR_BE_M(0x0108022C, 0x00)

#DDR_SDRAM_MODE_13

CCSR_BE_M(0x01080230, 0x00)

#DDR_SDRAM_MODE_14

CCSR_BE_M(0x01080234, 0x00)

#DDR_SDRAM_MODE_15

CCSR_BE_M(0x01080238, 0x00)

#DDR_SDRAM_MODE_16

CCSR_BE_M(0x0108023C, 0x00)

#DDR_SDRAM_RCW_3

CCSR_BE_M(0x010801A0, 0x00)

#DDR_SDRAM_RCW_4

CCSR_BE_M(0x010801A4, 0x00)

#DDR_SDRAM_RCW_5

CCSR_BE_M(0x010801A8, 0x00)

#DDR_SDRAM_RCW_6

CCSR_BE_M(0x010801AC, 0x00)

A008511_Erratum()

A009803_Erratum()

A009942_Erratum()

#Delay before enable

time.sleep(0.5)

#DDR_SDRAM_CFG [MEM_EN] = 1

#print "Enabling DDR controller"

CCSR_BE_M(0x01080110, 0xC5200000)

#wait for DRAM data initialization

time.sleep(0.5)

###################################################################

# IFC Initialization

###################################################################

def Init_IFC():

# CSPR_EXT

CCSR_BE_M(0x0153000C + NOR_CS * 12, 0x00000000)

# CSPR

CCSR_BE_M(0x01530010 + NOR_CS * 12, 0x60000101)

# AMASK

CCSR_BE_M(0x015300A0 + NOR_CS * 12, 0xF8000000)

# CSOR

CCSR_BE_M(0x01530130 + NOR_CS * 12, 0x00008000)

# IFC_FTIM0

CCSR_BE_M(0x015301C0 + NOR_CS * 48, 0xC0200410)

# IFC_FTIM1

CCSR_BE_M(0x015301C4 + NOR_CS * 48, 0x5000900E)

# IFC_FTIM2

CCSR_BE_M(0x015301C8 + NOR_CS * 48, 0x0410501C)

# IFC_FTIM3

CCSR_BE_M(0x015301CC + NOR_CS * 48, 0x00000000)

###################################################################

# QSPI Initialization

###################################################################

def Init_QSPI():

# QSPI_CFG

CCSR_BE_M(0x157015C, 0x20100000)

# SMPR

CCSR_BE_M(0x1550108, 0x00000000)

# QuadSPI_FLSHCR

CCSR_BE_M(0x155000C, 0x00000303)

# Set top address for each device

CCSR_BE_M(0x1550180, 0x44000000)

CCSR_BE_M(0x1550184, 0x48000000)

CCSR_BE_M(0x1550188, 0x4C000000)

CCSR_BE_M(0x155018C, 0x50000000)

# BUF0CR

CCSR_BE_M(0x1550010, 0x00000000)

# BUF3CR

CCSR_BE_M(0x155001C, 0x80000000)

# BFGENCR

CCSR_BE_M(0x1550020, 0x00000000)

# QuadSPI_MCR

CCSR_BE_M(0x1550000, 0x000f4000)

###################################################################

# Adds Flash devices for this board

###################################################################

def Config_Flash_Devices():

fl = flash.create(TA)

# Add QSPI device

fl.add_device({"alias": "qspi", "name": "MT25QU01GBBB", "address": 0x40000000, "ws_address": 0x10000000, "ws_size": 0x1FFFF, "geometry": "8x1", "controller": "QSPI"})

# Add eMMC device

fl.add_device({"alias": "mmc", "name": "SDINBDG4", "address": 0x00000000, "ws_address": 0x80000000, "ws_size": 0x1FFFF, "geometry": "8x1", "controller": "eSDHC"})

#set qspi as current device

fl.set_current_device("qspi")

###################################################################

# Detect DDR frequency

###################################################################

def Detect_DDR_Freq():

# Detect DDR data rate from RCWSR1

SYSCLK = 100

RCWSR1 = CCSR_BE_D(0x01ee0100)

MEM_PLL_RAT = (RCWSR1 & 0x3F0000) >> 16

# DDR freq in MT/s

DDR_freq = int(MEM_PLL_RAT * SYSCLK)

return DDR_freq

###################################################################

# L2 RAM Latency

###################################################################

def Config_L2_RAM_Latency():

# Initialize the L2 RAM latency

L2CTLR_EL1 = TA.reg.read(CORE_CONTEXT, "L2CTLR_EL1").to_int()

# Clear L2 Tag RAM latency and L2 Data RAM latency

L2CTLR_EL1 &= (~(0x000001C7))

# Set L2 data ram latency bits [2:0]

L2CTLR_EL1 |= 0x00000002

# Set L2 tag ram latency bits [8:6]

L2CTLR_EL1 |= 0x00000080

TA.reg.write(CORE_CONTEXT, "L2CTLR_EL1", L2CTLR_EL1)

###################################################################

# This is the actual function called by debugger, flash, etc.

###################################################################

def run_init_file():

Prepare_Env()

# Reset with RCW override option (USE_SAFE_RCW)

Reset()

Init_CCI()

#Init_IFC()

Init_QSPI()

DDR_freq = Detect_DDR_Freq()

Init_DDRC(DDR_freq)

Config_Flash_Devices()

Config_L2_RAM_Latency()When we set the USE_SAFE_RCW = False:

We got “RCW error encountered. In order to diagnose the error temporarily change the board configuration switches to ignore the assertion of the RESET_REQ_B signal. Please refer to board reference manual in order to locate the appropriate switch that controls this behaviour.

Could someone please help us to resolve the error?

Thank you for your support.

Regards,

Kavin

已解决! 转到解答。

The "DDR Initialization" section in CodeWarrior initialization file is only used for LS1046RDB demo board, you need to modify this section according to your custom board.

You could use QCVS DDR tool to assist you to calculate the DDR controller configuration parameters, then do validation and optimization to get the optimized parameters and use them in CW initialization file.

Please refer to https://www.nxp.com.cn/docs/en/user-guide/QCVS_DDR_User_Guide.pdf

If there is SPD on the target board, please use reading from SPD to create a DDR project. If no, please create a QCVS DDR project with default parameters, then modify Properties panel according to DDR datasheet.

Hello @Kavinravi

Were you able to resolve the issue you were facing?

Even i''m facing the same issue.

I hope you reply for this

Thank You.

Hi Dhanyalakshmi,

Yes, I modified the board initialization file as per our custom board configuration. This fixed the issue. Please use the DDR validation tool (https://www.nxp.com/docs/en/user-guide/QCVS_DDR_User_Guide.pdf) to generate the code for DDR.

If you have any questions, please create a support ticket with NXP, and they will guide you.

Thank you.

The "DDR Initialization" section in CodeWarrior initialization file is only used for LS1046RDB demo board, you need to modify this section according to your custom board.

You could use QCVS DDR tool to assist you to calculate the DDR controller configuration parameters, then do validation and optimization to get the optimized parameters and use them in CW initialization file.

Please refer to https://www.nxp.com.cn/docs/en/user-guide/QCVS_DDR_User_Guide.pdf

If there is SPD on the target board, please use reading from SPD to create a DDR project. If no, please create a QCVS DDR project with default parameters, then modify Properties panel according to DDR datasheet.