- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

A Walk Around the S32N55 Vehicle Super-Integration Processor Block Diagram

A Walk Around the S32N55 Vehicle Super-Integration Processor Block Diagram

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

Driven by automakers’ ambitions to reduce wiring costs, improve scalability and provide better pathways for software upgradeability, E/E architectures are rapidly evolving from traditional flat architectures to zonal architectures with central compute. The next generation of architectures for software-defined vehicles (SDVs) will be built around a central vehicle computer or controller running vehicle applications and/or real-time functions, while zone controllers and end nodes manage sensing and actuation.

NXP’s S32N55 device is the first in NXP’s new 5nm S32N family of vehicle super-integration processors for central compute applications. The S32N family offers a range of devices, with different combinations or real-time and applications processing, that act as the brain of an SDV. S32N devices provide the critical role of safe integration of many legacy and new cross-vehicle functions, along with the flexibility to adapt to new vehicle functions with software-defined, hardware-enforced partitioning in the future.

The S32N55 device targets the consolidation of real-time vehicle functions to implement a central vehicle controller, however, it could also be used as a high-performance domain controller. It offers market-leading real-time processing, advanced capabilities to isolate and manage multiple deterministic tasks, network acceleration to control real-time traffic, and security and safety modules to ensure overall proper operation.

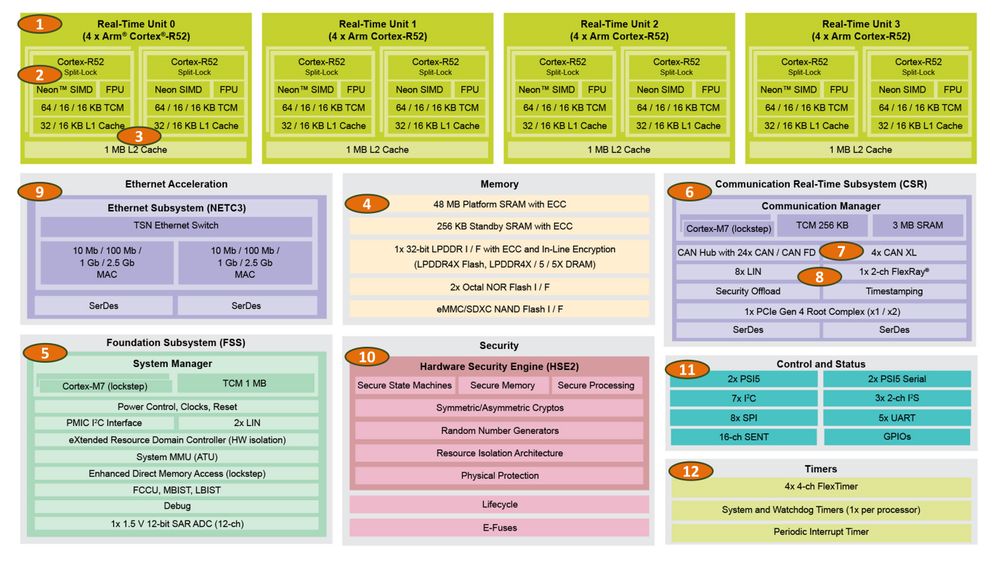

We will walk through the main modules and features shown in the S32N55 block diagram to explain them in more detail. Please note that the block diagram is a high-level representation of the device’s capabilities. For details on the device architecture and implementation, please refer to the S32N55 reference manual.

Real-Time Performance and Memory

(1) For real-time performance, the S32N55 offers 16 Arm® Cortex®-R52 processor cores that operate up to 1.2 GHz. These cores are arranged in four real-time units (RTUs) with four split-lock Arm Cortex-R52 cores. Split-lock means that each core in a pair can run independently (split), or in lockstep, where they run together. The Cortex-R52 cores can run in one of three configurations: 1) all cores in lockstep mode to offer the maximum ASIL D performance of nearly 20K DMIPS, 2) all cores in split mode to offer nearly 40K ASIL B DMIPS or 3) a combination of some of the cores in lockstep and split. It is expected that automakers will use mixed-critically in their consolidation of ECUs. Some vehicle functions will require a high level of functional safety and configure cores in lockstep mode, while other tasks may not be functional safety-critical and configure other cores in split mode.

(2) Each Cortex-R52 core also includes an Arm Neon™ single instruction, multiple data (SIMD) processing unit to help execute advanced control algorithms.

(3) The S32N55 RTUs also have tightly-coupled memory (TCM), L1 cache, L2 cache and direct access to 48 MB of platform SRAM on the device to reduce latency and support fast execution of multiple real-time applications. All memory is protected with error correction code (ECC) as part of the functional safety support.

(4) For memory expansion, the S32N55 offers a flexible range of memory interfaces: LPDDR4x Flash, LPDDR4X/5/5X DRAM and SDXC/eMMC NAND flash. These memory interfaces allow for OTA update support with execute-in-place (XiP) options with the LPDDR4X flash and LPDDR DRAM. SPI NOR flash is supported for booting.

Real-Time Application Isolation

The S32N55 consolidates real-time vehicle functions that previously have been implemented as separate ECUs with their own microcontrollers. Each integrated electronic control unit (iECU) runs in its own isolation execution environment to ensure freedom from interference from other functions. Each iECU is assigned a collection of hardware resources including processing, memory, peripherals and I/Os, or what we call “core-to-pin” isolation, to provide an isolated environment similar to a separate physical ECU. Each iECU can independently run, be suspended or put in a safe state. Individual iECUs can be reset without impacting others. This allows an iECU in a failure state to reset at run time without impacting the wider system. It also allows each iECU to be updated over time independently.

(5) The management of the iECUs is handled by the foundation subsystem (FSS). The FSS has a system manager, running on a dual-core lockstep pair of Cortex-M7 processor cores, which securely handles resource partitioning amongst the iECUs using the extended resource domain controller (XRDC) for hardware isolation. The system manager provides high-level system control services (clocks, reset and power) and handling shared resource events. The FSS also acts as a safety manager and addresses safety context, fault detection, fault reaction, fault recovery and built-in self-test. There is also support for a 12-channel, 12-bit SAR A/D converter.

Communication and Ethernet Acceleration

(6) The communication real-time subsystem (CRS) combines vehicle networking, PCI Express (PCIe) and legacy automotive peripheral functionality into a single subsystem. A communication manager, running on a dual-core lockstep pair of Cortex-M7 processor cores, safely assists in management of shared resources, diagnostics and calibration.

(7) A CAN Hub with 24 CAN/CAN FD modules virtualizes CAN I/O and allows applications to share the same CAN I/O pins. CAN frames can be routed to multiple iECUs. The CAN Hub also provides efficient filtering and routing between iECUs and the Cortex-M7 offloads CAN handling from the host core.

(8) A rich set of additional communication peripherals are available in the CRS, including 4 CAN XL, 8 LIN, 2-channel FlexRay, PCIe Gen 4 Root Complex (x1/x2 lanes) and high-speed SerDes (x2 lanes) interfaces.

(9) The S32N55 has an Ethernet subsystem module (NETC3) to manage Ethernet traffic. This is the same NETC3 module on NXP’s existing S32Z2/E2 family of real-time processors for compatibility. The module includes an integrated time-sensitive networking (TSN) Gigabit Ethernet switch with two Ethernet MACs operating up to 2.5Gbps. The inclusion of the Ethernet switch removes the need for an external switch and helps reduce overall system costs. MII, RMII, RGMII, SGMII and SGMII 2.5G / OC SGMII Ethernet interfaces are all supported. Two additional SerDes lanes are also available to run SGMII.

Security

(10) The S32N55 main security module is NXP’s 2nd generation hardware security engine (HSE2). This security module builds upon the robust and proven hardware security engine that is available on today’s NXP S32G2/G3 and S32Z2/E2 devices. The HSE2 offers an isolated secure execution environment providing the platform root-of-trust (RoT) for other functionalities within the chip. The security module provides general system security administration (secure boot/execution, resource partitioning, debug access and secure firmware updates), hardened cryptographic operations and key provisioning/distribution operations. The HSE2 has security state machines, secure processing and memory and other cryptography hardware to manage these tasks. It integrates physical protection support to resist side-channel attacks and supports the security lifecycle of the device.

The HSE2 is connected by a dedicated TrustBus to crypto engines distributed in other modules on the device. These additional crypto engines manage high-performance cryptographic operations, secure communication and secure content access (on-the-fly encryption and decryption). This distributed security approach has the benefits of increased availability of security services, increased parallelism of security operations, clearer prioritization between tasks and minimized latency.

Control and Status

(11) The control and status module manages additional communication and GPIO peripherals. This includes a broad mix of peripherals including PSI5, I2C, I2S, SPI, UART, SENT and many GPIOs.

Timers

(12) General purpose timers on the S32N55 include FlexTimers, periodic interrupt timer and system and watchdog timers.

Summary

The S32N55 vehicle super-integration processor is ideal for integration of many real-time vehicle functions or integrated ECUs. Each iECU can be allocated an isolation execution environment whose resources can be changed over the life of the vehicle as needed. This provides automakers with the ability to develop iECUs more rapidly, facilitates migration of vehicle functions across the vehicle and streamlines a lifetime of vehicle enhancements. The S32N55 provides a key role of streamlining the safe integration of real-time vehicle functions for SDVs.

For additional information on NXP’s S32N55 vehicle super-integration processor, please visit www.nxp.com/S32N55.

You must be a registered user to add a comment. If you've already registered, sign in. Otherwise, register and sign in.

-

101

6 -

communication standards

4 -

General Purpose Microcontrollers

19 -

i.MX RT Processors

45 -

i.MX Processors

43 -

introduction

9 -

LPC Microcontrollers

73 -

MCUXpresso

32 -

MCUXpresso Secure Provisioning Tool

1 -

MCUXpresso Conig Tools

30 -

MCUXpresso IDE

40 -

MCUXpresso SDK

25 -

Model-Based Design Toolbox

6 -

MQX Software Solutions

2 -

QorIQ Processing Platforms

1 -

QorIQ Devices

5 -

S32N Processors

4 -

S32Z|E Processors

6 -

SW | Downloads

4

- « Previous

- Next »