# **Getting Started with Pins Tool User's Guide**

**Document Number: PINSGS**

Rev. 0, 05/2016

## **Contents**

| Section number                        | Title                      | Page |

|---------------------------------------|----------------------------|------|

|                                       | Chapter 1<br>Introduction  |      |

| 1.1 Features                          |                            | 5    |

| 1.2 Conventions                       |                            | 6    |

| 1.3 Versions                          |                            | 6    |

| 1.4 Tool localization                 |                            | 8    |

|                                       | Chapter 2<br>Example Usage |      |

|                                       | Chapter 3<br>Configuration |      |

| 3.1 Creating a new configuration      |                            | 17   |

| 3.2 Saving a configuration            |                            | 19   |

| 3.3 Opening an existing configuration |                            | 20   |

|                                       | Chapter 4 Pins Tool        |      |

| 4.1 Selecting Pins tool               |                            | 23   |

| 4.2 Pins routing principle            |                            | 23   |

| 4.3 User interface                    |                            | 24   |

| 4.3.1 Package                         |                            |      |

| 4.3.2 Routed Pins view                |                            | 29   |

| 4.3.3 View controls                   |                            | 30   |

| 4.3.4 Filtering routed pins           |                            | 31   |

| 4.3.5 Highlighting and color codi     | ing                        |      |

| 4.3.6 Filtering in the Pins view      |                            | 34   |

| 4.3.7 Functions                       |                            | 35   |

| 4.3.8 Peripherals view                |                            | 37   |

| 4.3.9 Pins table                      |                            | 39   |

| 4.3.10 Power groups                   |                            | 41   |

| Se  | ction  | number                    | Title                          | Page |

|-----|--------|---------------------------|--------------------------------|------|

|     | 4.3.11 | Registers view            |                                | 42   |

| 4.4 | Errors | and warnings              |                                | 43   |

|     | 4.4.1  | Incomplete routing        |                                | 44   |

| 4.5 | Code g | generation                |                                | 45   |

|     | 4.5.1  | Exporting source code     |                                | 47   |

|     | 4.5.2  | Importing source code     |                                | 48   |

| 4.6 | Option | 18                        |                                | 49   |

|     | 4.6.1  | Configuration preferences |                                | 49   |

|     | 4.6.2  | Pins properties           |                                | 50   |

|     | 4.6.3  | Updates                   |                                | 51   |

|     |        |                           | Chapter 5<br>Advanced Features |      |

| 5.1 | Switch | ning processor            |                                | 53   |

| 5.2 | Export | ting pins table           |                                | 55   |

|     |        |                           | Chapter 6                      |      |

Support

# Chapter 1 Introduction

The Pins tool is a part of the NXP Configuration Tools, a suite of evaluation and configuration tools that helps users from first evaluation to production software development. The Pins tool is an easy-to-use way to configure the pins of the device. The Pins tool software enables you to create, inspect, change, and modify any aspect of the pin configuration and muxing of the device. This document introduces you to the Pins tool. It describes the basic components of the tool and lists the steps to configure and use the tool to configure the pins.

### NOTE

The Pins tool software is available in Web and desktop versions. For i.MX processors currently only the desktop version is available.

# 1.1 Features

The Pins tool is designed for:

- Configuration of pin routing/muxing

- Managing different functions used for routing initialization

- Configuration of pin functional/electrical properties

- Generation of code for routing and functional/electrical properties

The Pins tool can be used to define routing of pins for target device/board. The tool configuration may be shared using the stored configuration or by using the generated C file (via Import/ Export or via copy-paste of the generated source). The following sections describe the parts of the Pins tool.

## **NOTE**

The tool generates code for routing pin to peripheral, but not for the configuration of the peripheral. Some peripherals might need additional configuration of the pin to assign function or channel. For example, for some ADC - the routing provide connection between pin and the ADC peripheral. You can then assign the ADC channel from within the ADC peripheral.

## 1.2 Conventions

The following conventions are used in this document.

Table 1-1. Conventions used in the document

| Icon     | Description                                                               |  |

|----------|---------------------------------------------------------------------------|--|

|          | Indicates that the content is related to the desktop version of the tool. |  |

| 逾        | Indicates that the content is related to the Web version of the tool.     |  |

| <b>,</b> | Indicates useful tips.                                                    |  |

# 1.3 Versions

The suite of these tools is called NXP Configuration Tools. These tools are provided as an online Web application or as a desktop application.

For Kinetis, the tools are referred as Kinetis Expert Tools and they are available both as Web and desktop applications.

For i.MX, the tool is referred as Pins Tool for i.MX Processors and is available as a desktop application only.

### NOTE

The desktop version of the tool contacts the NXP server and fetches the list of the available processors. Once used, the processors data is retrieved on demand.

To use the desktop tool in the offline mode, create a configuration for the given processor while online. The tool will then store the processors locally in the user folder and enable faster access and offline use.

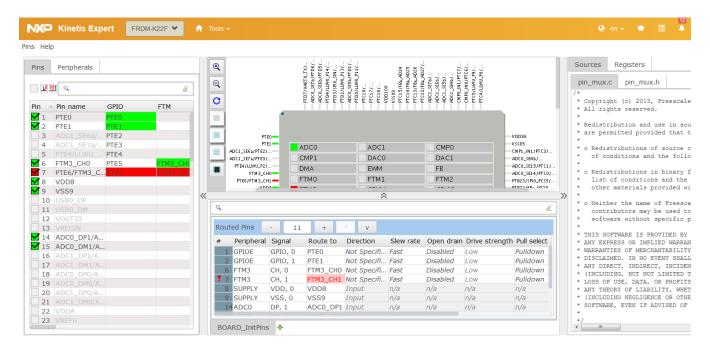

Figure 1-1. Web version

Pins tool for i.MX Processors is available as desktop application only.

#### Tool localization

Figure 1-2. Desktop version

## 1.4 Tool localization

The Pins Tool supports English and Chinese languages, based on your locale settings.

To manually set the locale, add the following parameter to the command line:

tools.exe -nl zh

It is possible to set the locale in the tools.ini file by adding the following line:

-Duser.language=zh

The supported languages are:

- en English

- zh Chinese

### NOTE

Setting your system locale to Chinese will automatically launch the tool with localized Chinese menu items, tool tips, and help.

# **Chapter 2 Example Usage**

This section lists the steps to create an example pin configuration, which then can be used in a project.

In this example, three pins (UART0\_RX, UART0\_TX and PTB21) on a board are configured.

The steps are listed both for the desktop and the Web version.

## **NOTE**

The Web version exists only for the Kinetis devices.

You can the use the generated files with the application code.

- 1. For the **desktop** version, launch the tool with the shortcut present in the installation folder.

- 2. For the **Web** version visit <a href="http://kex.nxp.com">http://kex.nxp.com</a> and select the Pins tool.

Figure 2-1. Select the Pins tool

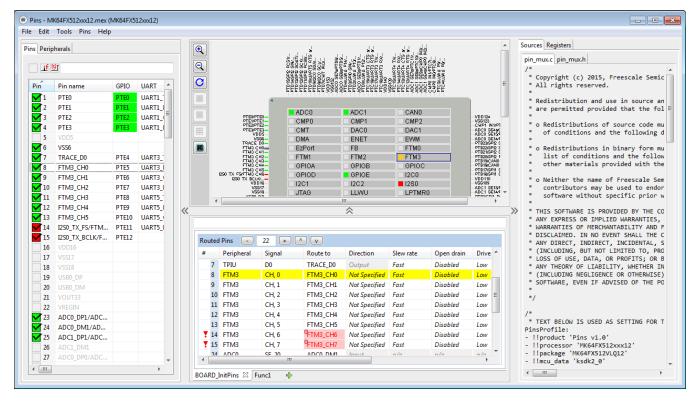

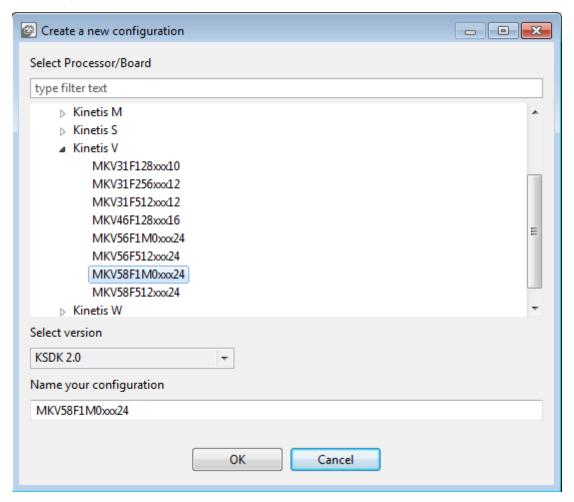

3. In the **desktop** version, create a new configuration with the menu **File > New** and select the processor/board you want to use.

Figure 2-2. Create a new configuration

Optionally, name the configuration to match your project.

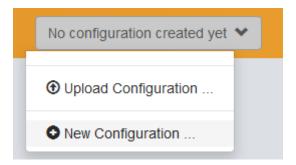

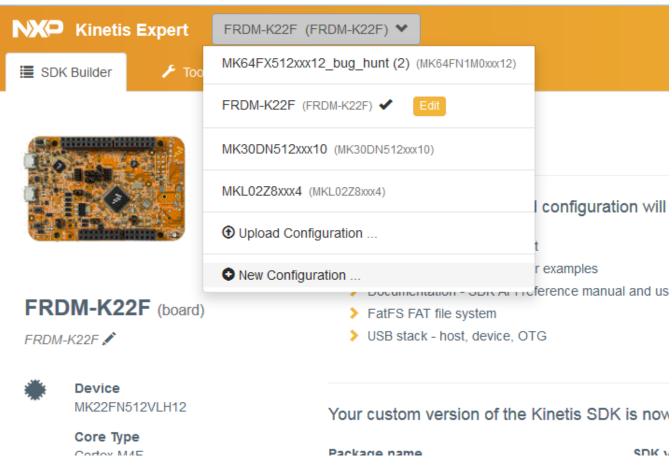

- 4. In the Web version:

- a. Select an existing configuration or create a new configuration.

Figure 2-3. New Configuration

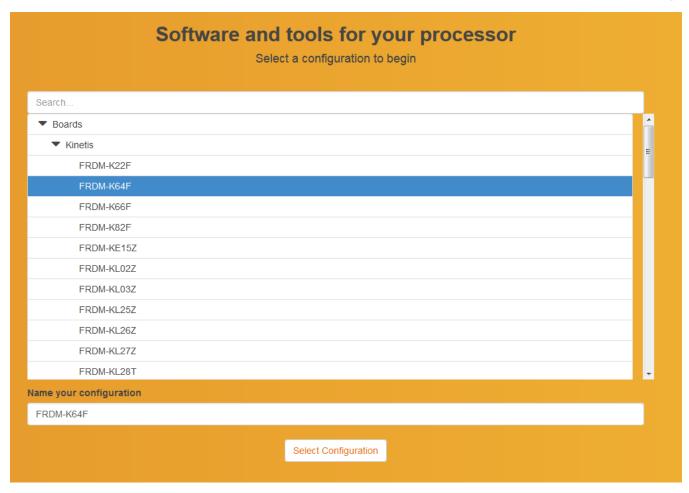

b. For a new configuration, select the board and the configuration.

11

Figure 2-4. Select a configuration to begin

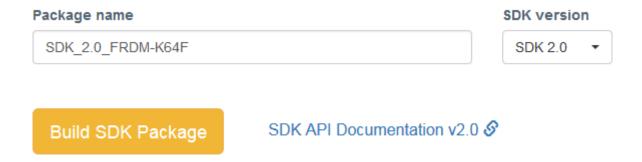

c. Create the SDK package for the configuration.

Figure 2-5. Build SDK Package

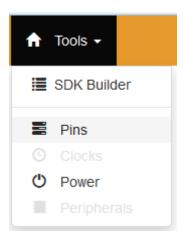

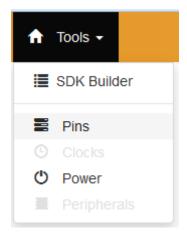

d. After creating a new configuration, switch to the Pins tool.

Figure 2-6. Switch to Pins tool

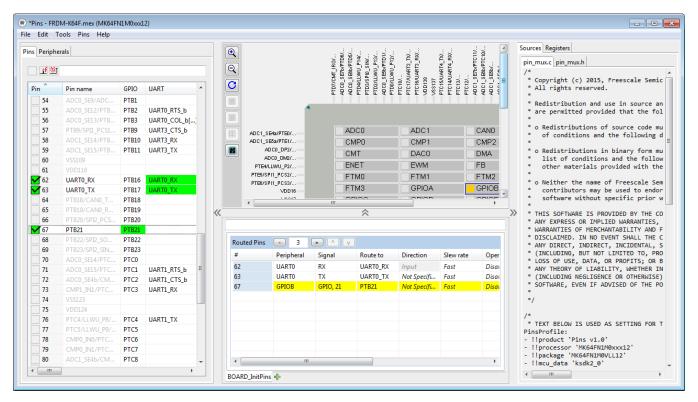

5. In the **Pins** view on the left, select the UARTO\_RX and TX signals and the PTB21 GPIO. For this, you can click into the cells to make them 'green'.

Figure 2-7. Switch to Pins tool

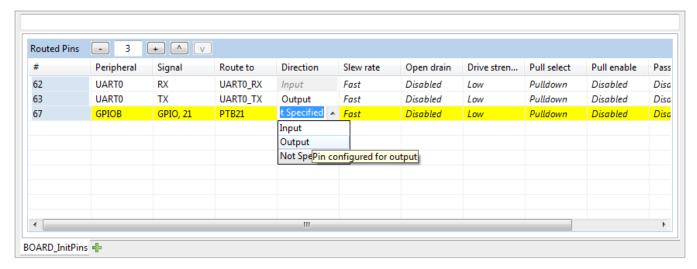

6. In the middle view, called the Routed Pins table, select **Output** for the TX and PTB21 signals.

Figure 2-8. Select output

7. The Pins tool automatically generates the source code for pin\_mux.c and pin\_mux.h on the right panel.

```

Sources Registers

pin_mux.c pin_mux.h

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR THE PINS TOOL ***

#include "fsl common.h"

#include "fsl port.h"

#include "pin_mux.h"

#define PIN16 IDX

16u /*!< Pin number for pin 16 in a pc

#define PIN17_IDX

17u /*!< Pin number for pin 17 in a pc

21u /*!< Pin number for pin 21 in a pc

#define PIN21 IDX

0x00u /*!< UART 0 transmit data source s

#define SOPT5 UART0TXSRC UART TX

* TEXT BELOW IS USED AS SETTING FOR THE PINS TOOL ******************************

BOARD InitPins:

- options: {coreID: singlecore, enableClock: 'true'}

- {pin_num: '62', peripheral: UARTO, signal: RX, pin_signal: PTB16/SPI1_SOUT/L

- {pin_num: '63', peripheral: UARTO, signal: TX, pin_signal: PTB17/SPI1_SIN/UA

- {peripheral: GPIOB, signal: 'GPIO, 21', pin_signal: PTB21/SPI2_SCK/FB_AD30/C

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR THE PINS TOOL ***

*/

* Function Name : BOARD InitPins

* Description : Configures pin routing and optionally pin electrical features

void BOARD_InitPins(void) {

/* Port B Clock Gat

CLOCK EnableClock(kCLOCK PortB);

PORT_SetPinMux(PORTB, PIN21_IDX, kPORT_MuxAsGpio);

/* PORTB21 (pin 67)

SIM->SOPT5 = ((SIM->SOPT5 &

/* Mask bits to zer

(~(SIM SOPT5 UARTOTXSRC MASK)))

SIM_SOPT5_UARTØTXSRC(SOPT5_UARTØTXSRC_UART_TX)

/* UART 0 transmit

}

```

Figure 2-9. Generated code

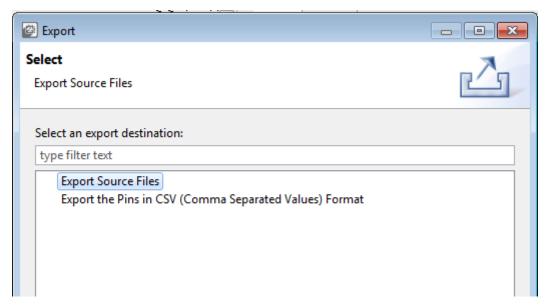

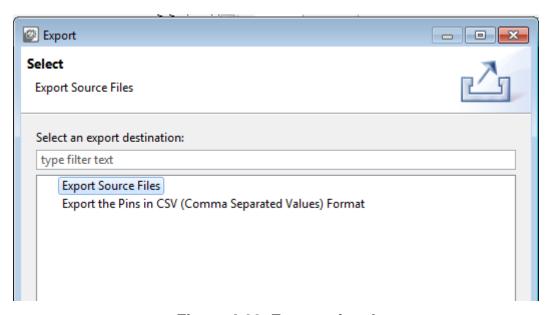

8. You can now copy-paste the content of the source(s) to your application and IDE. Alternatively, you can export the generated files. To export the files: select the menu **File > Export** (in the desktop version) or select the menu **Pins > Export** menu (in the Web version). In the **Export** dialog, select the **Export Source Files** option.

Figure 2-10. Export Source Files

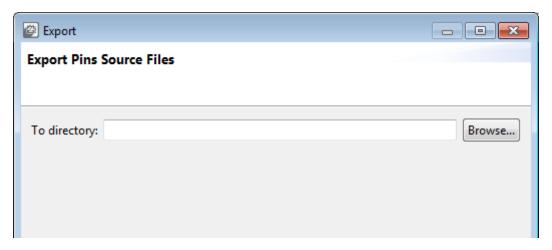

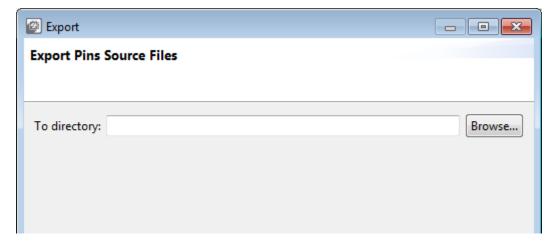

9. Click **Next** and specify the directory where you want to store the files.

Figure 2-11. Exported Pins Source Files

- 10. Click **Finish** to export the files.

- 11. Integrate and use the exported files in your application as source files.

Congratulations, you have created the configuration for your pins!

The following sections in this User's Guide describe the features of the tool in detail.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

# **Chapter 3 Configuration**

Configuration stands for common tools settings stored in .mex file. This file contains settings of all available tools and can be used in both web and desktop versions.

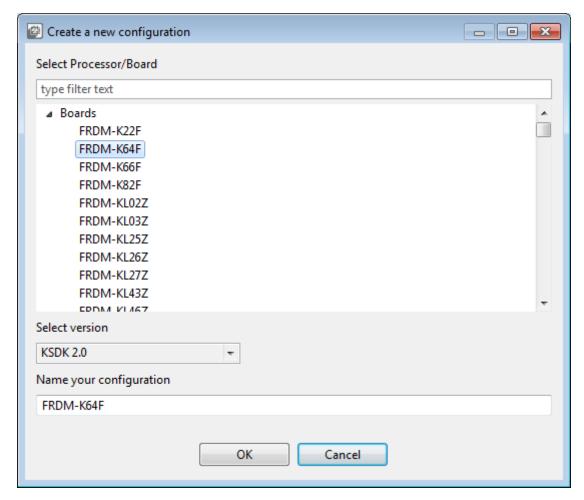

# 3.1 Creating a new configuration

To create a new configuration:

- 1. If the Pins tool is already open, select the **File > New** command.

- The Select a configuration to begin dialog box appears.

- 2. Expand the list of family and select the desired processor.

#### Creating a new configuration

Figure 3-1. Select a processor

Alternatively, type the name of the processor in the Search Processor text box and select the processor from the filtered results.

- 3. To specify a different name for your configuration, edit the text in the Name your configuration dialog box.

- 4. Click the OK button.

The selected configuration appears in the Pins tool. You can now configure the device.

5. You can now add the peripheral, package, and pins you want to configure and assigns/configure the muxing for the selected pins.

## NOTE

You can create a new configuration from the drop-down menu on the top of the Web page.

Figure 3-2. Drop-down menu on the Web page

# 3.2 Saving a configuration

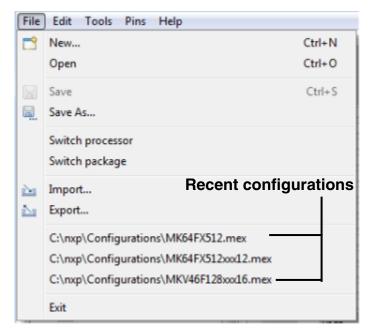

To save a configuration or a profile, select **File > Save As**.

#### Opening an existing configuration

Figure 3-3. Save configuration

## NOTE

In the desktop version, the configuration gets stored with a .mex file extension.

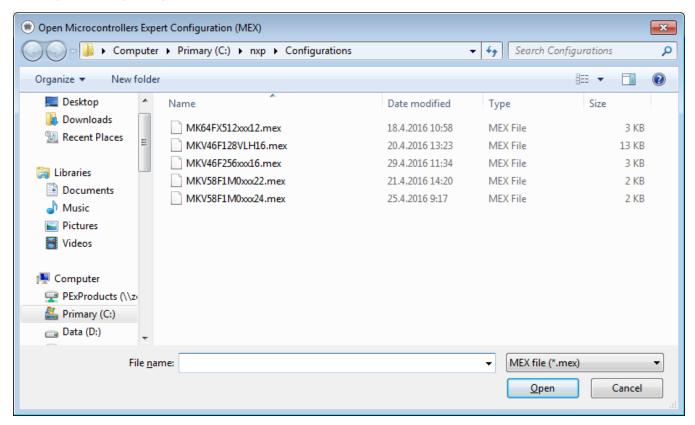

# 3.3 Opening an existing configuration

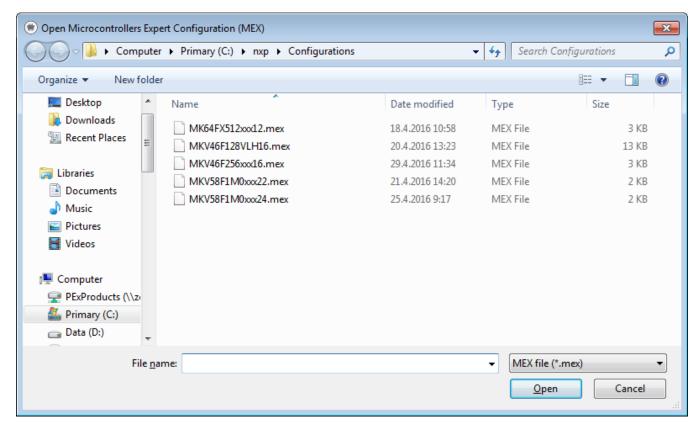

To open a previously saved profile:

1. Select **File > Open**.

Figure 3-4. Open profile

The Open profile dialog box appears.

2. Navigate to the folder where the previous profile has been saved.

Figure 3-5. Open dialog box

3. Select the profile and click Open.

## Opening an existing configuration

The existing profile appears in the Pins tool.

# Chapter 4 Pins Tool

This chapter describes the Pins tool principle and its use to generate the routing and muxing for pins.

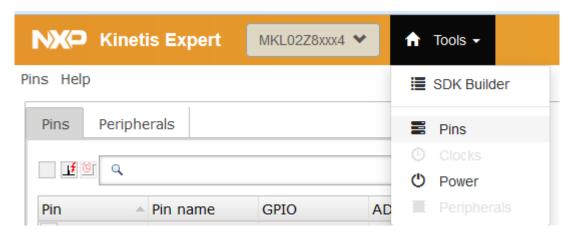

# 4.1 Selecting Pins tool

Select the Pins tool either via menu or by using shortcut installed on the desktop version.

Figure 4-1. Selecting Pins Tool - Desktop

Figure 4-2. Selecting Pins Tool - Web

**User interface**

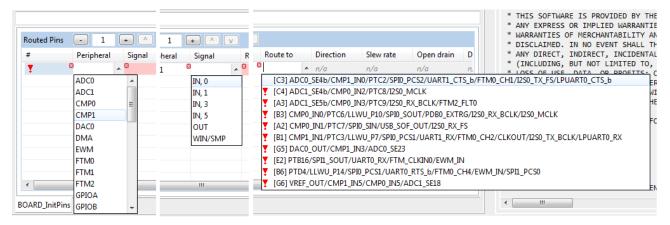

# 4.2 Pins routing principle

The Pins tool is designed to configure routing of signals from peripherals either to pins or to internal signals.

To define routing path, select:

- 1. Peripheral

- 2. Signal

- 3. Pin

Figure 4-3. Defining routing path

For the selected **Peripheral**, select one of the available signals.

Route the selected **Signal** to the desired pin.

Select one of non-conflicting/available pins. Once you have selected **Peripheral**, **Signal**, and **Route to**, the pin configuration is done. Later, it is also possible to configure the pin electrical features.

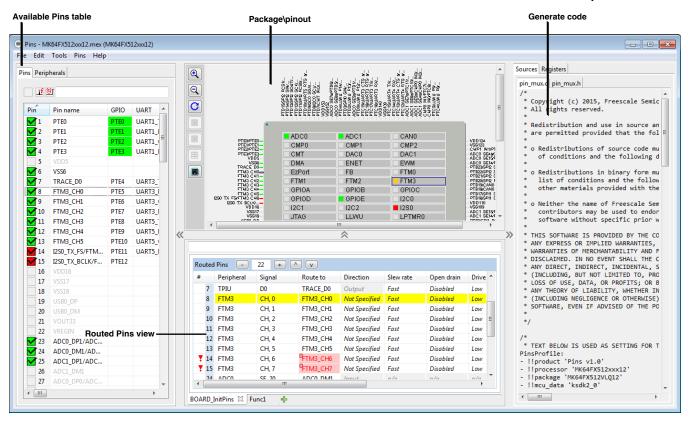

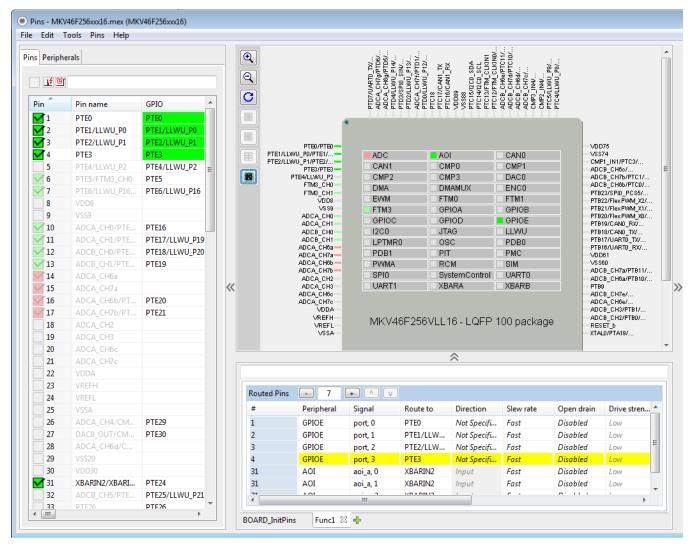

## 4.3 User interface

The Pins tool consists of several views.

#### **Chapter 4 Pins Tool**

Figure 4-4. Pins tool user interface

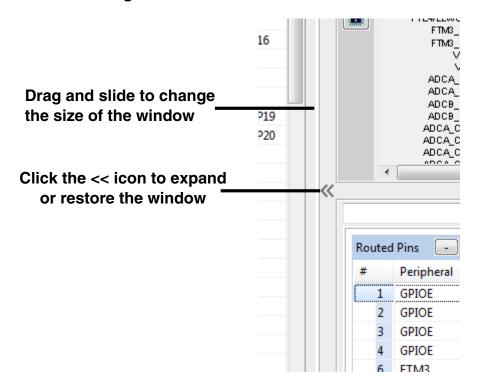

Figure 4-5. Resizing/restoring window

**User interface**

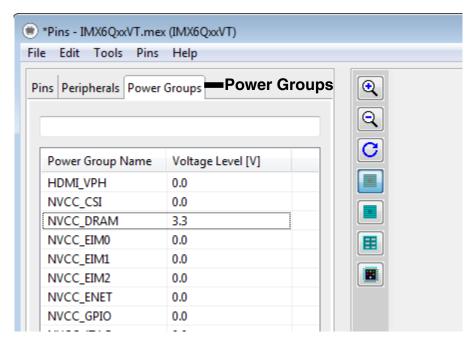

Figure 4-6. Selecting power group

## **NOTE**

Power Groups are not supported for all processors.

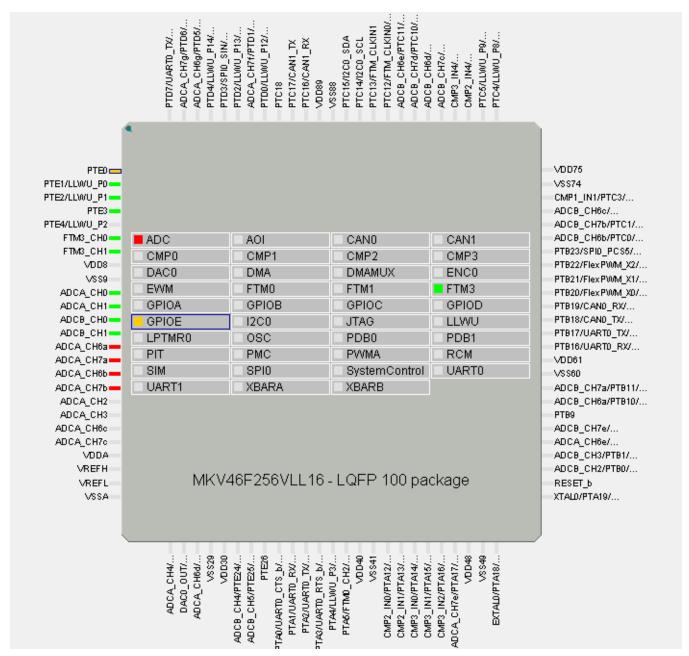

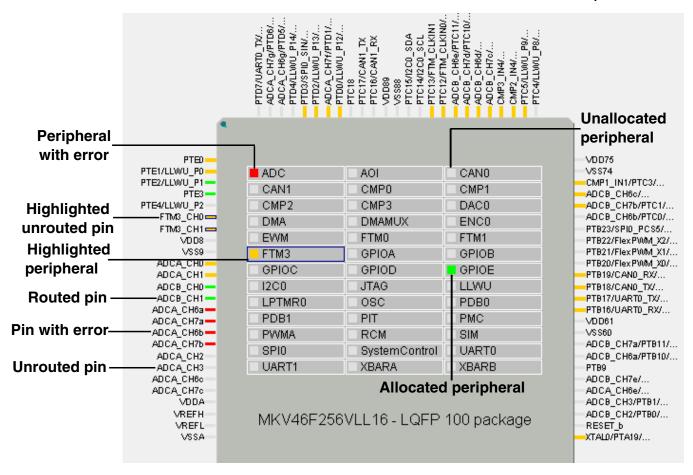

# 4.3.1 Package

The processor package appears in the middle of the Pins tool window. The processor package shows an overall overview of the package including the resources allocation.

This view shows Package overview with pins location. In the middle there are peripherals.

For BGA packages, use the **Show Peripherals** icon to see it.

Green color indicates the routed pins/peripherals.

Gray color indicates that the pin/peripheral is not routed.

The view also shows the package variant and the description (type and number of pins).

### **User interface**

The following icons are available in the toolbar:

Table 4-1. Toolbar options

| Icon | Description                                                                                 |

|------|---------------------------------------------------------------------------------------------|

| Q    | Zoom in package image.                                                                      |

| Q    | Zoom out package image.                                                                     |

| C    | Rotate package image.                                                                       |

|      | Show pins as you can see it from the bottom. This option is available on BGA packages only. |

|      | Show pins as you can see it from the top. This option is available on BGA packages only.    |

|      | Show peripherals. This option is available on BGA packages only.                            |

|      | Switch package.                                                                             |

## **NOTE**

Depending on the processor package selected, not all views are available.

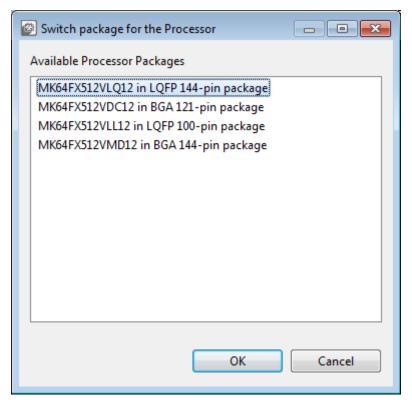

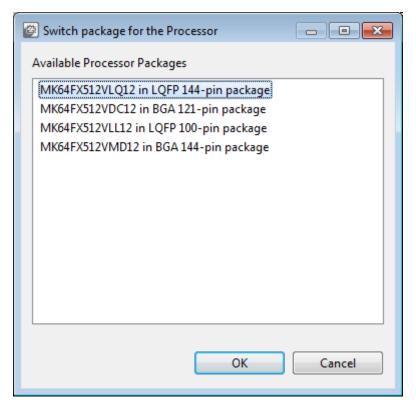

The Switch package icon launches the Select package for the Processor dialog box.

Figure 4-7. Switch package

The **Switch package for the Processor** dialog shows list of available processor packages, showing package type and number of pins.

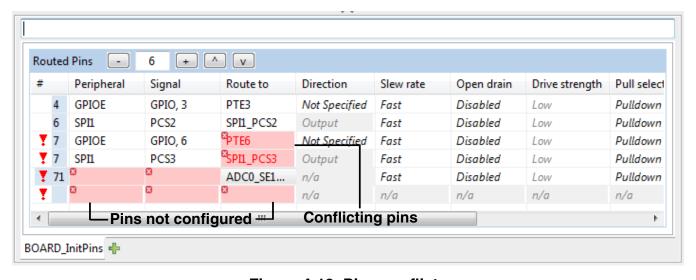

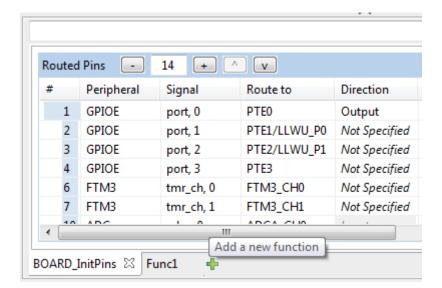

## 4.3.2 Routed Pins view

This **Routed Pins** view shows a list of routed pins and allows configuration. This view also allows the configuration of the electrical properties of pins and displays all the pins. It displays the pad configuration available in a configuration where each pin is associated with the signal name and the function.

## NOTE

The electrical features are configured only for pins in the table. For example, the routed pins.

The table is empty when the new project is created, which means no pin configured. Each row represents configuration of one pin and if there are no conflicts, the code is immediately updated.

Use the table drop down menu to configure the pin. To configure pins, start from left to right – select the peripheral first, then select required signal, and finally select the routed pin.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

#### **User interface**

See the right part of the table to configure the electrical features.

If the feature is not supported, n/a is shown.

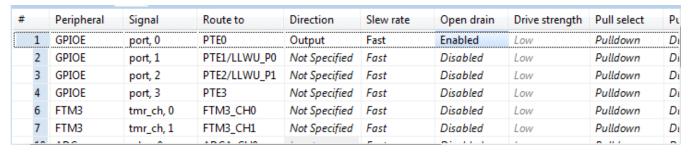

Figure 4-8. Routed Pins view

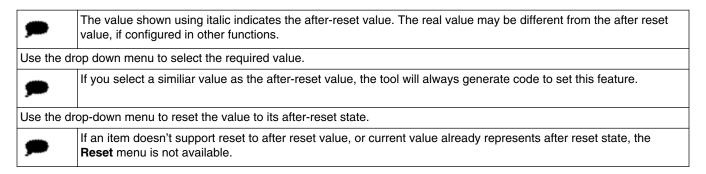

The gray background indicates the read-only items.

The italic value indicates that the value is not configured and it shows the after-reset value and no code is generated, so the configuration relies on the after reset value.

The first row shows pin number or coordinate on BGA package.

## 4.3.3 View controls

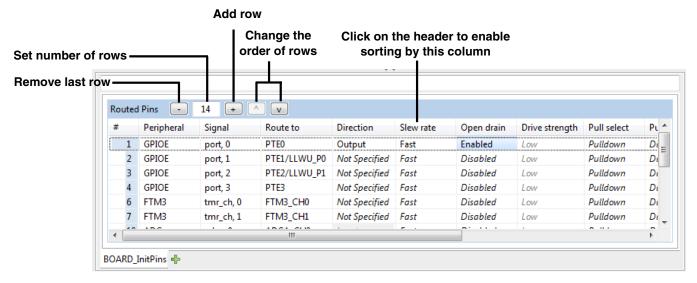

The following figure illustrated the Routed pins view controls.

Figure 4-9. View controls

### Add / remove rows:

- To add a new row to the end of table, click on the [+] icon.

- To remove the last row, click on the [-] icon.

- To delete a specific row or insert a new row at a given position, right-click and use the pop-up menu commands.

## Add a specific number of rows or clear the table:

- To add a specific number of rows, specify the exact number of rows.

- To clear the table, type 0.

## Change the order of the rows:

To change the order of the rows, use the arrow icons to move one row up or down.

# 4.3.4 Filtering routed pins

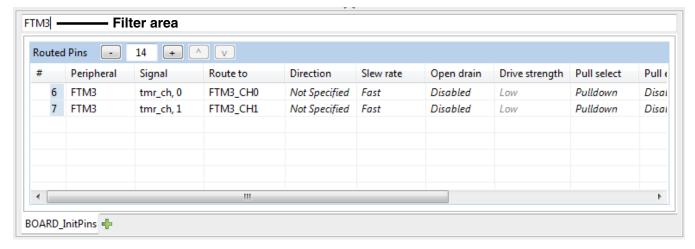

The following image illustrated the filter are of the **Routed Pins** view.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

#### **User interface**

Figure 4-10. Filter area

To instantly filter rows, type the text or the search phrase in the filter area.

## NOTE

When you enter the search text, it also searches the text in the full pin names displays rows that contain the search text.

# 4.3.5 Highlighting and color coding

It is possible to easily identify routed pins/peripherals on the package using highlighting. By default, the current selection (pin/peripheral) is highlighted in the package view.

- Error (red) indicates that the pin has an error.

- Used (green) indicates that the pin is muxed.

- Not used (light grey) indicates that the pin is available for mux, but is not muxed.

- Selected (yellow border around the pin such that the other color is still visible) indicates that the pin is selected. For example, by peripheral or by pin.

Figure 4-11. Highlighting and color coding

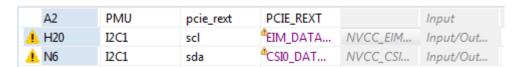

Figure 4-12. Pins conflicts

Figure 4-13. Warnings

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

#### **User interface**

- Package view

- Click on the peripheral or use the pop-up menu to highlight peripherals:

- and all allocated pins (to selected peripheral)

- or all available pins if nothing is allocated yet

- Click on the pin or use the pop-up menu to highlight the pin and the peripherals.

- Click outside the package to cancel the highlight.

- Peripherals/pins view

- Peripheral and pin behaves as described above image

- Keyboard can be used for (multiple) selection. This works only for Desktop version.

Figure 4-14. Pins tool interface

Desktop version of the too highlights pins during the drop-down menu traversal on pins

# 4.3.6 Filtering in the Pins view

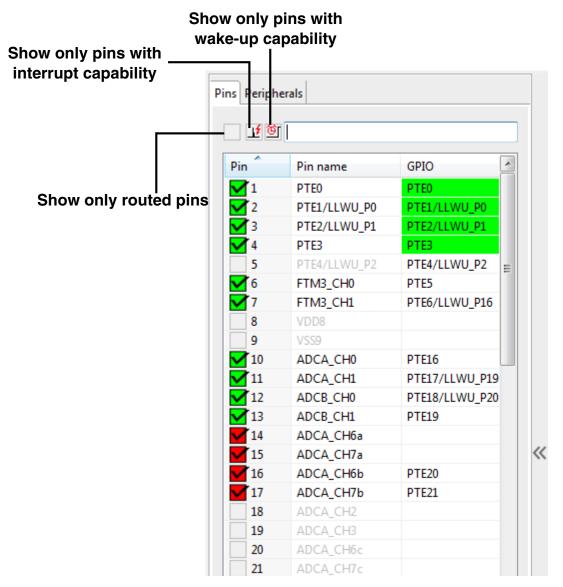

The following image illustrates the filtering controls in the Pins view.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

Figure 4-15. Filtering Controls

Type any text to search across the table. It will search for the pins features, like wake-up feature, or the low-power feature.

To see only pins on the selected peripheral, click on the header to sort pins for given peripheral by name.

Click on the first checkbox icon to see all or the routed pins only.

## 4.3.7 Functions

'Functions' are used to group a set of routed pins, and it will create code for the configuration in a function which then can be called by the application.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

#### **User interface**

The tool creates multiple functions that can be used to configure pin muxing.

Figure 4-16. Routed pins

The tool does not limit nor indicate the usage of pins in each function. Each function can define a set of routed pins or re-configure already routed pins.

When multiple functions are specified in the configuration, the package view primarily shows the pins and the peripherals for the selected function. Pins and peripherals for different functions are shown with light transparency and cannot be configured, until switched to this function.

Figure 4-17. Pins and peripherals

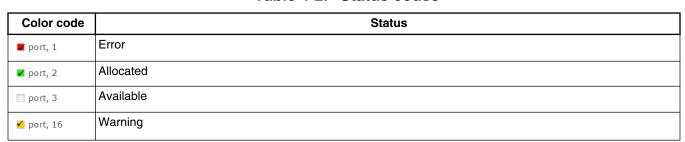

## 4.3.8 Peripherals view

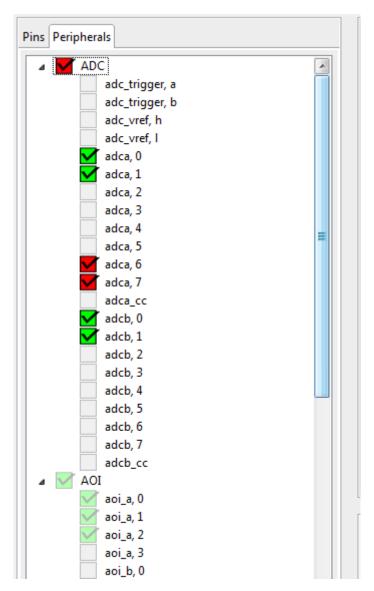

The **Peripherals** view shows a list of peripheral and its signals. Only the **Peripherals** and **Pins** view shows the checkbox (allocated) with status.

Table 4-2. Status codes

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

Figure 4-18. Peripherals tab

Use the checkbox to route/unroute the selected pins.

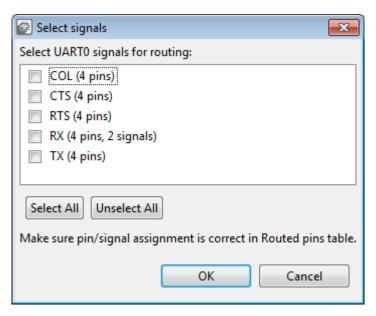

To route/unroute multiple pins, click on the peripheral and select the options in the Select signals dialog box.

Figure 4-19. Select signals dialog box

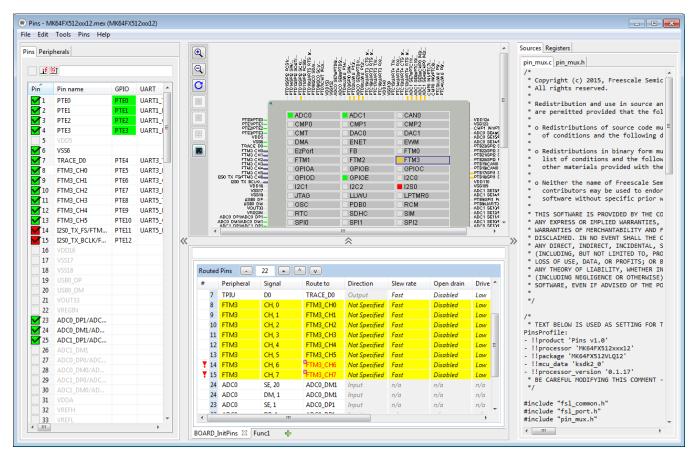

## 4.3.9 Pins table

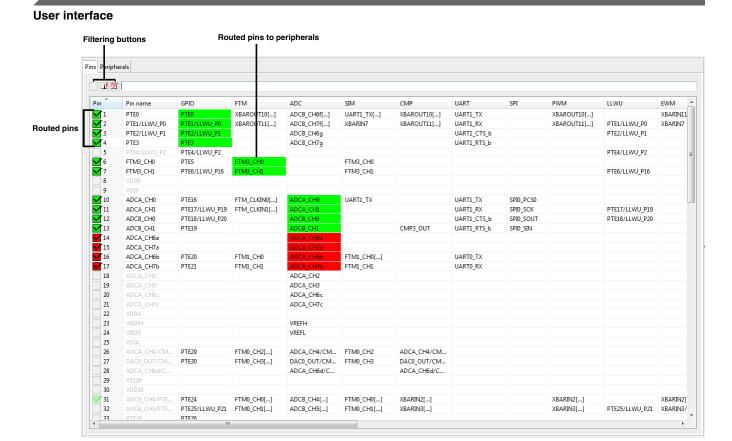

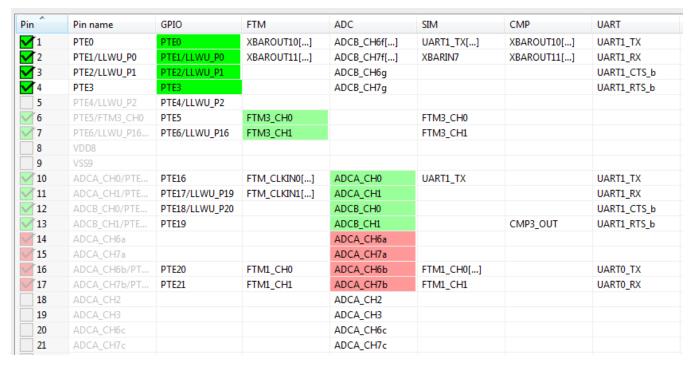

The **Pins** table view shows all the pins in a tabular format.

Figure 4-20. Pins table view

This view shows the list of all the pins available on a given device. The **Pin name** column shows the default name of the pin, or if the pin is routed. The pin name is changed to show appropriate function for selected peripheral if routed. The next columns of the table shows peripherals and pin name(s) on given peripheral. Peripheral with few items is cumulated in the last column.

To route/un-route pin to the given peripheral, click in the cell of the table. Routed pins are marked with checkbox and green color. Colored cells indicates pin is routed to given peripherals. If there is conflict in routing, red color is used.

Unroute is possible by clicking on given cell, or by checkbox in the first column.

Every routed pin appears in the Routed pins table.

When multiple functions specified in the configuration, the pins table view shows pins for selected function primarily. Pins for different functions are shown with light transparency and can't be configured, until switched to this function.

Figure 4-21. Example of routing mutiple functions

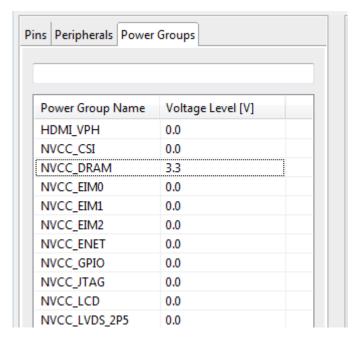

## 4.3.10 Power groups

If processor supports power groups, an additional tab will appear next to Pins and Peripherals allowing configuration of it.

#### NOTE

This feature is not supported for all the devices.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

Figure 4-22. Selecting power group

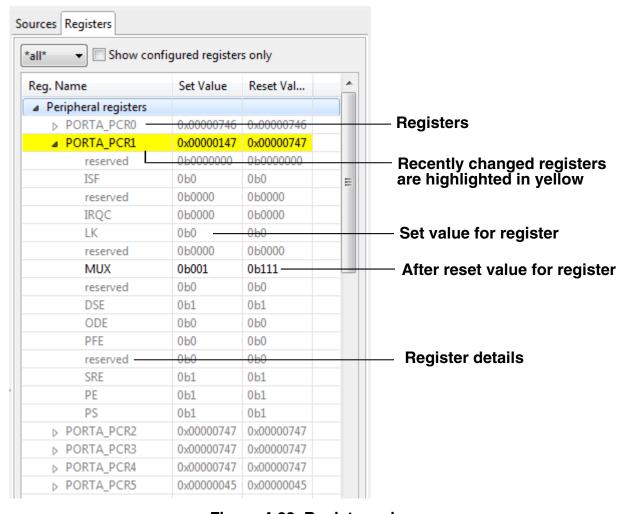

## 4.3.11 Registers view

The **Registers** view shows the list of registers of a given peripheral. The view shows the register name, the value used for routing configuration, and the after-reset values. This value is written into the register or bit by the generated code during the initialization process of the application. It is the last value that is written by the routing function to the register. The reset column contains the value that is in the register by default after the reset. The values of the registers are displayed in the hexadecimal and binary form. If the value of the register (or bit) is not defined, an interrogation mark "?" is displayed instead of the value.

Figure 4-23. Registers view

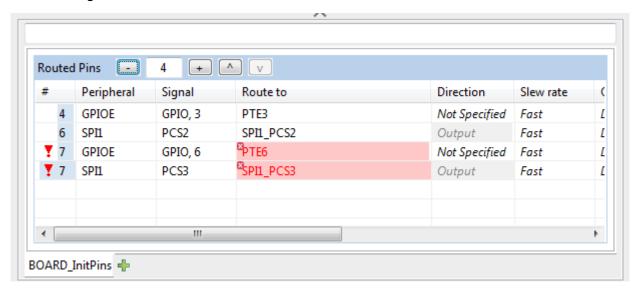

## 4.4 Errors and warnings

The pins tool checks for any conflict in the routing and also for errors in the configuration. Routing conflicts are checked only for the selected function. It is possible to configure different routing of one pin in different functions to allow dynamic pins routing re-configuration.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

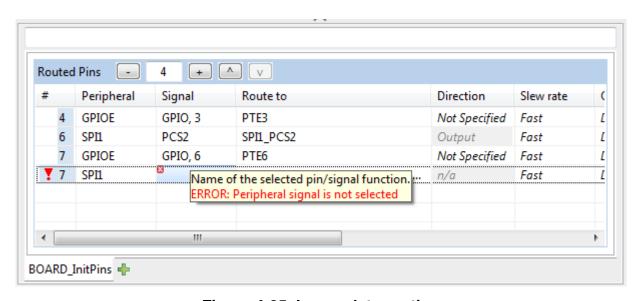

Figure 4-24. Error and warnings

If an error is encountered, the conflict is represented in the first column of the row and the error is indicated in the cell, where the conflict was created. The figure above shows the peripheral/ signal where the erroneous configuration occurs. The detailed error message appears as a tooltip.

## 4.4.1 Incomplete routing

Cell with incomplete routing is indicated by a red background. To generate proper pin routing, click on the drop down arrow and select the suitable value. Red decorator on a cell indicates an error condition.

Figure 4-25. Incomplete routing

45

The tooltip of the cell shows more details about the conflict or the error, typically it lists the lines where conflict occurs.

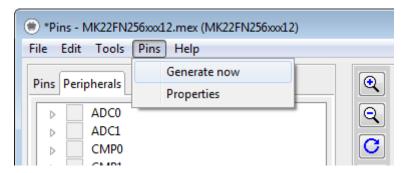

## 4.5 Code generation

The tool generates source code that can be incorporated into an application to initialize pins routing. The source code is generated automatically on change or can be invoked explicitly by selecting the main menu **Pins > Generate Now**.

Figure 4-26. Generate code

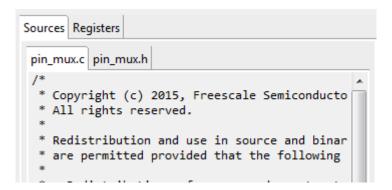

The generated code is shown in the **Sources** tab on the right window. It shows all generated files and each file has its own tab.

Figure 4-27. Sources view

It is also possible to copy and paste the generated code into the source files. The view generates code for each function. In addition to the function comments, the tool configuration is stored in YAML format. This comment is not intended for direct editing and can be used later to re-store the pins configuration.

#### Code generation

```

Sources Registers

pin_mux.c pin_mux.h

- !!processor_version '0.0.0'

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR THE PINS TOOL ***

#include "fsl_common.h"

#include "fsl_port.h"

#include "pin_mux.h"

3u /*!< Pin number for pin 3 in a port */

#define PIN3 IDX

#define PIN5 IDX

/*!< Pin number for pin 5 in a port */</pre>

#define PIN6 IDX

6u /*!< Pin number for pin 6 in a port */

BOARD InitPins:

- options: {coreID: singlecore, enableClock: 'true'}

- pin list:

- {pin_num: '4', peripheral: GPIOE, signal: 'GPIO, 3', pin_signal: ADC1_SE7a/PTE3/SPI1_S

- {pin_num: '6', peripheral: SPI1, signal: PCS2, pin_signal: PTE5/SPI1_PCS2/LPUART0_RX}

- {pin_num: '7', peripheral: GPIOE, signal: 'GPIO, 6', pin_signal: PTE6/SPI1_PCS3/LPUART

- {pin_num: '7', peripheral: SPI1, signal: '', pin_signal: PTE6/SPI1_PCS3/LPUART0_CTS_b/

* BE CAREFUL MODIFYING THIS COMMENT - IT IS YAML SETTINGS FOR THE PINS TOOL ***

* Function Name : BOARD InitPins

* Description : Configures pin routing and optionally pin electrical features.

void BOARD InitPins(void) {

/* There are conflicts or other incorrect settings in the configuration, the code below

those registers which are set correctly and without a conflict. Open this file in Pin

CLOCK EnableClock(kCLOCK PortE);

/* Port E Clock Gate Control:

PORT_SetPinMux(PORTE, PIN3_IDX, kPORT_MuxAsGpio);

PORT_SetPinMux(PORTE, PIN5_IDX, kPORT_MuxAlt2);

PORT_SetPinMux(PORTE, PIN6_IDX, kPORT_MuxAsGpio);

/* PORTE3 (pin 4) is configur

/* PORTE5 (pin 6) is configur

/* PORTE6 (pin 7) is configur

```

Figure 4-28. Generated code

YAML configuration contains configuration of each pin. It stores only non-default values.

## 4.5.1 Exporting source code

It is possible to export generate source using the Export wizard.

To launch the Export wizard:

- 1. Select **File > Export** from the main menu.

- 2. Select the **Export Source Files** option.

Figure 4-29. Export wizard

- 3. Click Next.

- 4. Select the target folder where you want to store the generated files.

Figure 4-30. Select target folder

5. Click Finish.

Web version offers download zip file containing all generated files.

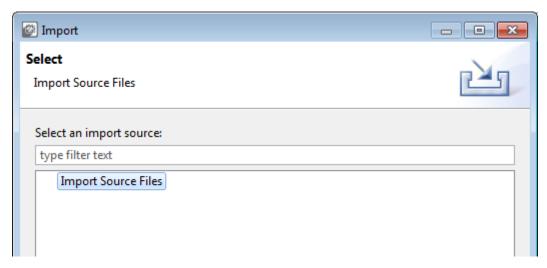

## 4.5.2 Importing source code

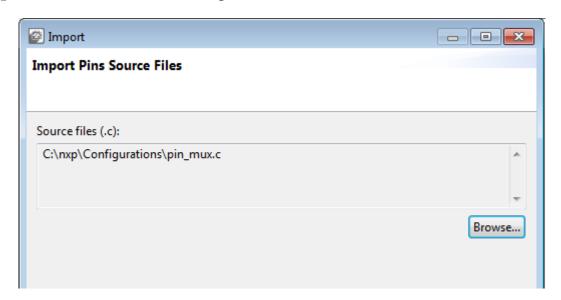

To import source code files:

1. Select **File > Import** from the main menu.

Figure 4-31. Import wizard

- 2. Select the **Import Source Files** option.

- 3. Click Next.

- 4. It is possible to select one or more C files to import using the **Browse** button in the **Import Pins Source Files** dialog box.

Figure 4-32. Import Pins Source Files

#### 5. Click Finish.

All files are merged into current configuration. It imports all the functions only. If imported function has the same name as in the existing configuration, it is automatically renamed to the indexed one. For example, if BOARD\_InitPins already exists in the configuration then the imported function is renamed to BOARD\_InitPins1.

Only C files with valid Yaml configuration can be imported. It imports the configuration only, then the whole C file is re-created based on this setting (the rest of the C file is ignored).

## 4.6 Options

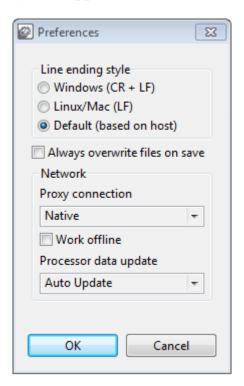

## 4.6.1 Configuration preferences

To configure preferences, select **Edit > Preferences** from the main menu. The configuration Preferences dialog box appears.

Figure 4-33. Preferences dialog box

In this dialog it is possible to set:

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

#### **Options**

- Line ending style (Windows, Linux or default based on host)

- Auto overwrite files on save behavior

- Proxy connection

- Direct direct network connection without any proxy.

- Native uses system proxy configuration for network connection.

- Work offline to enable this mode

- It will not download/update new data from NXP cloud, at it will not show all possible processors available for download if this feature is enabled.

- Processor data update options

- Update will be proceeded either automatically or manually (user has to confirm it when requested) or disabled at all.

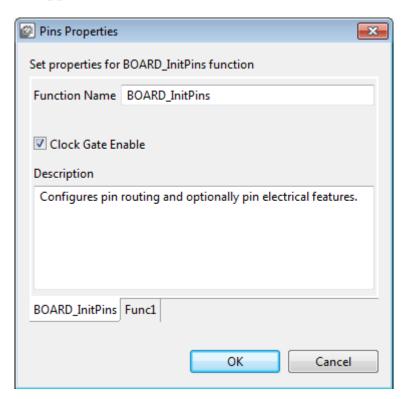

## 4.6.2 Pins properties

To set pins properties, select **Pins > Properties** from the main menu. The **Pins Properties** dialog box appears.

Figure 4-34. Pins Properties

In this option it is possible to configure several options for functions and code generation. Each settings is applicable for selected function, which can be specified by selecting appropriate tab. It is possible to specify generated function name, selected core\*, option to enable clock gate\* in source code, or write function description (this description will be generated in the C file). <sup>1</sup>

## 4.6.3 Updates

To perform a check for updates select **Help > Check** for the updates menu. It contacts the server and checks whether there is a new version available.

#### NOTE

To check updates, internet connection is required.

Getting Started with Pins Tool User's Guide, Rev. 0, 05/2016

<sup>1. \*</sup>if supported by processor

Options

## **Chapter 5 Advanced Features**

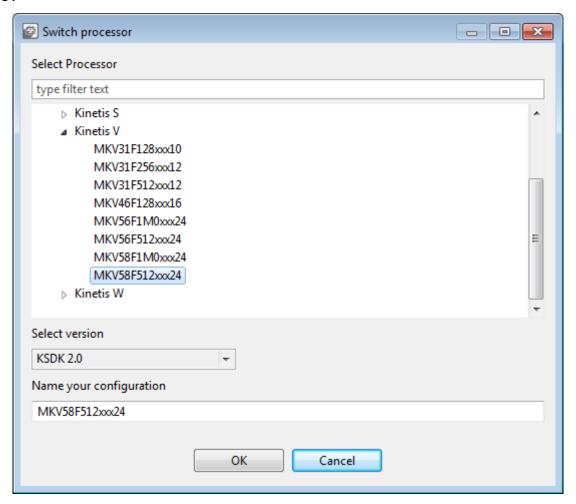

## 5.1 Switching processor

It is possible to switch processor or package of the current configuration to different one. If the processor or package is switched, all functions and configured routing of pins remains same, only applied on different processor. This is typically useful to change to similar packages. If switched to completely different processor, it may lead in many conflict or inaccessible pin routing. In this case, it is necessary go to Pins Routing table and re-configure all pins, which reports an error or conflicts.

Select **File > Switch processor** menu to change the processor in the selected configuration.

#### **Switching processor**

Figure 5-1. Switch configuration

Select **File > Switch package** menu to change package of current processor.

Figure 5-2. Switch package

#### **NOTE**

In order to switch processor in Web version, it is required to select top configuration menu and then change it.

## 5.2 Exporting pins table

To export Pins table:

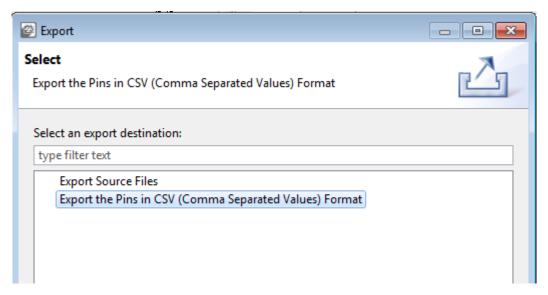

- 1. Select **File > Export** from the main menu.

- 2. In the **Export** dialog box, select the **Export the Pins in CSV** (Comma Separated Values) Format option.

#### **Exporting pins table**

Figure 5-3. Export dialog

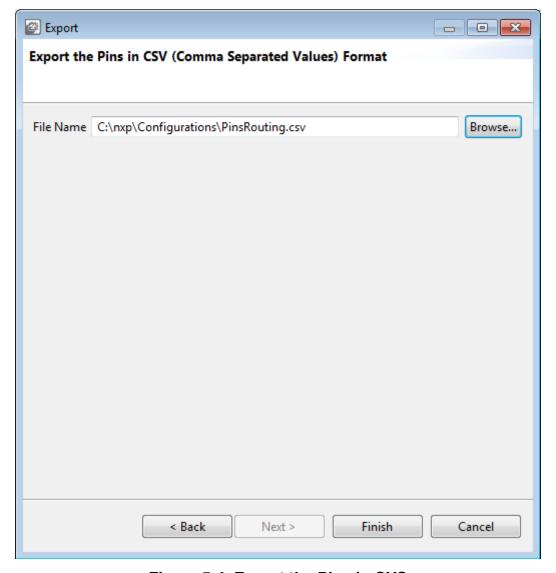

- 3. Click Next.

- 4. Select the folder and specify the file name to which you want to export.

Figure 5-4. Export the Pins in CVS

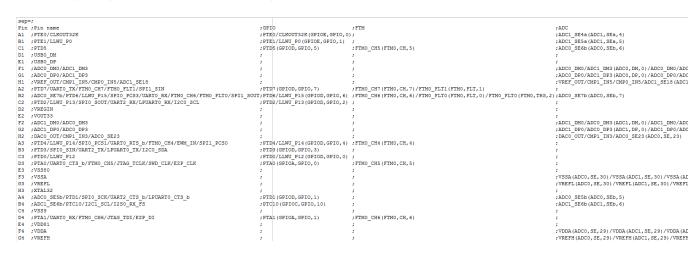

5. The exported file contains content of the current Pins view table, plus list of functions and selected routed pins.

#### Exporting pins table

```

Pin; Pin name; GPIO; FTM; ADC; UART; SPI; I2S; LLWU; I2C; CMP; SUPPLY; LPUART; USB; SIM; JTAG; RTC; EWM; Other; Routing for BOARD InitPins

A1; PTEO/CLKOUT32K; PTEO/CLKOUT32K(GPIOE, GPIO.0); ; ADC1 SE4a(ADC1, Sea, 4); UART1 TX(UART1, TX); SPI1 PCS1(SPI1, PCS1); ; ; I2C1 SDA(I2C1, SDA); ; ; ; PTEO

B1:PTE1/LLWU P0:PTE1/LLWU P0 (GPIOE.GPIO.1)::ADC1 SE5a(ADC1.SEa.5):UART1 RX (UART1 RX):SPI1 SOUT (SPI1.SOUT)/SPI1 SIN(SPI1.SIN)::PTE1/LLWU P0 (

C1; PTD5; PTD5 GPIOD, GPIO, 5); FTM0_CH5 (FTM0, CH, 5); ADC0_SE6b (ADC0, SEb, 6); UART0_CTS_b (UART0, CTS); SPI0_PCS2 (SPI0, PCS2) / SPI1_SCK (SPI1, SCK);;;;;;;

D1;USB0 DM;;;;;;;;;;USB0 DM(USB0,DM);;;;;;

E1;USB0 DP;;;;;;;;;USB0 DP(USB0,DP);;;;;

G1; ADCO DPO/ADC1 DP3;;; ADCO DPO/ADC1 DP3 (ADCO, DP, 0) /ADCO DPO/ADC1 DP3 (ADCO, DP, 0) /ADCO DPO/ADC1 DP3 (ADC1, DP, 3) /ADCO DPO/ADC1 DP3 (ADC1, SE, 3);

H1; VREF OUT/CMP1 IN5/CMP0 IN5/ADC1 SE18;; VREF OUT/CMP1 IN5/CMP0 IN5/ADC1 SE18(ADC1, SE, 18);;;;; VREF OUT/CMP1 IN5/CMP0 IN5/ADC1 SE18(CMP1, I

A2; PTD7/UARTO TX/FTMO CH7/FTMO FLT1/SP11 SIN; PTD7 (GP10D, GP10,7); FTMO CH7 (FTMO,CH,7)/FTMO FLT1(FTMO,FLT,1); ; UARTO TX (UARTO,TX); SP11 SIN(SP11

B2;ADCO SE7b/PTD6/LLWU P15/SPIO PCS3/UARTO RX/FTMO CH6/FTMO FLTO/SPI1 SOUT; PTD6/LLWU P15/GPIOD, GPIO, 6); FTMO CH6(FTMO, CH, 6) / FTMO FLTO (FTMO, F

C2; PTD2/LLWU_P13/SP10_SOUT/UART2_RX/LPUART0_RX/12C0_SCL; PTD2/LLWU_P13 GP10D, GP10, 2);; UART2_RX (UART2, RX); SP10_SOUT (SP10, SOUT);; PTD2/LLWU_P1

D2; VREGIN; ;; ;; ;; ;; ; VREGIN (USBO, VREGIN);;;;;

E2; VOUT33;;;;;;;;;; VOUT33 (USB0, VOUT33);;;;;

G2;ADC1_DP0/ADC0_DP3;;;ADC1_DP0/ADC0_DP3(ADC1,DP0/ADC0_DP3(ADC1,DP0/ADC0_DP3(ADC0,DP3),ADC1_DP0/ADC0_DP3(ADC0,DP3),ADC1_DP0/ADC0_DP3(ADC0,DP3,DP0/ADC0_DP3(ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,DP3,DP0/ADC0,D

A3;PTD4/LLWU_P14/SPIO_PCS1/UARTO_RTS_b/FTMO_CH4/EWM_IN/SPI1_PCS0;PTD4/LLWU_P14(GPIOD,GPIO,4);FTMO_CH4(FTMO,CH,4);;UARTO_RTS_b(UARTO,RTS);SP

B3;PTD3/SPIO_SIN/UART2_TX/LPUART0_TX/I2C0_SDA;PTD3(GPIOD,GPIO,3);;;UART2_TX(UART2,TX);SPI0_SIN(SPIO,SIN);;;12C0_SDA(12C0,SDA);;;LPUART0_TX(

C3;PTDO/LLWU_P12;PTDO/LLWU_P12(GPTOD,GPIO,O);;;UART2_RTS_b(UART2,RTS);SPTO_PCSO(SPIO,PCSO/SS);;PTDO/LLWU_P12(LLWU,WAKEUP,P12);;;;LPUARTO_RT

D3;PTAO/UARTO_CTS_b/FTMO_CH5/JTAG_TCLK/SWD_CLK/EZP_CLK;PTAO(GPIOA,GPIO,0);FTMO_CH5(FTMO,CH,5);;UARTO_CTS_b(UARTO,CTS);;;;;;;;;JTAG_TCLK/JT

```

Figure 5-5. Exported file content

The exported content can be used in other tools for further processing. For example, see it after aligning to blocks in the image below.

Figure 5-6. Aligning to block

# Chapter 6 Support

If you have any questions or need additional help, perform a search on the Kinetis or i.MX community or post a new question. Visit https://community.freescale.com/community/kinetis or https://community.freescale.com/community/imx.

How to Reach Us:

Home Page:

nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals", must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

Freescale, the Freescale logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. All rights reserved.

© 2016 Freescale Semiconductor, Inc.

**Document Number PINSGS**