### COST DRIVERS AND DESIGN GUIDELINES TO IMPROVE PRINTED CIRCUIT BOARD MANUFACTURABILITY

### **BOARD SOLUTIONS GROUP**

ANDRES MARQUEZ DFX ENGINEER FTF-DES-N1992 May 17, 2016

PUBLIC USE

# AGENDA

- Introduction

- Importance of Early Engagement

- Design for Manufacturing (DFM)

- PCB Fabrication Cost Adders

- PCB Assembly Recommendations

- Stay Up to Date

- Q & A

# INTRODUCTION

# Introduction

What this presentation IS about:

- It aims to talk about printed circuit board's design aspects that drive manufacturing and assembly costs

- It shows guidelines and recommendations for PCB fabrication and assembly

What this presentation IS NOT about:

- It does not show a process to set the cost of PCBs

- It is not project specific

### Audience:

- Everyone interested in PCBs

- 3 PUBLIC USE **#NXPFTF**

# IMPORTANCE OF EARLY ENGAGEMENT

## **Importance of Early Engagement**

PCB Design should have early input from:

- a) Manufacturing Guidelines

- b) Parties building the board

5 PUBLIC USE **#NXPFTF**

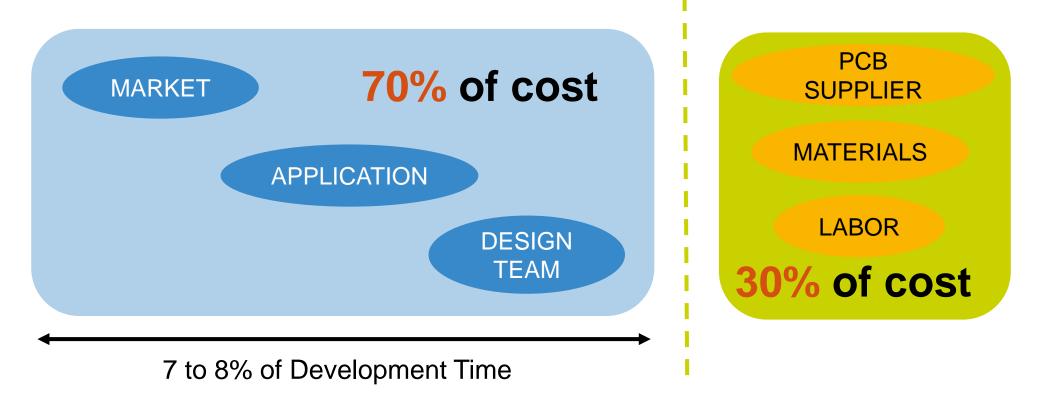

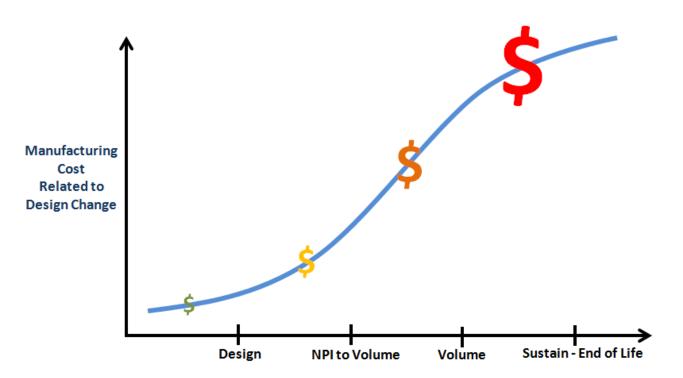

# **Importance of Early Engagement**

Image reference: Lean NPI With Valor. Mentor Graphics

Early involvement in product life cycle to shift money to the left: *"The earlier the changes in the design, the better."*

- Avoid manufacturing cost impact by following manufacturing guidelines

- Early supplier involvement to define manufacturing capabilities and be up to date with new technologies

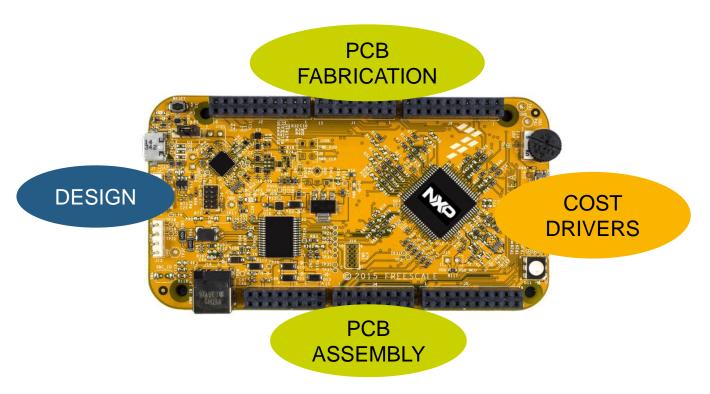

# DESIGN FOR MANUFACTURING (DFM)

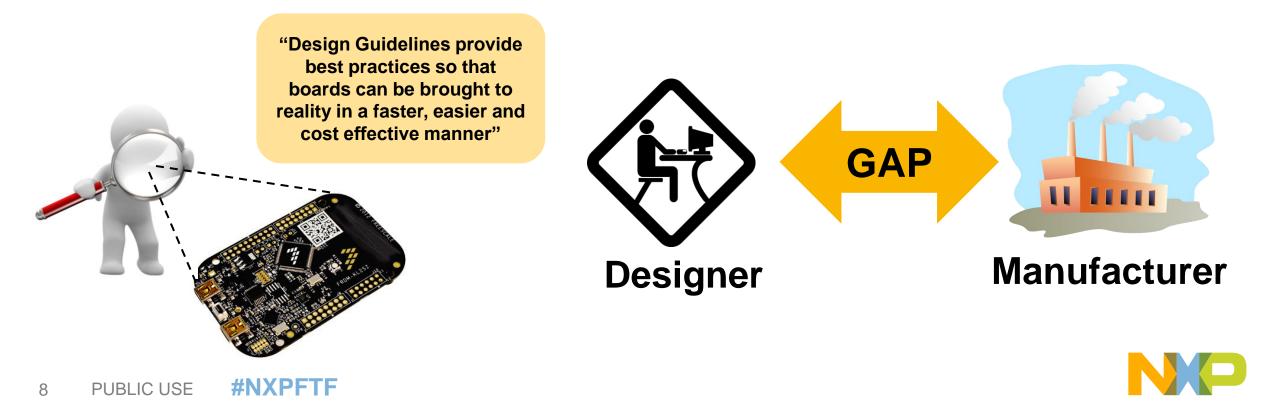

# **Design For Manufacturing (DFM)**

Awareness of how the way we design is going to affect manufacturing

Several Definitions, all convey in **designing a product in the most efficient** manner possible in terms of cost, resources and time.

## **PCB Fabrication and PCB Assembly**

9 PUBLIC USE **#NXPFTF**

# PCB FABRICATION COST ADDERS

# **Printed Circuit Board Fabrication Cost Adders**

- Volume and Lead Time

- PCB Fab Shop's Capabilities

- Panel Utilization

- Stackup Number of Layers

- Stackup Configuration

- Technology Complexity (HDI)

- Copper Weight vs. Minimum Spacing/Width

- Copper Considerations

- Drilling and Aspect Ratio

- Drill to Copper Distance

- Solder Mask Considerations

- PCB Finish

- Fabrication Drawing

# **Volume and Lead Time**

- Prototypes vs. Production

- Many PCB manufacturers have a minimum cost for an order >> MOQ

- Time is Money. A Quick Turn will cause the PCB Fabshop to change priorities and increase the cost.

#### VOLUME AS A COST ADDER

| Quantity | 150    | 500    | 5000   |

|----------|--------|--------|--------|

| Cost     | \$7.36 | \$2.43 | \$0.62 |

#### LEAD TIME AS A COST ADDER - QTY 1000

| Lead Time | 10 Days | 15 Days | 20 Days |

|-----------|---------|---------|---------|

| Cost ea.  | \$3.40  | \$3.00  | \$2.74  |

12 PUBLIC USE **#NXPFTF**

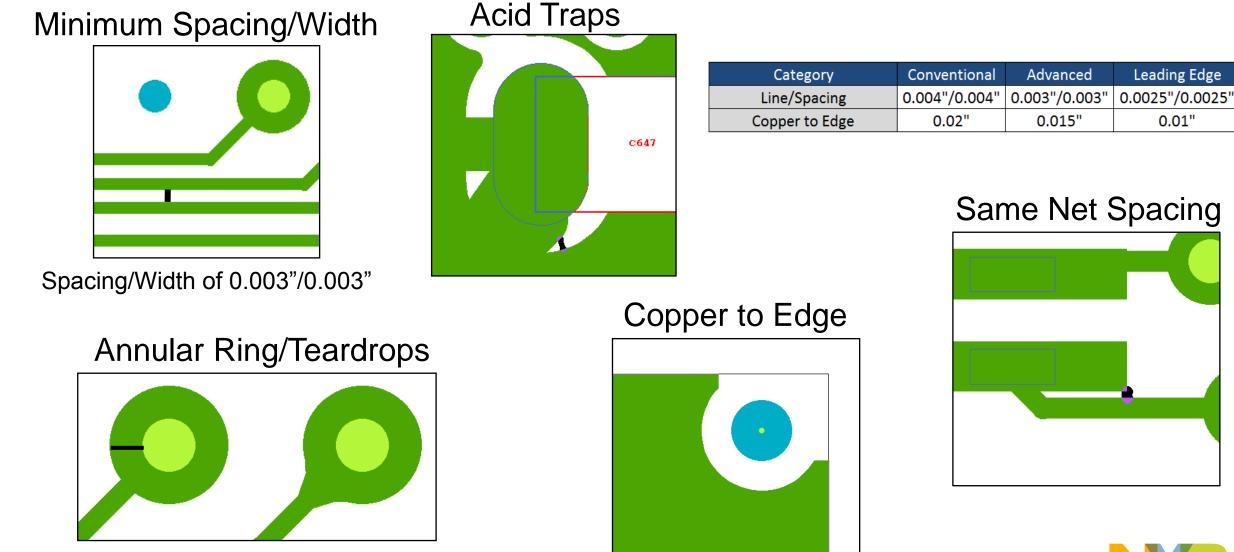

## **PCB Fab Shop's Capabilities**

Understand the PCB Fab Shop's capabilities

CONVENTIONAL

ADVANCED

LEADING EDGE

Advanced categories build up. Each parameter contributes independently for the yield of the PCB.

| Category                 | Conventional  | Advanced      | Leading Edge    |

|--------------------------|---------------|---------------|-----------------|

| Line/Spacing             | 0.004"/0.004" | 0.003"/0.003" | 0.0025"/0.0025" |

| Mechanical Drill         | 0.010"        | 0.008"        | 0.006"          |

| Aspect Ratio             | 8:1 ~ 10:1    | 10:1 ~ 15:1   | 15:1 ~18:1      |

| Solder Mask Registration | 0.003"        | 0.002"        | 0.001"          |

| DHS to Copper            | 0.008"        | 0.007"        | 0.006"          |

| Copper to Edge           | 0.02"         | 0.015"        | 0.01"           |

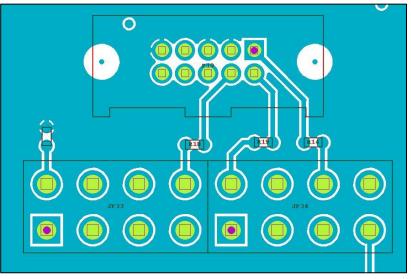

# **Panel Utilization**

- Know the types of panels your Fab shop uses:

- The most common measurements are 18"x24" and 21"x24"

- How many parts will fit? Goal: as much parts as possible in a Panel

- Rectangular boards can usually fit better in a panel than circular boards

- Consider part rotation

- PCB fab shops have to charge for material not used

| 5.25x3.45 | 5.25x3.45 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 |

|-----------|-----------|---------------|---------------|---------------|---------------|

| 5.25x3.45 | 5.25x3.45 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 |

| 5.25x3.45 | 5.25x3.45 |               |               |               |               |

| 5.25x3.45 | 5.25x3.45 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 |

| 5.25x3.45 | 5.25x3.45 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 | 3.45x<br>5.25 |

|           |           |               |               |               |               |

Same panel 18"x24" different arrangement. 41.9% (10 boards) vs. 67.1% (16 boards) utilization

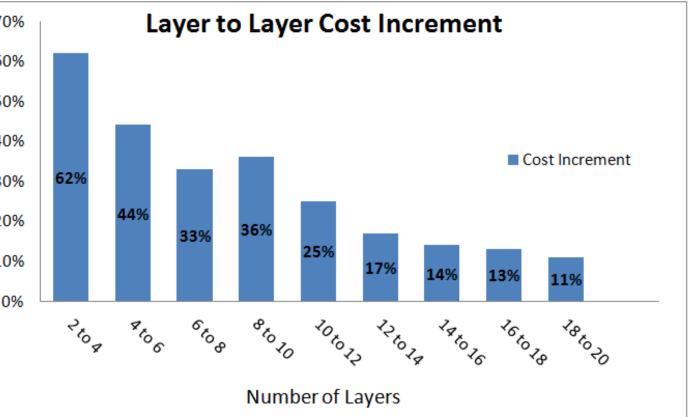

# **Stackup – Number of Layers**

Number of Layers affects cost by increments

| 300000000CL |

|-------------|

| sst         |

| spt         |

| smt         |

| top         |

| bottom      |

| smb         |

| spb         |

| ssb         |

| ADDDDDDDDDL          | 70%  |

|----------------------|------|

| sst                  |      |

| spt                  | 60%  |

| smt                  |      |

| top                  | 50%  |

| 12_gnd_1             |      |

| 13_int_1             | 409  |

| 14_int_2             |      |

| 15_gnd_2             | 309  |

| 16_pwr_1             |      |

| 17_pwr_2             | 209  |

| 18_gnd_3             | 4.00 |

| 19_int_3             | 109  |

| 110_int_4            | 00   |

| 111_gnd_4            | 0%   |

| bottom               |      |

| smb                  |      |

| spb                  |      |

| ssb                  |      |

| 1 <u>000000000</u> 7 |      |

|                      |      |

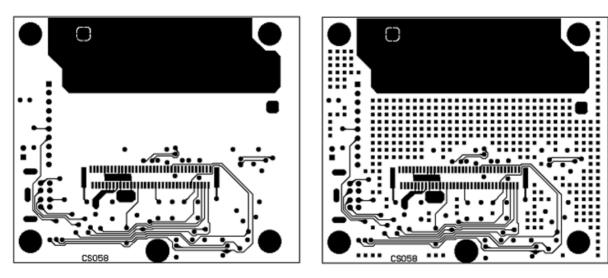

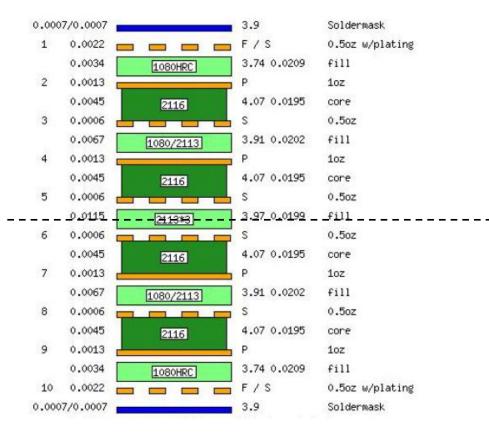

# **Stackup Configuration**

- Material Selection \$\$\$ Application Driven, mostly signal integrity

- Balanced Stackup:

- Symmetrical stack up to avoid warpage

-Thieving pads

**PUBLIC USE**

16

Image by electronics.stackexchange.com

**#NXPFTF**

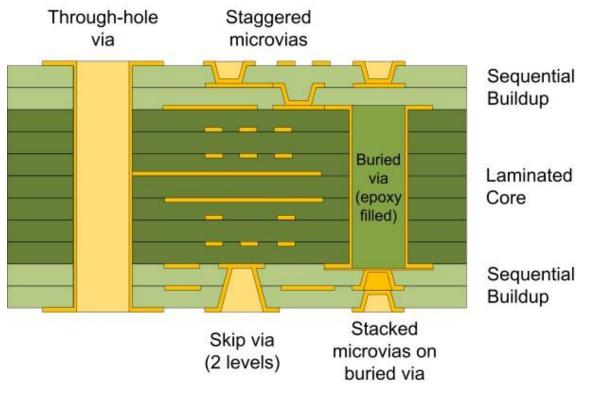

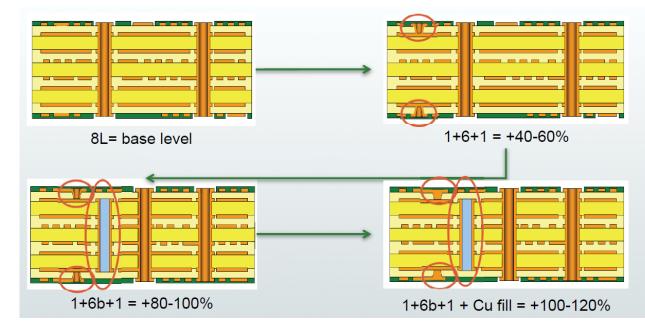

# **Technology Complexity (HDI)**

Microvias usually < 0.006" and laser drilled</li>

### Type III HDI Structure

Cost based on Extra Processes

Image by NCAB – Cost Drivers in PCB Production

Image by www.datarespons.com - High Density Interconnect

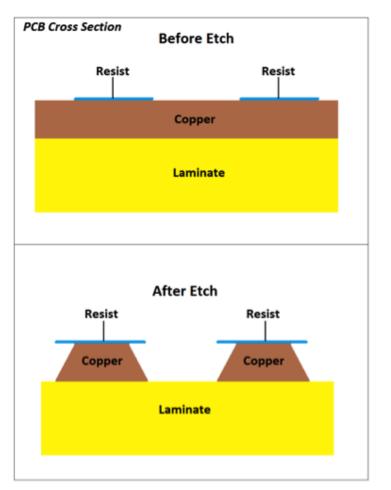

# **Copper Weight vs. Minimum Spacing/Width**

• The thicker the copper the more difficult to etch

Etch compensation defines minimum spacing/width

| Internal Layers                        | Cu Weight        | Conventional            |

|----------------------------------------|------------------|-------------------------|

| Min Line                               | 0.5              | 0.004                   |

| Min Separation                         | 0.5              | 0.004                   |

| Min Line                               | 1                | 0.005                   |

| Min Separation                         | 1                | 0.005                   |

| Min Line                               | 2                | 0.007                   |

| Min Separation                         | 2                | 0.007                   |

|                                        |                  |                         |

| External Layers                        | Cu Weight        | Conventional            |

| External Layers<br>Min Line            | Cu Weight<br>0.5 | Conventional<br>0.004   |

| · · · · · · · · · · · · · · · · · · ·  |                  |                         |

| Min Line                               | 0.5              | 0.004                   |

| Min Line<br>Min Separation             | 0.5<br>0.5       | 0.004<br>0.004          |

| Min Line<br>Min Separation<br>Min Line | 0.5<br>0.5<br>1  | 0.004<br>0.004<br>0.004 |

Image by www.pcbuniverse.com

# **Copper Considerations**

**#NXPFTF**

**PUBLIC USE**

19

0.01"

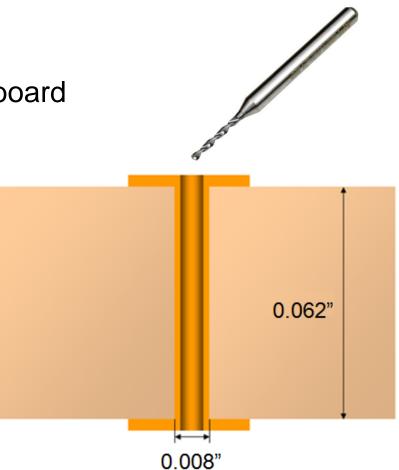

# **Drilling and Aspect Ratio**

- Affected by quantity, minimum drill and thickness of the board

- Drilling small holes has an impact in cost: < 0.008"

- The Aspect Ratio is defined as the board thickness divided by the drill size

- Higher aspect ratios are more difficult to produce

$Maximum Aspect Ratio = \frac{Board Thickness}{Smallest Drilled Hole}$

*Maximum Aspect Ratio* =

$$\frac{0.062''}{0.008''}$$

= 7.75:1

| Category         | Conventional | Advanced    | Leading Edge |

|------------------|--------------|-------------|--------------|

| Aspect Ratio     | 8:1 ~ 10:1   | 10:1 ~ 15:1 | 15:1 ~18:1   |

| Mechanical Drill | 0.010"       | 0.008"      | 0.006"       |

**For fabrication flexibility** Via Size (+0.000"/-Via Size)

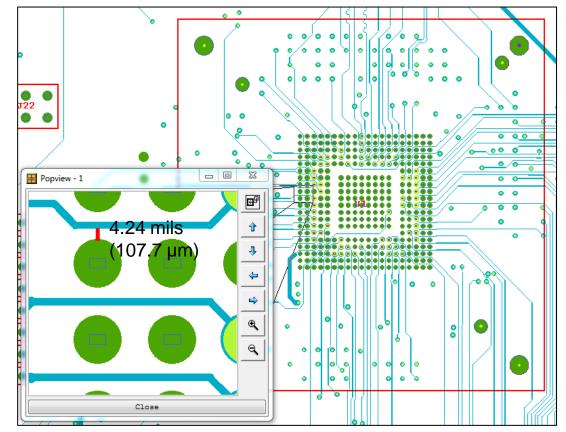

# **Drill to Copper Distance**

- Often overlooked issue

- Imaging tolerance, layer to layer registration and Drill tolerance come into play

- Center FHS in its tolerances + 4 mils (100 µm) plating to obtain approximate Drilled Hole Size

$$DHS = FHS + \frac{ABS(POS TOLERANCE + NEG TOLERANCE)}{2} + 4$$

• POS and NEG Tolerances with signs included. Tolerances specified in fabrication drawing.

$$DHS = 14 + \frac{ABS(4+0)}{2} + 4 = 20$$

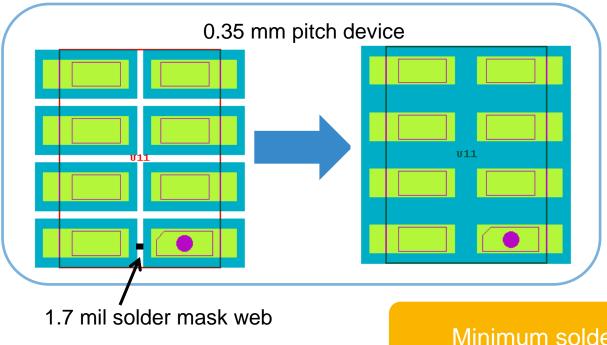

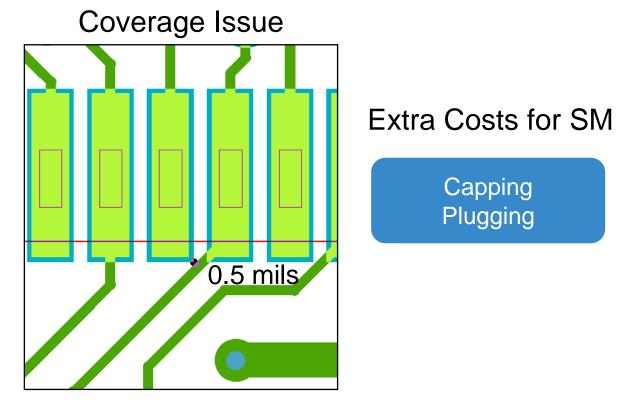

# **Solder Mask Considerations**

- Color may affect the process

- Types of solder mask LDI vs. LPI

- When pitch is small remove solder mask between pads

| Category                 | Conventional | Advanced | Leading Edge |

|--------------------------|--------------|----------|--------------|

| Solder Mask Registration | 0.003"       | 0.002"   | 0.001"       |

Minimum solder mask webs are usually 3 mils.

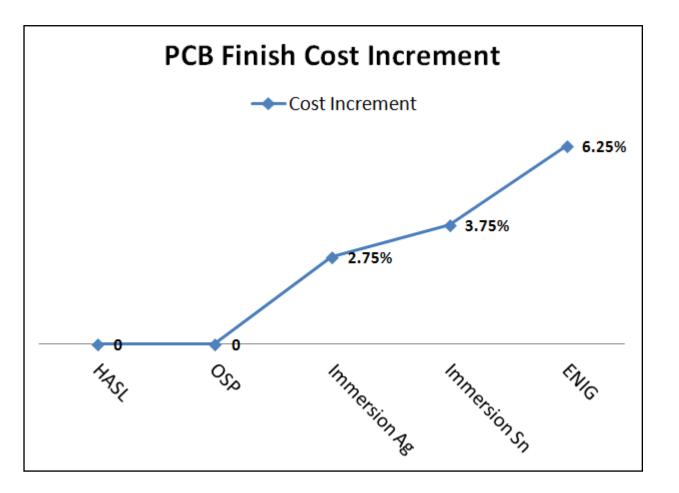

# **PCB** Finish

- Hot Air Solder Leveling (SnPb HASL)

- Organic Solderability Preservative (OSP)

- Immersion Silver (Imm Ag)

- Immersion Tin (Imm Sn)

- Lead Free HASL (LF HASL)

- ENIG Electroless Nickel Immersion Gold

- Electrolytic Hard Gold

- Electroless Nickel Electroless

- Palladium Immersion Gold (ENEPIG)

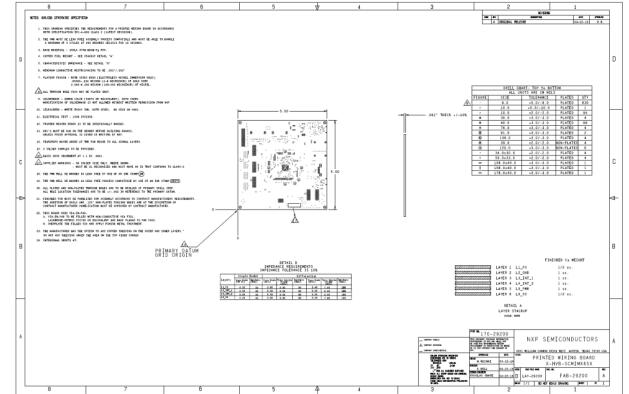

# **Fabrication Drawing**

# Should contain necessary information to avoid delays or confusion

- · Some important information to be specified:

- Dimensions of the outline of the board with cutouts or notches

- Thickness of the board along with stackup

- Base material

- IPC class type

- Copper thickness

- Drill map with quantity, tolerances and their respective symbols

- Surface finish

- Solder mask color

- Whether it is allowed for fab shop to add thieving pads for copper balancing, NFP removal and Tear drops for ease of manufacturing

- List of intentional shorts to avoid confusion

- Impedance chart

- Revision and company information

- 24 PUBLIC USE **#NXPFTF**

Avoid discrepancies between fabrication drawing and CAD data

# PCB ASSEMBLY RECOMMENDATIONS

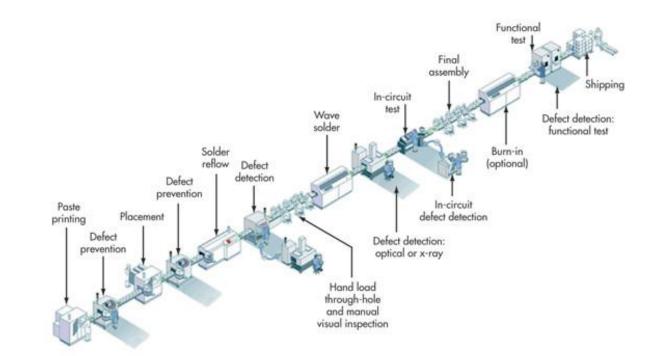

# **Printed Circuit Board Assembly Recommendations**

- Assembly Cost

- Product Technology Definition

- Package Sizes

- Component Spacing & Footprints

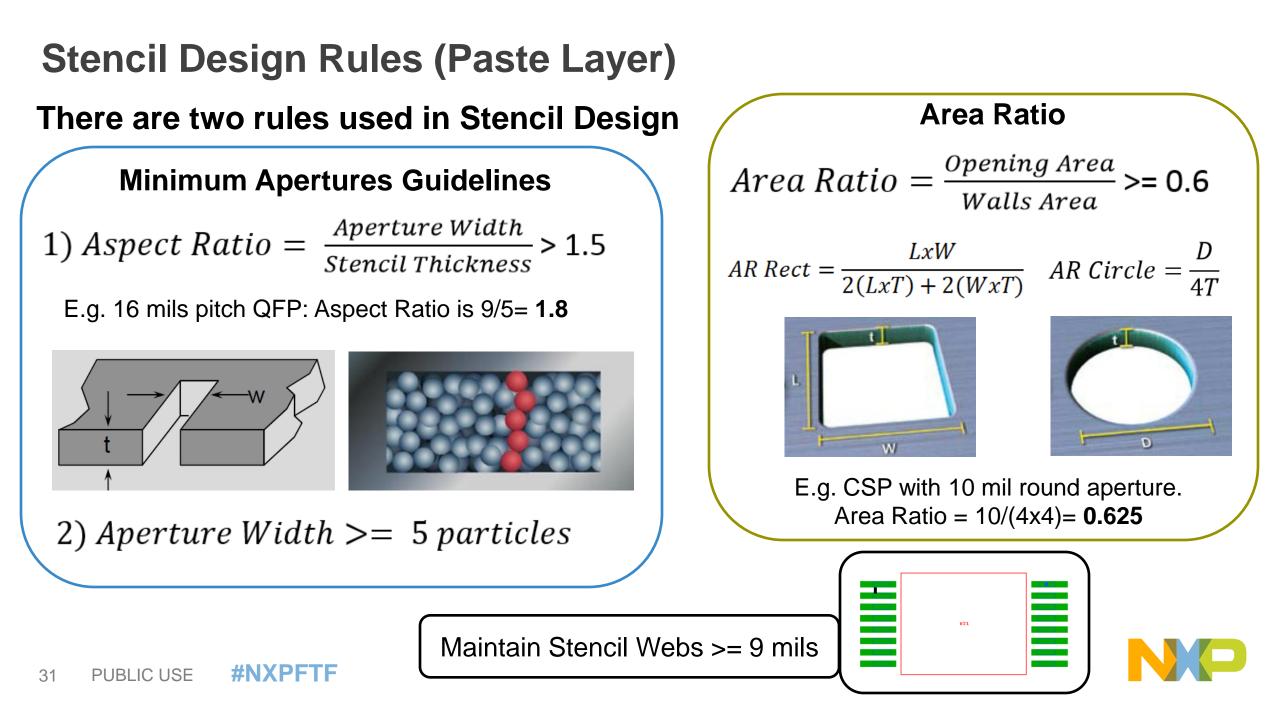

- Stencil Design Rules

- Wave Soldering

- General Recommendations For Assembly

# **Assembly Cost**

The assembly cost from the process point of view will depend upon:

- Number of processes

- SMT Top and Bottom

- PTH Top and Bottom

- Press fit

- TEST

### Process time

- SMT placement time (number of different components, rotation, etc.)

- Board size (nozzle travel)

- Hand placed components, manual soldering, etc.

# **Product Technology Definition**

- Intention of the board

- Application

- Volume

- Prototype vs. Production

## **Package Sizes**

- Component manufactures have new packages with the same features

- Keep your BOMs up to date, use new parts

- Smaller is not better in all cases, define and standardize the technology you will use. Package drives PCB technology.

# **Component Spacing and Footprints**

Why is it important to maintain an adequate component to component distance?

- For better machine programming (Placement tolerance)

- To compensate for component and PCB dimensional tolerances

- To facilitate component verification (Visual inspection)

- To facilitate rework process

- To facilitate cleaning process

Footprint design to achieve reliable solder joints

Follow IPC7351 as a reference

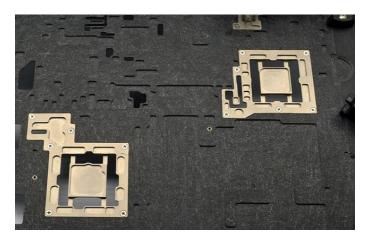

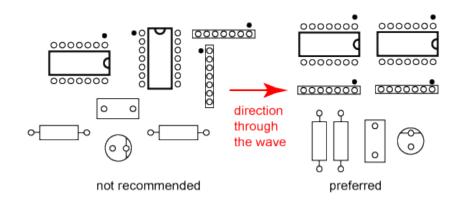

# **Wave Soldering**

- Keep enough distance from SMT to PTH components' pins on the other side in order to avoid high cost wave solder pallets.

- Consider alternate ways: paste in hole, selective wave solders.

- Take care of component orientation to avoid shorts and retouch!

Wave Solder Pallet with Titanium Inserts

Component's Alignment for Wave Solder

**Selective Soldering Process**

# **General Recommendations for Assembly**

- Define Type of IPC Class so that CM knows what to accept or not

- Use at least 3 fiducials, spaced by 8 inches

- If having a few SMT comps on bottom move all to top to avoid having duplicated stencil NREs if board is big

- Avoid having lots of PTH comps on both sides so that all of them are processed at the same process on top, otherwise they will have to be hand soldered

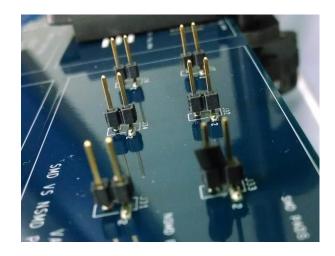

- Avoid using two pin SMT headers as they tend to detach along with pads. Recommend to increase the size of pad encroached in case they are used.

# **STAY UP TO DATE**

# Stay Up To Date...

- App Notes from NXP: <u>www.nxp.com</u>

- Websites from Fab Shops

- PCB Design Magazine: <a href="http://www.iconnect007.com/magazines/pcb-design-magazine/">http://www.iconnect007.com/magazines/pcb-design-magazine/</a>

SMTA Subscription

- Everything PCB: <a href="http://www.everythingpcb.com/">http://www.everythingpcb.com/</a>

EverythingPCB

- Follow up on Conferences: such as PCB West, Apex, SMTA...

- Forums such as Sparkfun Electronics

35 PUBLIC USE **#NXPFTF**

Contact: Andres.Marquez@nxp.com

# SECURE CONNECTIONS FOR A SMARTER WORLD

### ATTRIBUTION STATEMENT

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, CoolFlux, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE, MIFARE Classic, MIFARE DESFire, MIFARE Plus, MIFARE FleX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TrenchMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2015–2016 NXP B.V.