# MBD Approach with MATLAB & SIMULINK in Powertrain Application Development Using NXP Microprocessor S32Kxx

Daniel Popa, Razvan Ionescu

NXP Automotive Microcontroller & Processors Tools

October 2019 | Session #AMF-AUT-T3836

SECURE CONNECTIONS FOR A SMARTER WORLD

## Agenda

- MBD Development Process with MATLAB Ecosystem – Value Proposition

- NXP MBD Toolbox SW Development Flow

- NXP MBD Toolbox for S32K Features

- S32K Core & Systems Support

- S32K Motor Control Support

- S32K Communication Support

- Various S32K MCU Configuration Modes

- Code Generation and Cross-compiler Support

- Simulation Mode Support (Normal, SIL, PIL)

- MBDT S32K Utilities: AMMCLIB, FreeMASTER, BootLoader, Profiler, Registers

## Model-Based Design Development Process with MATLAB Ecosystem

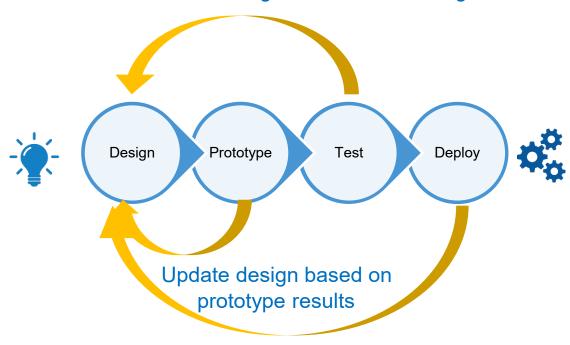

Simulate, Test, Build and Deploy

## Model-Based Design (MBD) Introduction

- MBD is becoming more common during the normal course of software development to explain and implement the desired behavior of a system. The challenge is to take advantage of this approach and get an executable that can be simulated and implemented directly from the model to help you get the product to market in less time and with higher quality. This is especially true for electric motor controls development in this age of hybrid/electric vehicles and the industrial motor control application space.

- Many companies model their controller algorithm and the target motor or plant so they can use a simulation environment to accelerate their algorithm development.

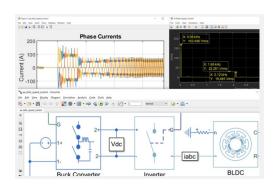

- The final stage of this type of development is the integration of the control algorithm software with target MCU hardware. This is often done using hand code or a mix of hand code and model-generated code. NXP's Model Based Design Toolbox allows this stage of the development to generate 100% of the code from the model.

## Traditional vs. Model-Based Design Dev. Process

#### Redefine the design based on test insights

Integrate tested existing code to new design

## Reduce TTM With Model-Based Design (V-Model SW Dev)

Use MBD and start testing at very earliest stage.

System Requirements

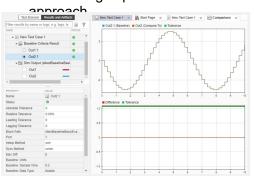

Convert model to SIL and now can test ANSIgenerated software. Can also use MDB library with SIL testing.

Modeling/ Simulation

Use AMMCLIB library and MBD Toolbox to test the Model using target MCU and compiler through PIL testing.

With MBD Toolbox, auto-generate code for direct interface of peripherals for target hardware without any manual hand code.

Functional Testing

Fewer defects found in this phase of testing, where finding defects is expensive.

**HIL Testing**

Now that more testing on target has occurred earlier in the process, HIL testing time is reduced.

Target MCU Implementation

Rapid

Prototype

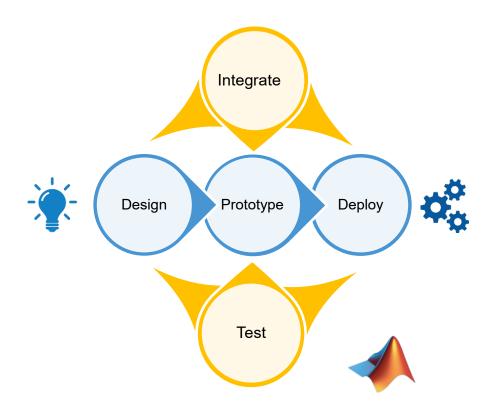

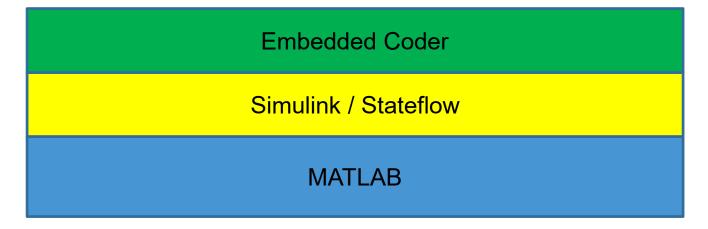

## MATHWORKS Model-Based Design Environment

Embedded Coder is production code generation environment from MATLAB/Simulink models that generates ANSI C source code.

Simulink is graphical environment for building controls algorithms as well as simulation of these algorithms. Stateflow is a special case of Simulink blocks for state based design and flow chart controls of execution.

Simulink allows for a basic solver to execute either in discrete time or continuous time modes.

MATLAB is the base tool environment, very powerful and scriptable and allows access to complex functionalities

## NXP Model-Based Design Toolbox Environment

MCU embedded target and bootloader support

NXP Simulink Blocks for algorithm components, place holders

for peripheral drivers, and other functional utility block interfaces.

NXP Embedded Target, basic main functions + MCU specific infrastructure code

and make file generation to build .elf/s-record/mot files on back end of code

generation process.

Standard MathWorks Tools for Model-Based Design

NXP MBD Toolbox – MCU Runtime Environment (Combination of Target + Bootloader)

NXP MBD Toolbox – Simulink Blocks

NXP MBD Toolbox – Embedded Target MCU Specific Interface

MATLAB / Simulink / Embedded Coder

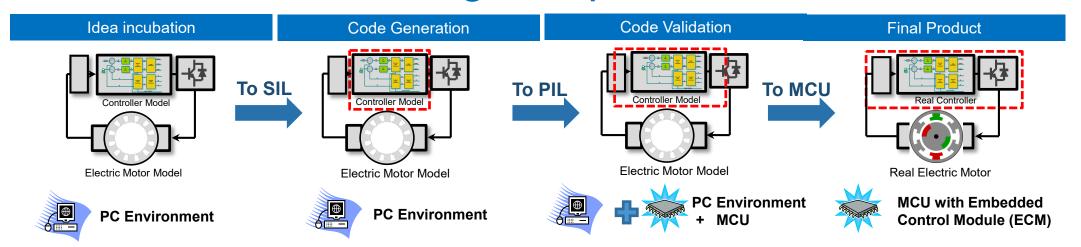

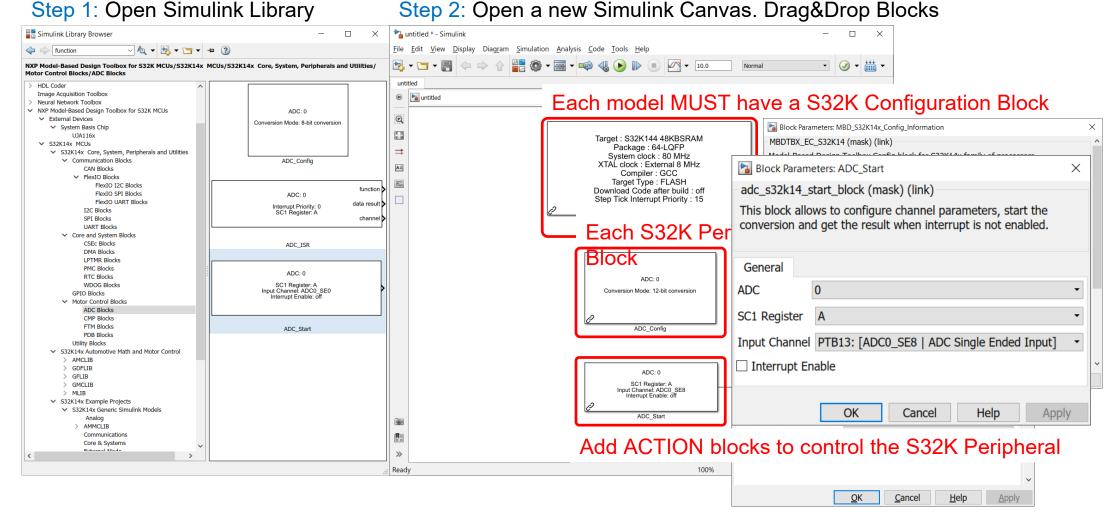

## NXP Model-Based Design Steps

#### <u>Step 1 – System Requirements:</u>

#### Model-in-the-Loop

- Software requirements

- Control system requirements

- Overall application control strategy

#### Step 2 – Modeling/Simulation:

#### Software-in-the-Loop

- · Control algorithm design

- Code generation preparation

- Control system design

- Start testing implementation

#### <u>Step 3 – Rapid Prototype:</u>

#### **Processor-in-the-Loop**

- Controller code generation

- Determine execution time on MCU

- Verify algorithm on MCU

- See memory/stack usage on MCU

#### <u>Step 4 – Target MCU Implementation</u>

#### **MCU Final Application**

- · Validation/verification phase

- Controller code generation

- Test system in target environment using tools for data logging and parameter tuning

## MathWorks Ecosystem

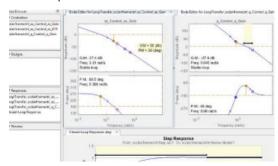

## Control & Design

## **Event Based Modeling**

## **Code Generation**

## Certification & Validation

#### Control Design

Tuning & Auto tuning, Frequency Response

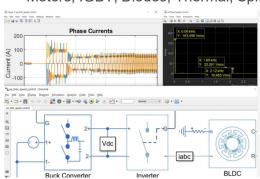

Simscape

Motors, IGBT, Diodes, Thermal, Spice

#### Stateflow

Logic design, Scheduling

#### Simulink Coder

Code generation, legacy code integration, XCP, HIL, PIL, External mode

#### IEC Certification Kit

IEC 61508, ISO26262, EN50128, IEC62304

#### IEC Certification Kit

- ISO 26262, IEC 61508, EN 50128, IEC 615:

- ▶ Embedded Coder

- Polyspace Bug Finder

- Polyspace Code Prover

- Simulink Design Verifier

- Simulink Verification and Validation

- Simulink PLC Coder

- Supporting Artifacts

#### Simulink Requirements

Requirements, Trace PRD, Track Status

## **Embedded Coder Introduction**

- A set of optimization and code configuration options that extend MATLAB Coder and Simulink Coder to generate code for a specific MCU.

- Storage class, type, and alias definition using <u>Simulink®</u> data dictionary capabilities.

- MCU specific code optimizations

- Code verification, including SIL and PIL testing, custom comments, and code reports with tracing of models to and from code and requirements

- Standards support, including ISO 26262, and MISRA-C

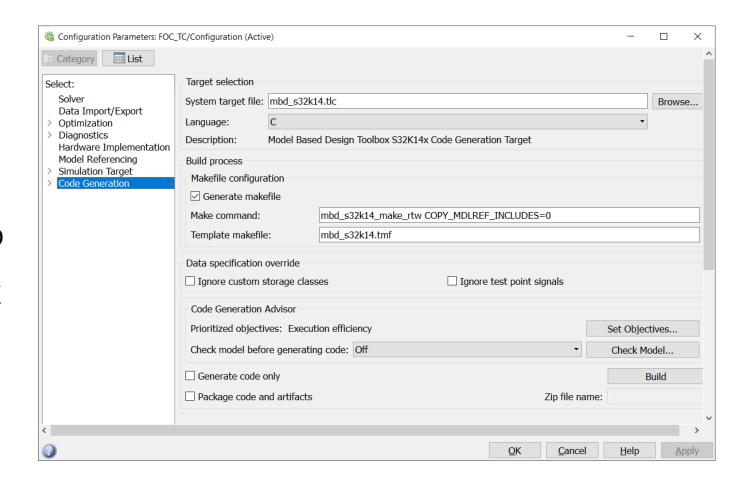

## Embedded Target Code Generation Requirements

- Simulink Model must use a discrete time solver

- Must NOT contain any continuous/special blocks

- Code Generation Add-on: To build MCU target executable must have embedded target selected (NXP MBD Toolbox provides all Embedded Coder configuration files for the S32K MCUs).

- May generate code only or generate code and compile for a target environment .exe, .dll, .s19, .elf...).

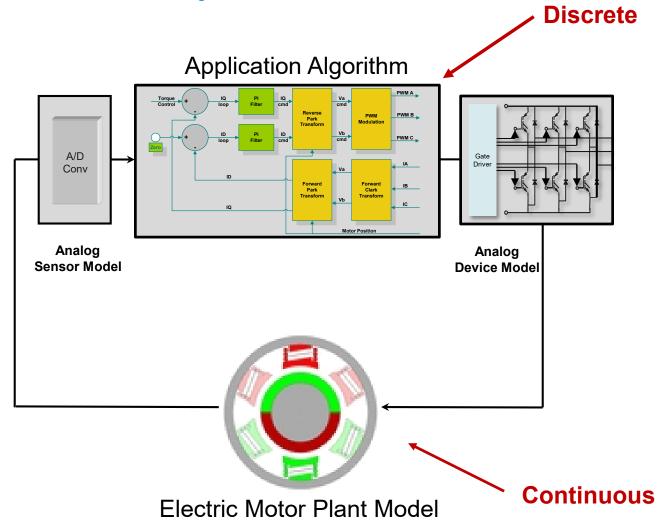

## **Control System Anatomy**

## Embedded Target Requirements for Application Algorithm

- Start from Idealized model (double precision unconstrained mathematics).

- Need to move to target constrained model (integer code, fixed point mathematics, or single precision mathematics).

- Tradeoffs are made in this process depending on how the user chooses to implement the controller on the target MCU.

- The simulation environment supports simulation in any of the target data types also code generation is supported when targeting the MCU.

- What is executed in simulation should be exactly the same as on the embedded target.

## **Embedded Target Code Generation Considerations**

- Must have modeling style guidelines that takes into account code generation and target software architecture

- Plan code generation to meet target software architecture

- Use of an interface Data Dictionary to minimize software integration issues is industry best practice

- Design/Refine models for code generation to target MCU

- Learn and understand code generator optimizations (Know the Tools)

- Optimize model for code generation with target MCU in mind

- Data Types

- Optimize Function/File Partitions

- Utilize target optimized functions for key bottlenecks (custom)

- Utilize target optimized block sets whenever possible

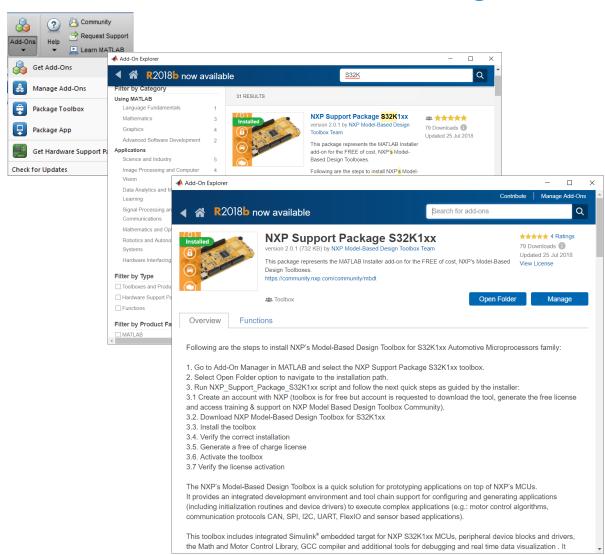

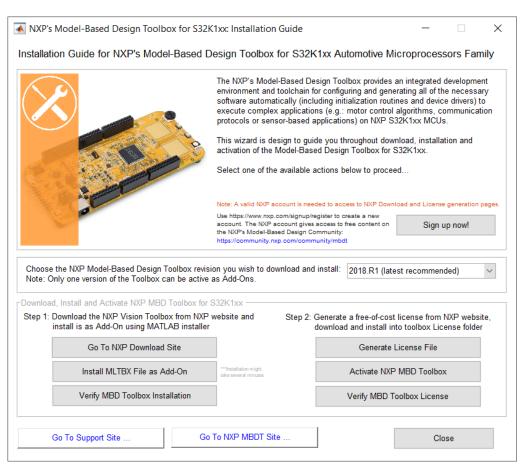

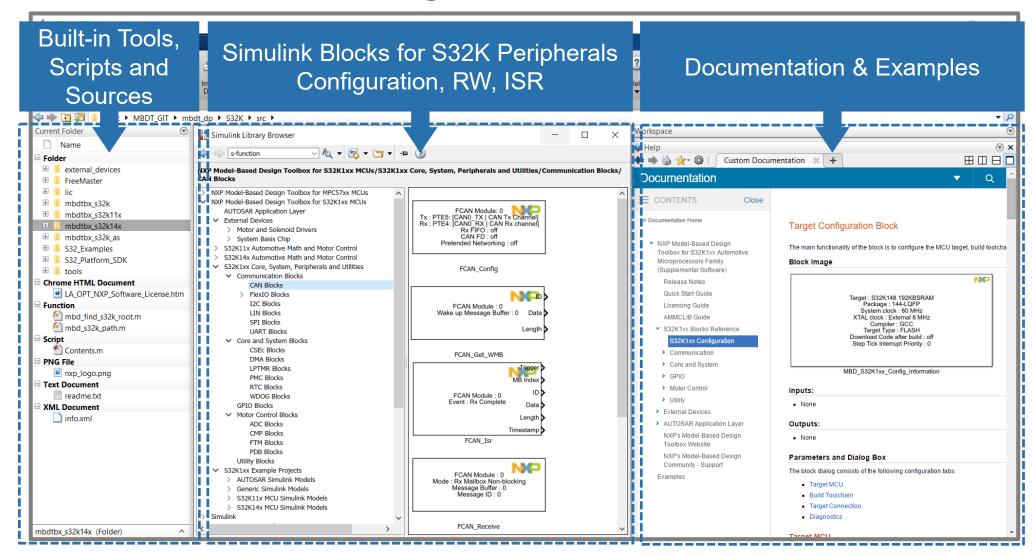

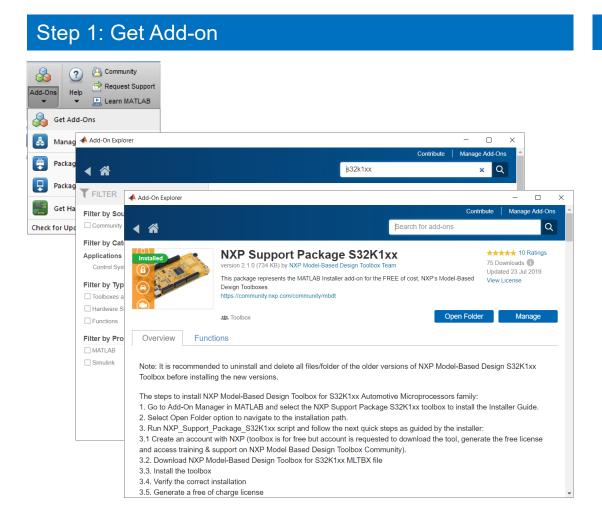

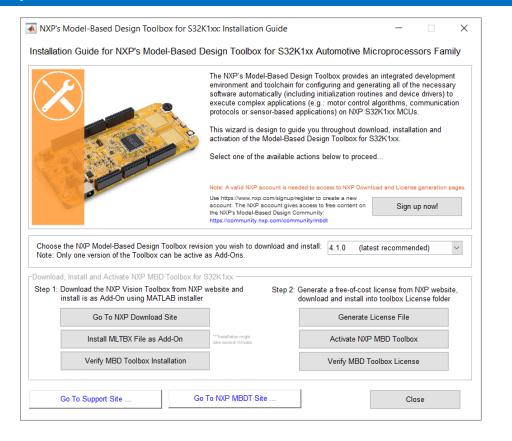

## NXP Model-Based Design Toolbox – Installation

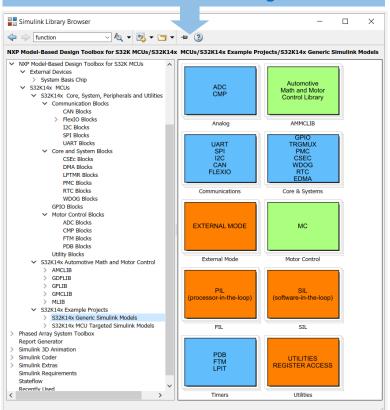

## NXP Model-Based Design Toolbox – Preview

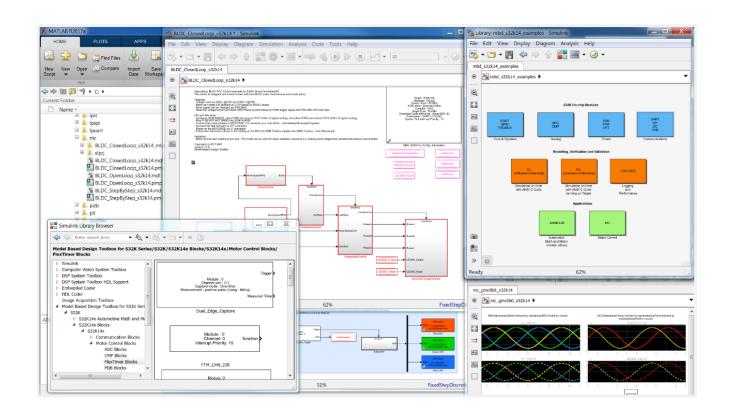

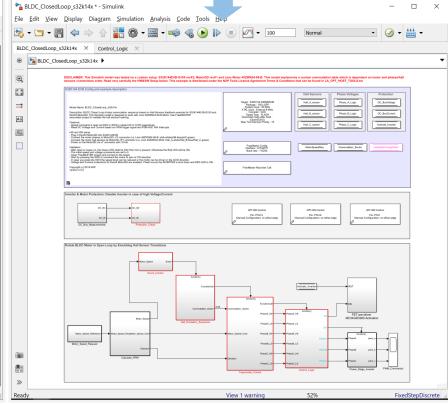

## S32K MBDT – SW Development Flow

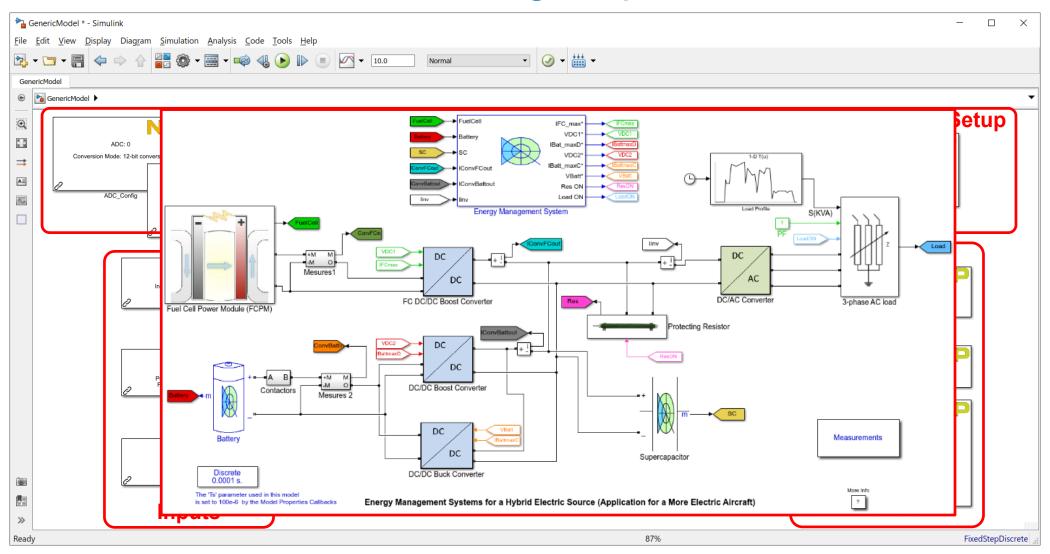

## S32K MBDT – Limitless Design Options

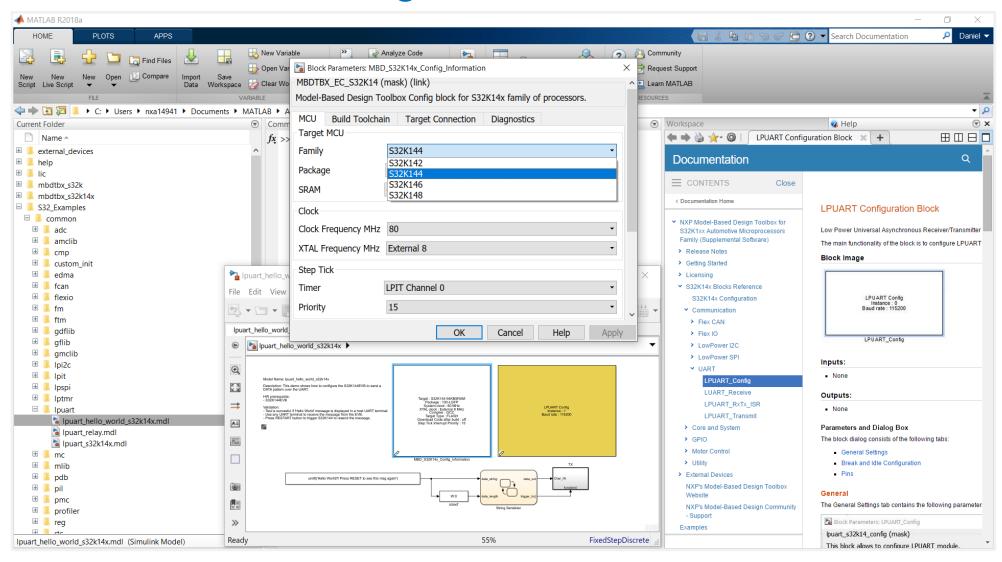

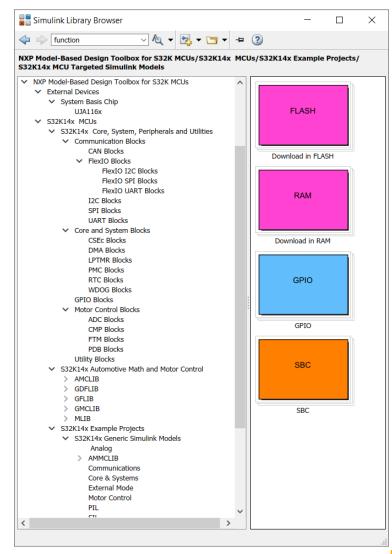

## NXP MBD Toolbox for S32K Features

One common frameworks for simulation, testing and deploying embedded applications for S32K processors without any hand-written code

## NXP Model-Based Design Toolbox – Overview

- Collection of Tools & Libraries designed to **Assist** customers with prototyping and accelerate algorithm development on NXP MCUs

- MCU Peripherals Initialization & Configuration through GUI from a Model-Based Design environment like Simulink®

- Supported Platforms for automatic Code Generation: MagniV S12ZVMx/S12ZVC, MPC56xx, MPC57xx, Arm®-based S32K, DSC and Kinetis families

- Customer Support and Training: <a href="https://community.nxp.com/community/">https://community.nxp.com/community/</a> <a href="mailto:mbdt">mbdt</a>

## NXP Model-Based Design Toolbox – Preview

## NXP Model-Based Design Toolbox – Installation

#### Step 2: Install & Validate

## NXP Model-Based Design Toolbox – Approach

**Basic/Advanced Building Blocks** Ideas & Designs

## NXP Model-Based Design Toolbox – S32K Features

### Peripherals

#### Generic

- Digital & Analogue I/Os

- HW Timers (normal/low power)

- Various ISR sources

#### Communication

- CAN and CAN-FD

- SPI, I2C, UART, FlexIO, LIN

#### Motor Control

- PWM (edge/center/combined, **SW**)

- ADC & CMP

- FTM (Flex Timer Module)

- PDB (Programmable Delay Block)

#### · Core & Subsystems

- CSEC

- DMA

- PMC (Power Management)

- RTC

- WDOG

## Configuration/Modes

#### MCU Options

- Multiple packages (LQFP and BGA)

- Multiple crystal frequencies

#### Compilers

- GCC 6.3

- Green Hills MULTI

- IAR

- RAM/FLASH support

- Custom Memory Map

#### Simulation Modes

- Model in the Loop (MIL)

- Software in the Loop (SIL)

- Processor in the Loop (PIL)

- External Mode

- AUTOSAR (SIL/PIL/Profiling)

#### **Utilities**

#### AMMCLIB Library 1.1.7

- MLIB

- GFLIB/GDFLIB

- GMCLIB/AMCLIB

#### S32 FreeMASTER

- Data acquisition / Calibration

- Customized GUI

#### S32 Bootloader

Program application into MCU Flash/RAM

#### Profiler Function

- Exec. time measurement

- Available in PIL

- Available in standalone

#### Read and Write Blocks

- Memory

- Registers

## MCUs Supported

- S32K142

- S32K144

- S32K146

- S32K148

- S32K116

- S32K118

#### **External Devices**

- SBC UJA 113x

- SBC UJA 116x

- MC33GD3000

- MC34GD3000

- MC33937

- MC34937

## NXP MBDT 2018.R1 release – S32K Peripheral Mapping

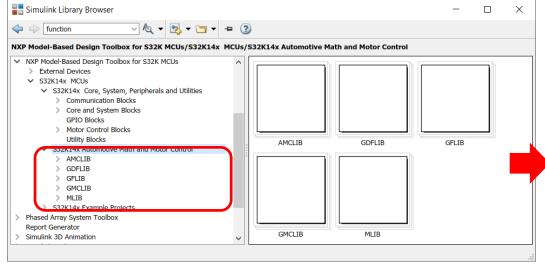

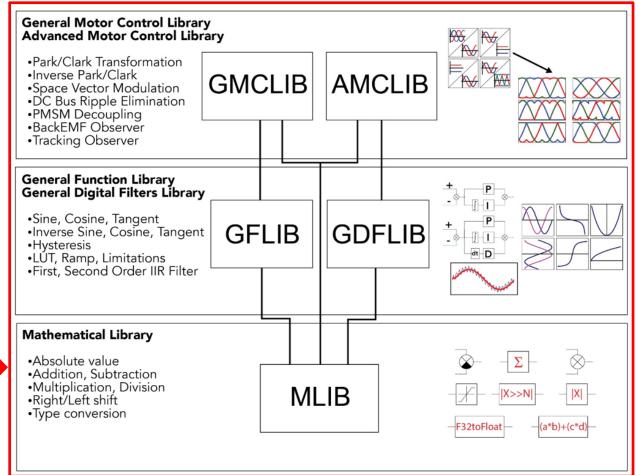

## Automotive & Math and Motor Control Library

- Precompiled software library containing building blocks for a wide range of motor control applications

- Easy migration between platforms with minimized effort

- Production ready SW (SPICE Level 3, CMMI and ISO9001/TS16949)

- Control loop modeling with MATLAB/Simulink® models and examples

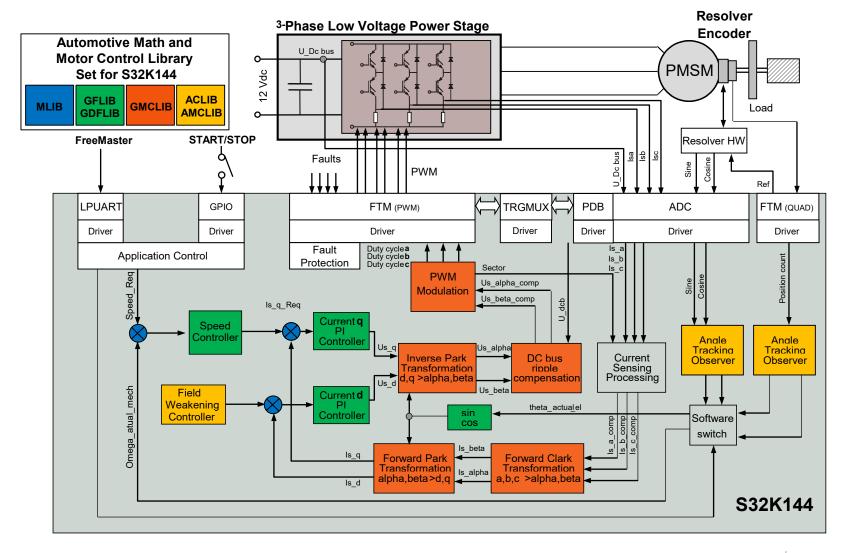

## Application Example for PMSM/FOC with AMMCLIB

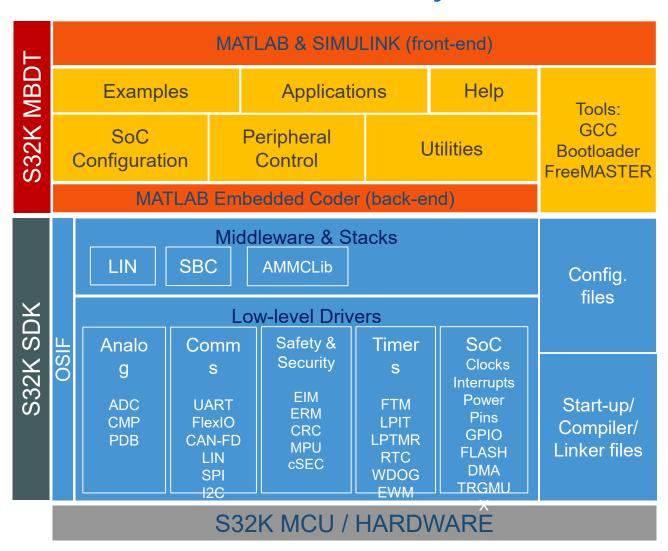

## NXP S32K MBDT – "Ultimate" Abstraction Layer

#### S32K Model-Based Design Layer

- MATLAB/Simulink oriented

- Drag-drop programming

- Automatic C-code generation

- Easy to port

- Peripherals and Applications Examples

- Dedicated online Community

### S32K SDK Enablement Layer

- Layered Software Architecture

- Documented Source Code and Examples

- Integrated with S32 DS and other IDEs

- Featuring various Middleware

- FreeRTOS integration

- Multiple toolchains supported

- Several examples and demos

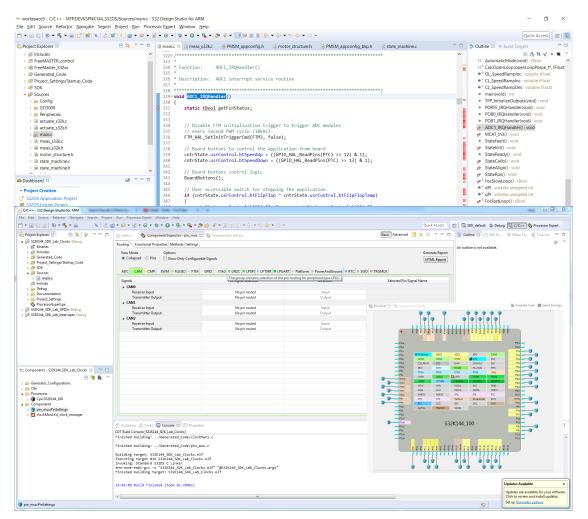

## NXP S32 Design Studio – IDE

- Free of charge

- Unlimited code size

- GNU compiler & debugger integrated

- S32 SDK integrated (graphical configuration)

- Processor Expert integrated (automatic code generator)

- Not intended to compete with premium 3<sup>rd</sup> party IDEs

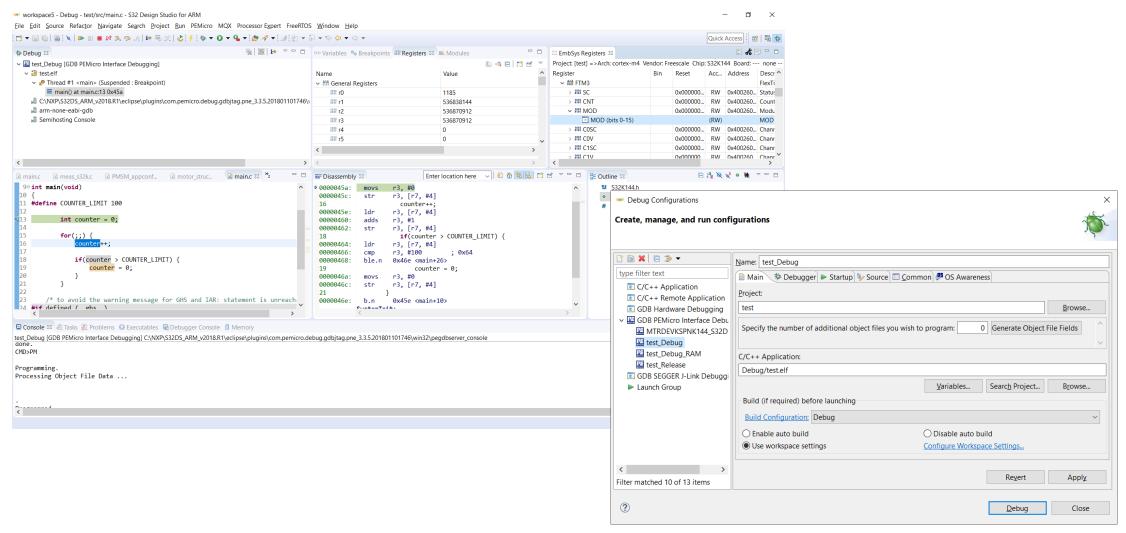

## S32 Design Studio – Application Debugging

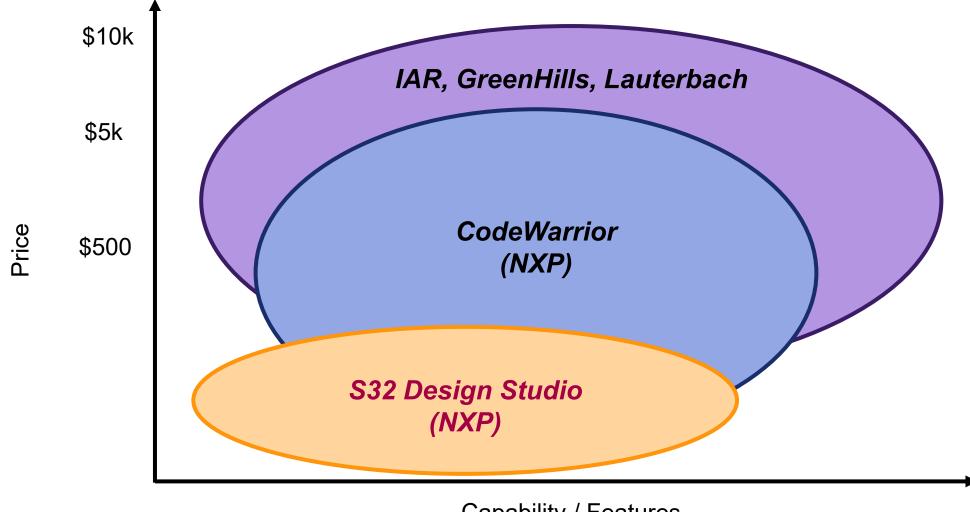

## NXP & 3<sup>rd</sup> Party IDEs – Performance/Price Map

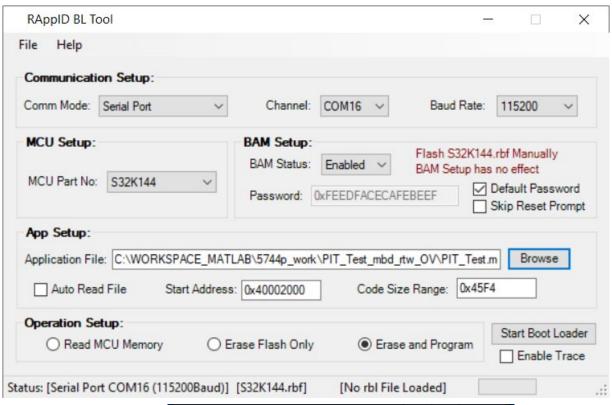

## RAppID Bootloader Utility

Provides a streamlined method for programming code into FLASH or RAM on either target EVBs or custom boards. Once programming is complete, the application code automatically starts.

## Modes of Operation

- Use as a stand-alone PC desktop GUI utility

- Integration with different user required tools chains through a command line interface (i.e. Eclipse Plug-in, MATLAB/Simulink, ...)

## MCUs Supported

- MPC55xx

- MPC56xx

- MPC57xx

- S12ZVM

- S32Kxxx,

- KVxx

- 56F82xx/56F84xx.

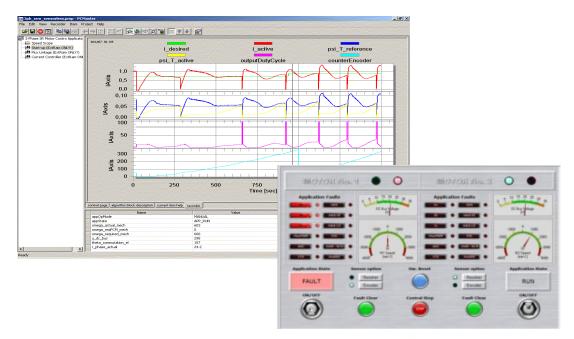

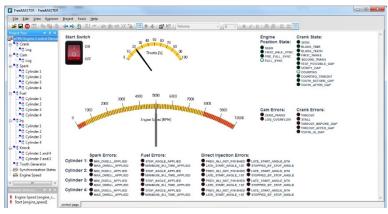

## FreeMASTER — Run Time Debugging Tool

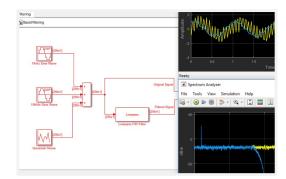

- User-friendly tool for real-time debug monitor and data visualization

- Non-intrusive monitoring of variables on a running system

- Display multiple variables changing over time on an oscilloscope-like display, or view the data in text form

- Communicates with an on-target driver via USB, CAN, UART

- Establish a Data Trace on Target

- Set up buffer (up to 64 KB), sampling rate and trigger

- Near 10-µs resolution

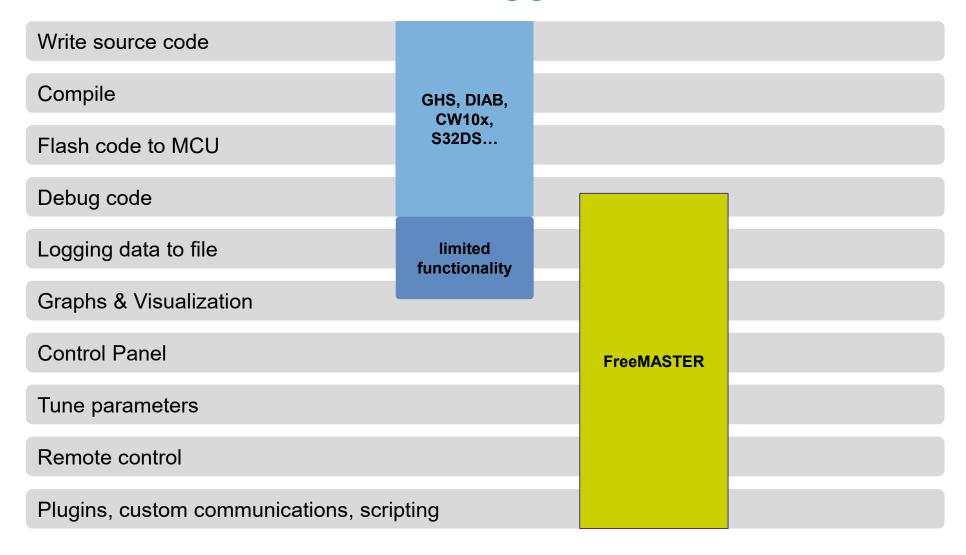

### FreeMASTER vs. IDE & Debugger

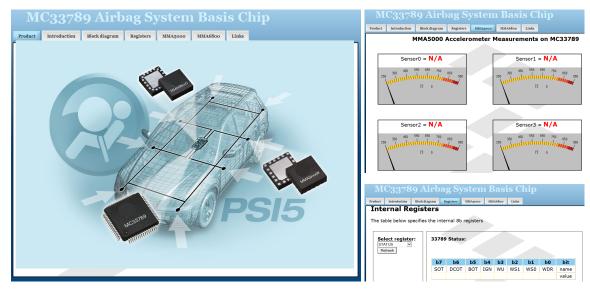

# FreeMASTER – Reference Designs and Demos

**Rapid Sensors Evaluation Tool**

**Airbag Reference Design**

**eTPU Engine Control**

# Agenda

- S32K Solutions

- S32K Motor Control Specific Modules

- Clock

- FTM/PWM

- -PDB

- -ADC

- FTM-PDB-ADC Synchronization

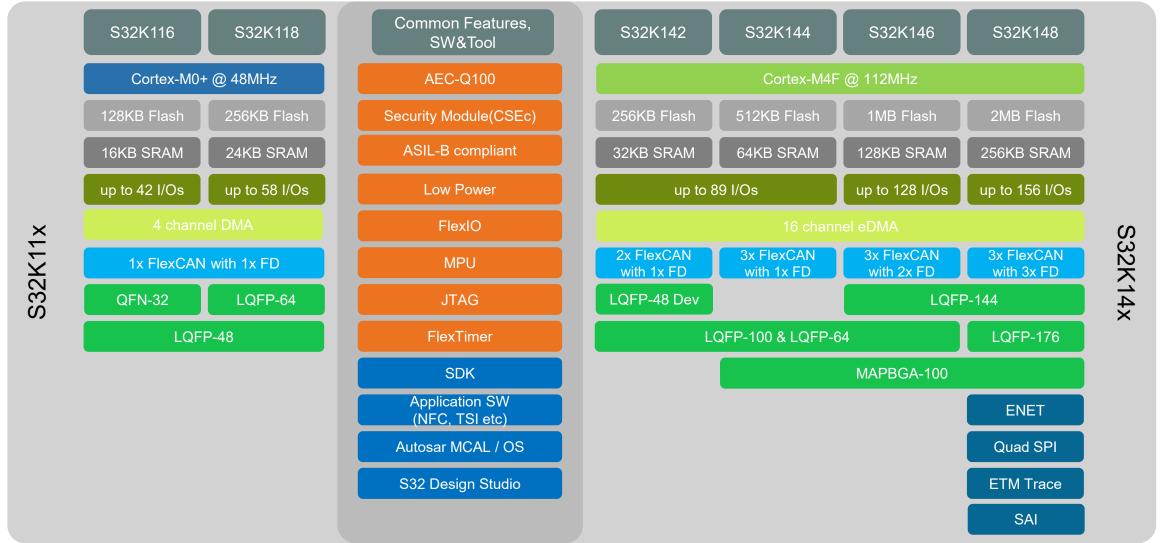

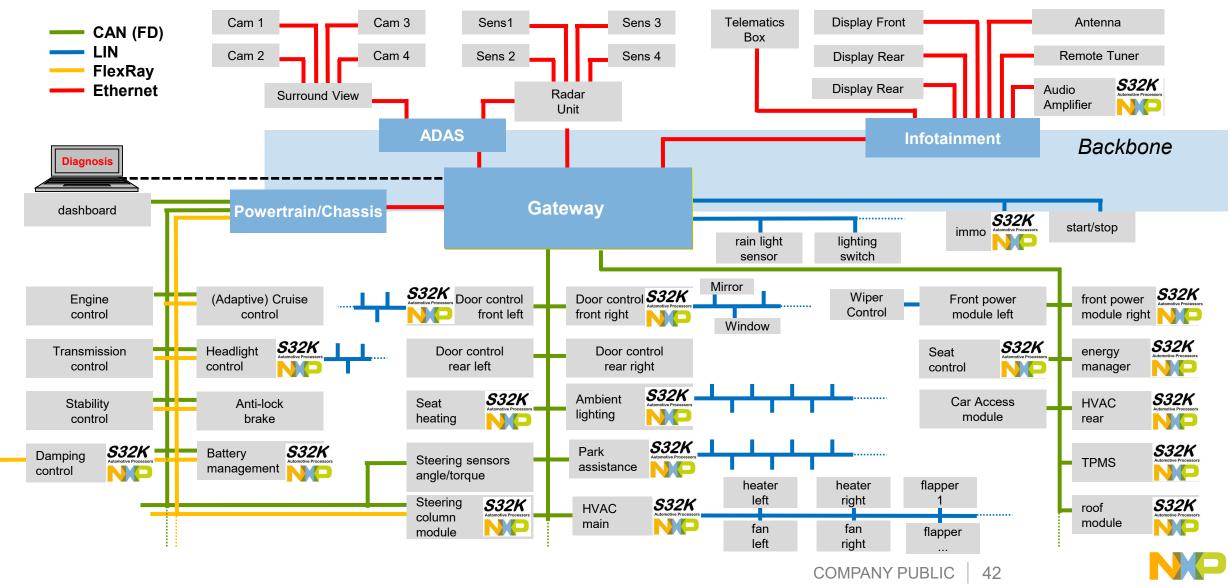

# S32K Product Family – S32K14x and S32K11x

# S32K – Solutions for Automotive Edge Nodes

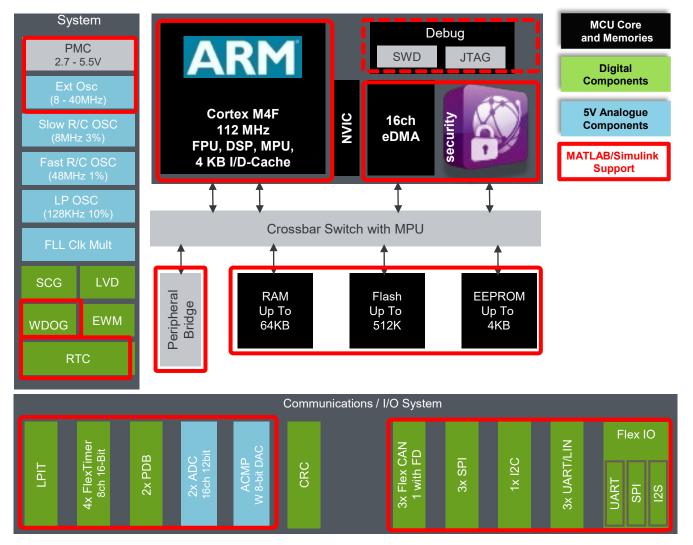

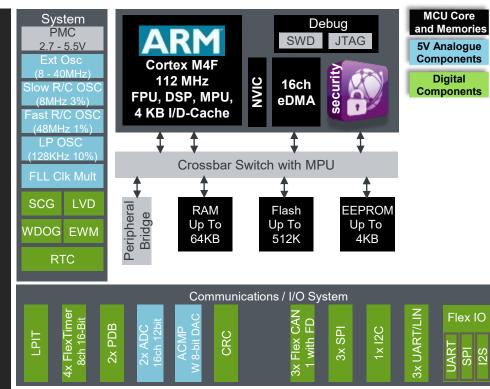

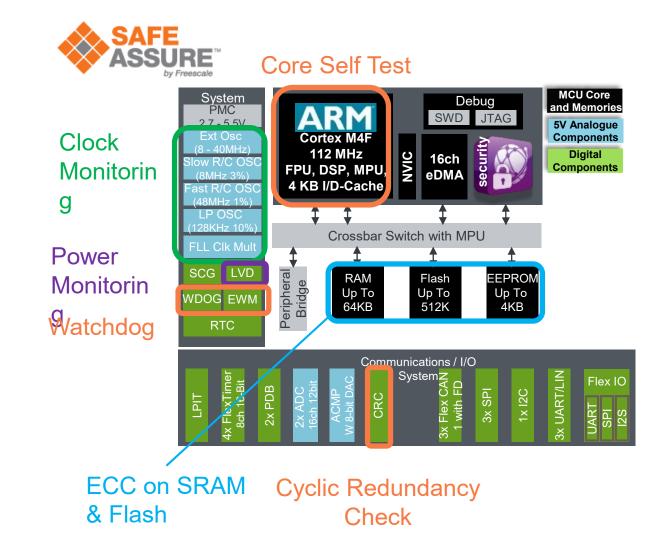

### S32K144 – Block Diagram

#### High performance

- ARM Cortex M4F up to 112MHz w FPU

- eDMA from 57xxx family

#### **Software Friendly Architecture**

- High RAM to Flash ratio

- · Independent CPU and peripheral clocking

- 48MHz 1% IRC no PLL init required in LP

- Registers maintained in all modes

- Programmable triggers for ADC → no SW delay counters or extra interrupts

#### **Functional safety**

- ISO26262 support for ASIL B or higher

- Memory Protection Unit

- ECC on Flash/Dataflash and RAM

- Independent internal OSC for Watchdog

- Diversity between ADC and ACMP

- Diversity between SPI/SCI and FlexIO

- · Core self test libraries

- Scalable LVD protection

- CRC

#### Low power

- · Low leakage technology

- Multiple VLP modes and IRC combos

- Wake-up on analog thresholds

#### Security

• CSEc (SHE-spec)

#### Packages & IO

- Open-drain for 3.3 V and hi-drive pins

- Powered ESD protection

- Packages: 100 BGA, 64 LQFP, 100 LQFP

#### **Operating Characteristics**

- Voltage range: 2.7V to 5.5V

- Temperature (ambient): -40°C to +125°C

#### **Memories**

- 512KB Flash memory

- 64kB SRAM

- 4kB EEPROM

#### **Communication Interfaces**

- 3x LPUART

- 1x LPSPI

- 1x LPI2C

- 3x FlexCAN

- 1x FlexIO

(configurable for UART, SPI, I2C & I2S)

#### **Analog Peripherals**

- 2x 12bit ADC w/ up to 16 channels

- 1x CMP w/ 8bit DAC

#### **Timers Peripherals**

- 4x FTM with 8 channels

- 2x PDB with 2 channels

- Low Power Interrupt Timer (LPIT)

- Low Power Timer (LPTMR)

- · Real Time Clock (RTC)

### S32K – Solution for Industrial

S32K MCUs deliver quality, reliability and safety for challenging environments found in industrial, automation, communications, transportation, medical and A&D applications.

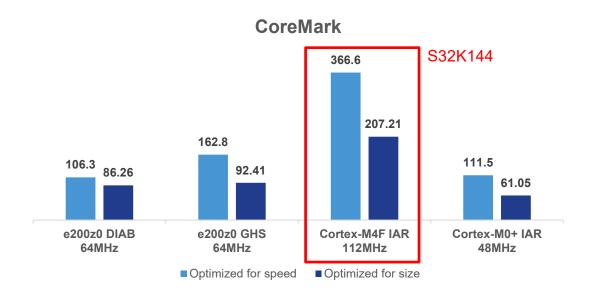

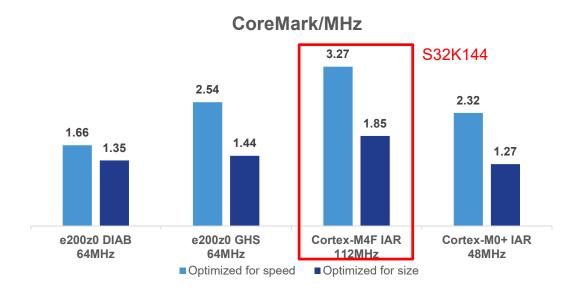

### S32K - Performance

### S32K – Low Power Performance

| MCU/Core<br>Type | Ta (C)    | VLSP (uA) | VLPR (mA) | Stop 1 (mA) | Run (mA) |

|------------------|-----------|-----------|-----------|-------------|----------|

| S32K116/M0       | 25 (typ)  | 26        | 1.9       | 7           | tbd      |

| S32K118/M0       | 25 (typ)  | 26        | 1.9       | 7           | tbd      |

| S32K142/M4       | 25 (typ)  | 29        | 1.9       | 10          | tbd      |

| S32K144/M4       | 25 (typ)  | 29.8      | 1.25      | 7           | 39.6     |

|                  | 105 (typ) | 256.3     | 1.48      | 7.8         | 40.5     |

|                  | 125 (max) | 1492      | 2.71      | 12.2        | 46       |

| S32K146/M4       | 25 (typ)  | 40        | 5         | 15          | tbd      |

| S32K148/M4       | 25 (typ)  | 40        | 5         | 15          | tbd      |

### S32K – ASIL-B Functional Safety

- Safety Hardware

- Power supplies

- Clocks generation

- Core platform (core, DMA, cache ...)

- Busses XBAR

- Memories NVM, SRAM

- Safety Process

- ISO 26262 development process

- Safety Support

- FMEDA

- Safety manual

- Technical support

- Safety Software

- S32K core self-test SW,

# S32K Functional Safety SW

- Cortex-M Core Self-Test Library: Structural Core Self-Test Library (SCST) is a safety measure against permanent faults in the cores

- Developed for detecting hardware permanent faults in a core by means of executing machine opcodes with fixed set of operands and comparing their execution results

- This library is considered as Safety Element out of Context and was developed according to ASIL B

- SCST library provides tests to achieve the claimed diagnostic coverage (analytically estimated)

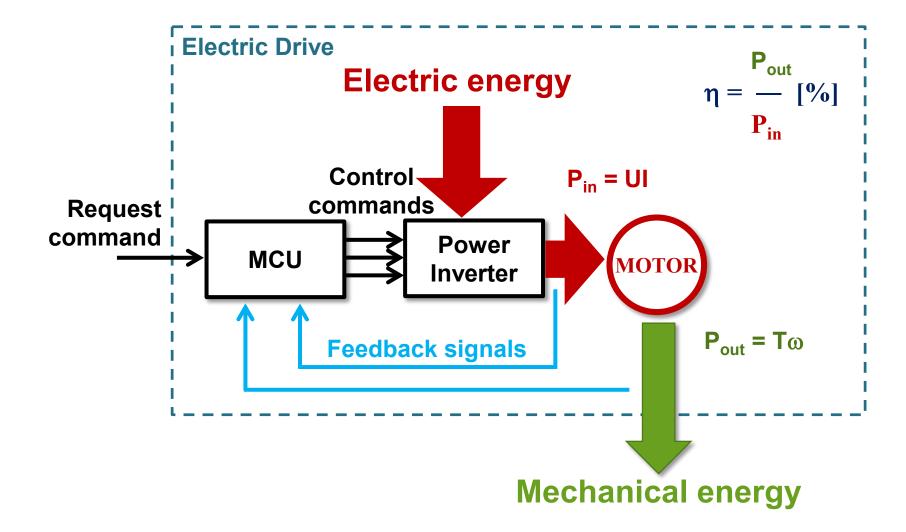

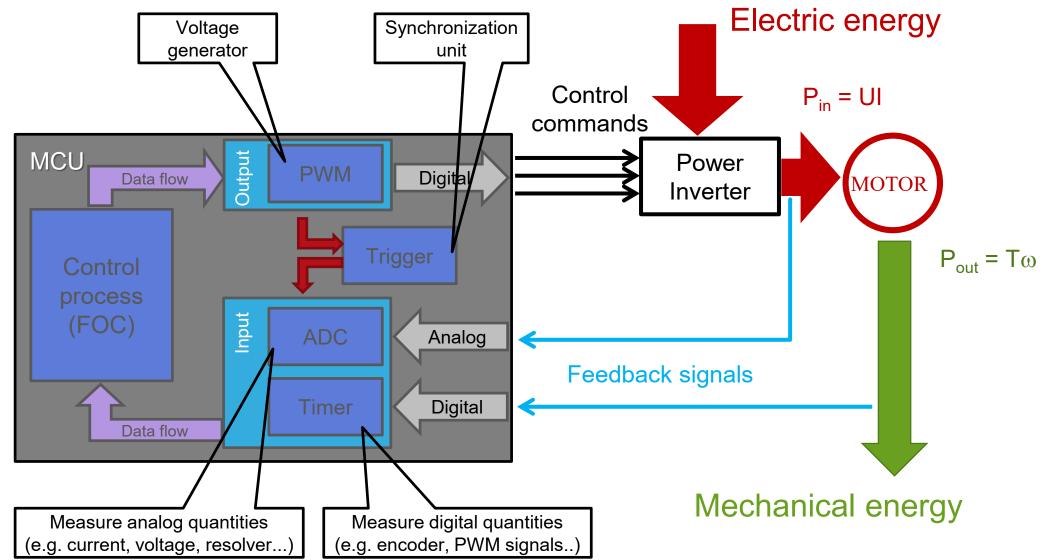

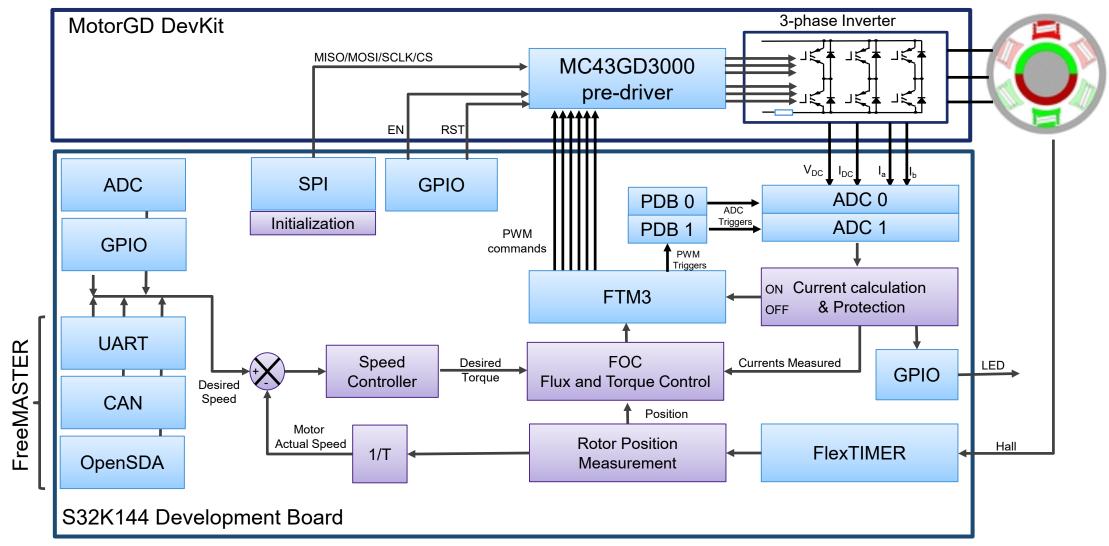

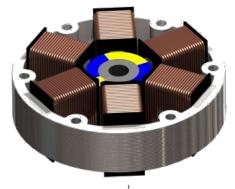

### Motor Control Drive Concept

### Motor Control Loop Implementation – Generic

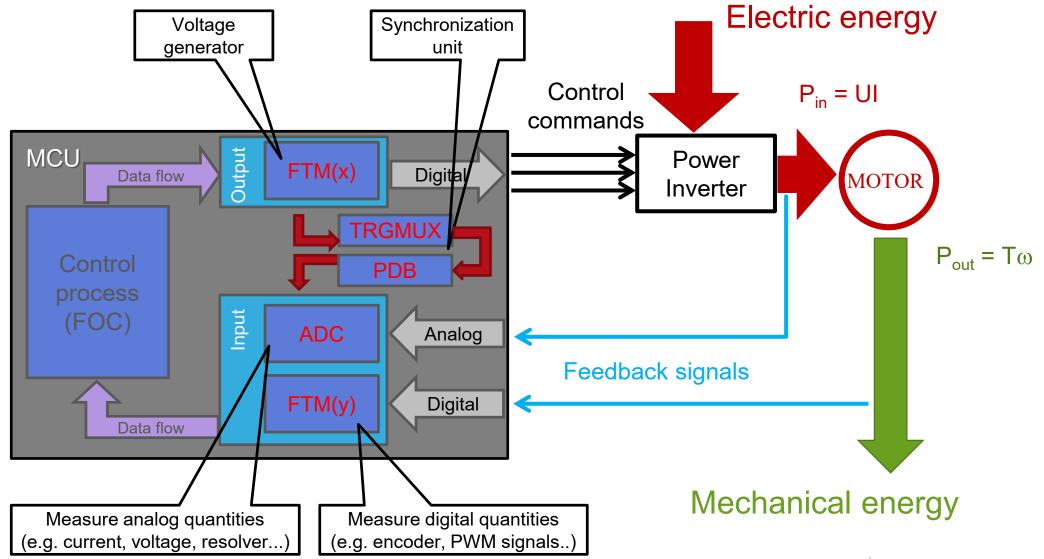

### Motor Control Loop Implementation on S32K

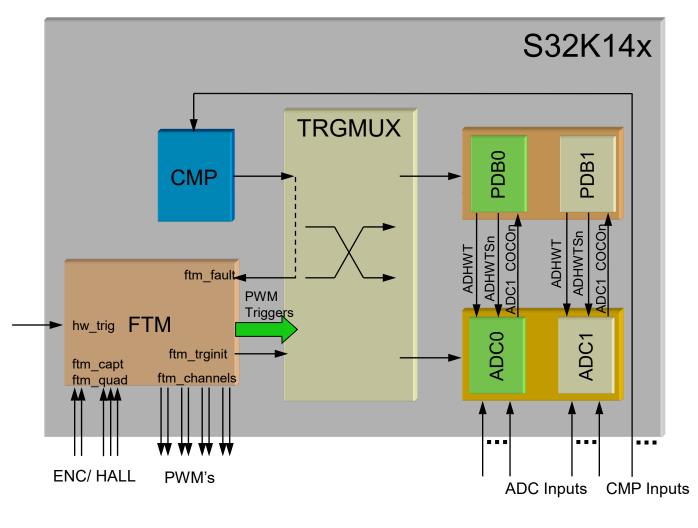

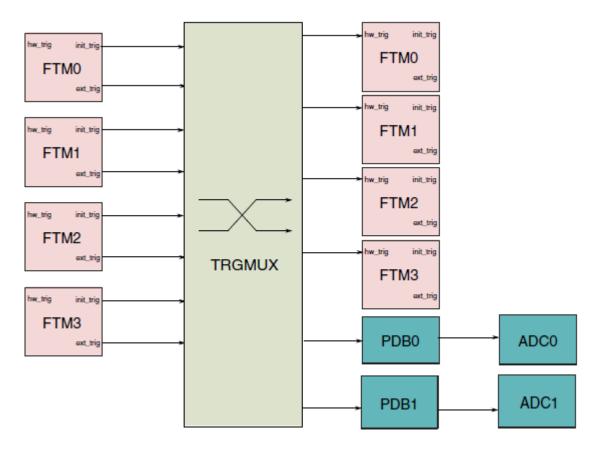

### S32K144 Motor Control Specific Modules

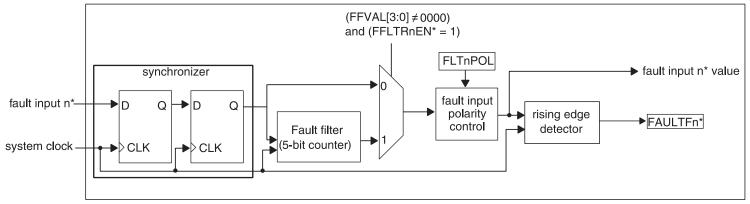

#### **CMP**

- In MC as a fault protection unit

- Up to 8 channels some shared with ADC channels

- 8bit internal DAC

#### FTM0/1/2/3

- Various PWM modes

- Sync of double buffered registers

- Double buffered registers with various sync schemes

- Fault control

- SW Control & Masking

- Triggers generator for PDB or directly for ADC

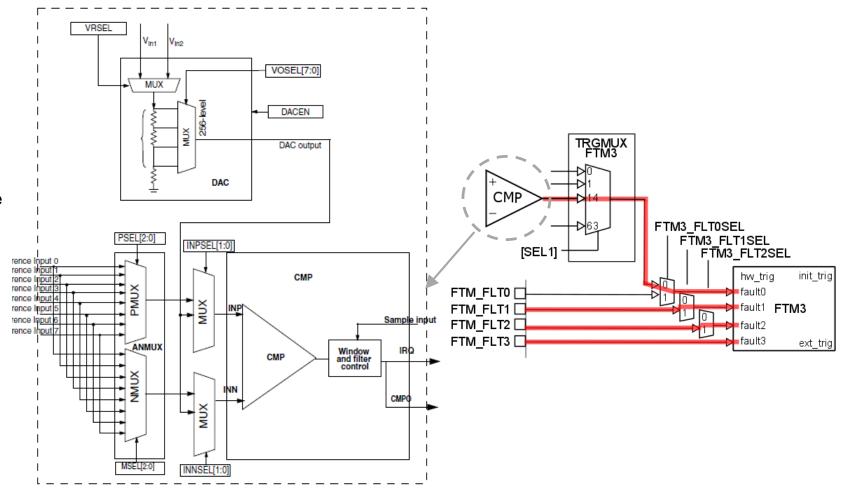

#### **TRGMUX**

- Each peripheral has 32-bit trigger control register

- Each control register support up to 4 triggers

- Each trigger can be selected from up to 64 inputs.

#### PDB0/1

- 16bit delay and triggering unit for ADC

- Two channels and each channel has 8 pretriggers

- Back-to-back operation

- DMA support

#### ADC0/1

- 12bit resolution

- Up to 16 channels some of them interleaved & shared with analog CMP

- HW average function

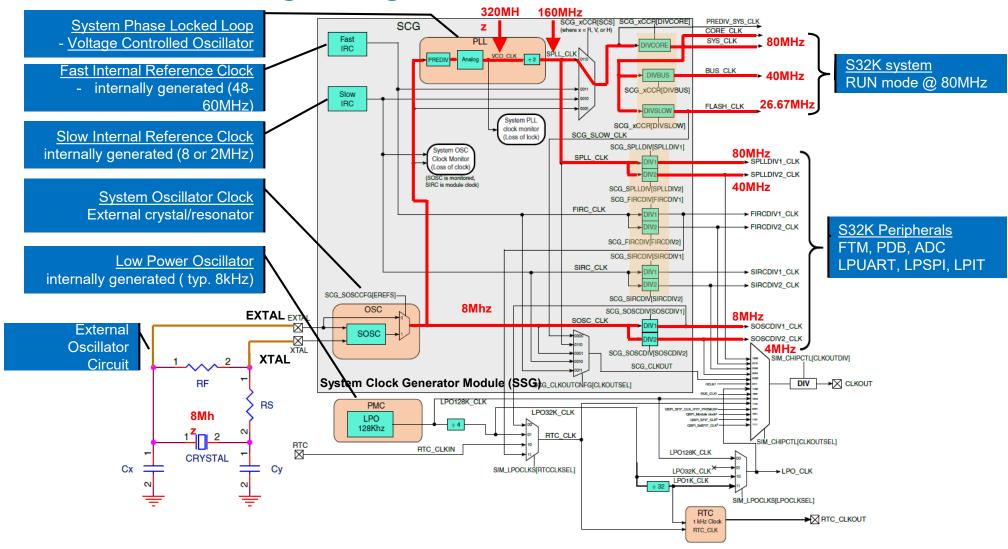

### S32K144 Clocking Diagram

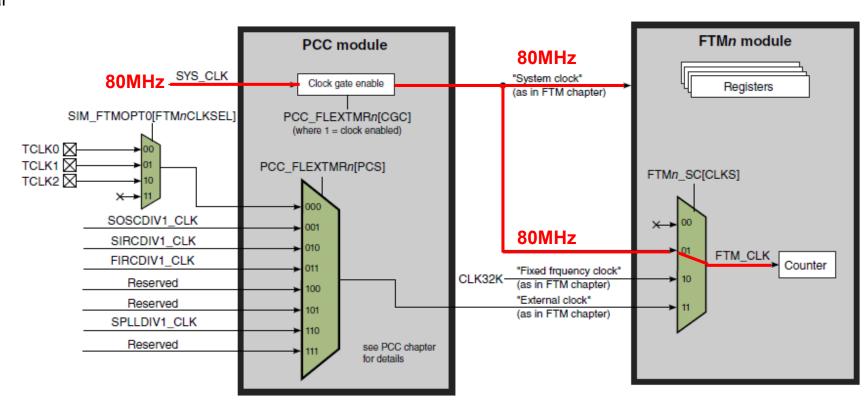

### S32K144 Clock Source of FlexTimer

- Clock selection in Peripheral Clock Controller (PCC) – PCC\_FTMn register

- FTM module needs two clock sources:

- Module clock

- Clock for FTM counter

- Source clock for FTM counter:

- External clock source

- Divided OSC

- Divided FIRC (48MHz-60MHz)

- Divided SIRC (8 or 2Mhz)

- Divided PLL

- System clock (80MHz) to get the maximum PWM resolution

### S32K144 FlexTimer Features

- 4 x FTM, with 8 channels (inputs/outputs)

- FTM source clock is selectable with prescaler divide-by 1, 2, 4, 8, 16, 32, 64, or 128

- FTM has a 16-bit counter

- The counting can be up or up-down

- Each channel can be configured for input capture, output compare, or PWM generation

- New combined mode to generate a PWM signal (with independent control of both edges of PWM signal)

- Complementary outputs, include the deadtime insertion

- Software control masking of PWM outputs

- Up to 4 fault inputs for global fault control

- The polarity of each channel is configurable

- The generation of an interrupt per channel input capture/compare, counter overflow, at fault condition

- Synchronized loading of write buffered FTM registers

- Write protection for critical registers

- Dual edge capture for pulse and period width measurement

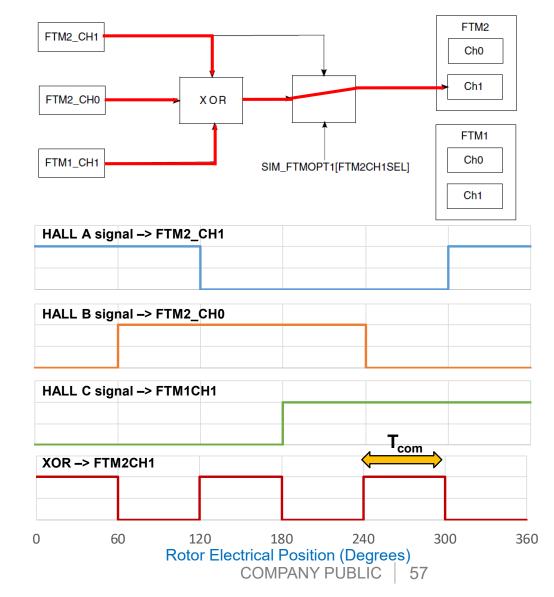

# S32K144 FlexTimer – Input Capture Mode

- Single or Dual Edge Capture mode for pulse or period width measurement

- Configurable capture events on rising, falling or both edges

- · Input filter for some channel inputs

- When selected edge occurs, current FTM counter value is captured into the CnV register and interrupt is generated, if enabled

- HALL sensor support for position detection and speed calculation of an electric motor

- FTM2\_CH1 can be configures as normal input or the XOR of FTM2\_CH0, FTM2\_CH1 and FTM1\_CH1 that will be applied to FTM2\_CH1

- Rotor speed is calculated based on the captured time every rising/falling edge

- $\omega_{mech} = \frac{360^{\circ}}{pT_{com}}$

- Rotor position is determined according to the HALL logic captured by GPIO input

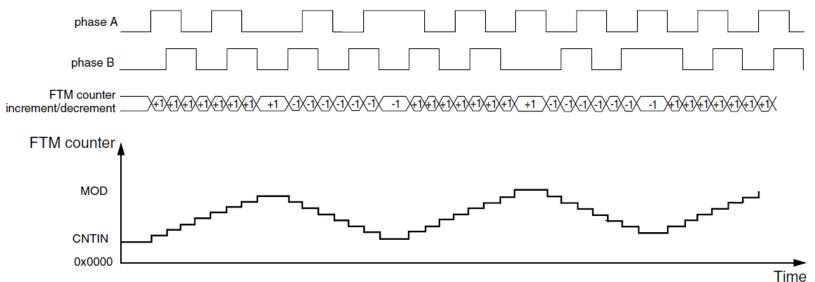

### S32K144 FlexTimer – Quadrature Decoder Mode

- Dedicated feature to process Phase A and Phase B signals generated by rotary or linear sensors to determine rotor/slider position and speed

- Phase A and Phase B input signals control FTM counter increment and decrement

- Phase A and Phase B input signals can be additionally filtered

- Two sub-modes available in quadrature mode:

- Count and Direction Encoding mode

- Phase A and Phase B Encoding mode

- 1024 pulses rotary encoder sensor MOD value is set to 4x1024=4096 and CNTIN is set to 0

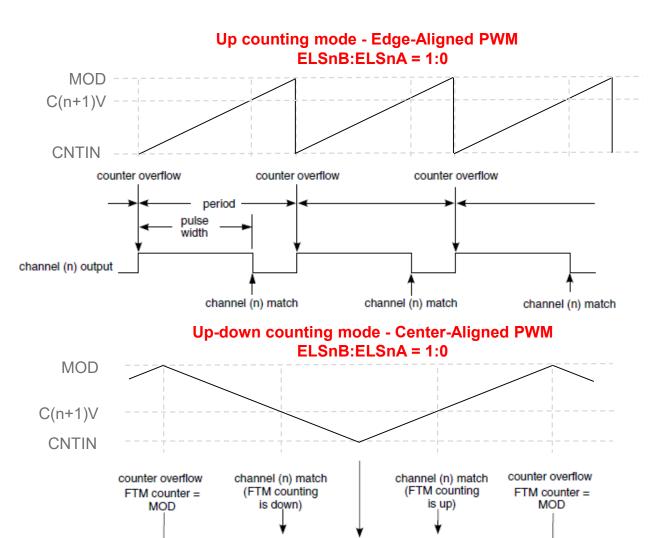

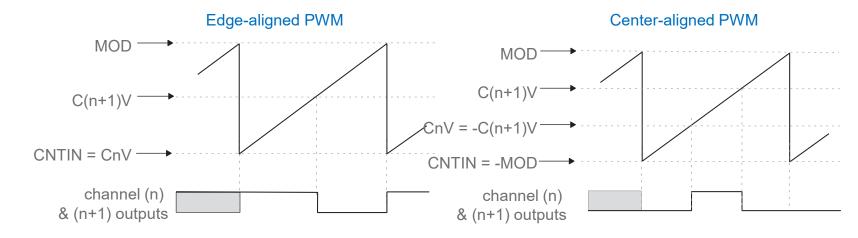

### **PWM Modes**

- **Up counting** mode

- For Edge-Align PWM

- ELSnB:ELSnA bits define pulse polarity

- PWM period = MOD CNTIN

- Duty cycle = CnV CNTIN

- Up-down counting mode

- For Center-Align PWM

- ELSnB:ELSnA bits define pulse polarity

- PWM period = 2x (MOD-CNTIN)

- Duty cycle = 2x (CnV CNTIN)

- In up counting mode even (n) and odd channels (n+1) can work as a pair in combine mode & complementary mode

pulse width = 2 x (CnV - CNTIN)

2 x (MOD - CNTINCNTIN)

channel (n) output

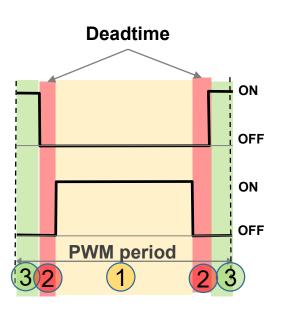

# PWM Modes (Cont'd)

- In Combine mode two FTM channels are combined together to define one PWM signal

- An even channel (n) defines rising edge of PWM signal

- An adjacent odd channel (n+1) defines falling edge of PWM signal

- PWM period = MOD CNTIN

- Duty cycle = C(n+1)V C(n)V

#### Complementary mode

Channel (n+1) output is the inverse of the channel (n)

#### Deadtime insertion

Clock source for deadtime delay is the FTM input clock divided by deadtime prescaler value DTPS (1, 4, 16)

#### Complementary mode of Edge-aligned PWM

#### Complementary mode of Center-aligned PWM

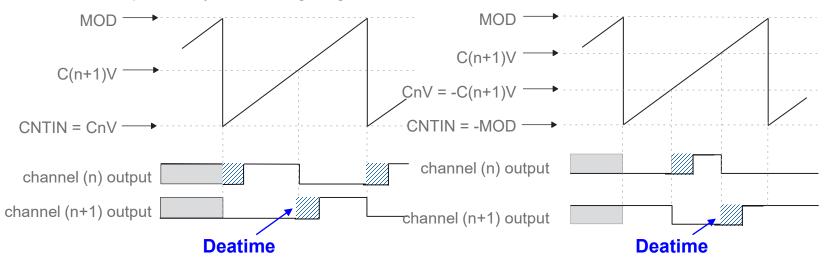

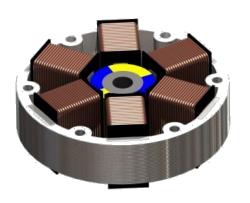

### Advanced Peripherals Reduce Motor/Generator Size

- High Resolution PWM (Pulse Width Modulator) Peripheral is key to design powerful electric motors at reduced cost:

- Motor/Generator to be small and powerful (not to carry unnecessary mass/space).

shall be designed to work at high electric frequency (~1 kHz high number of poles).

- Generation of high electric frequency 3-phase system requires high resolution PWM, both in time and amplitude

- FTM ~ 12bit resolution at 80MHz input clock frequency

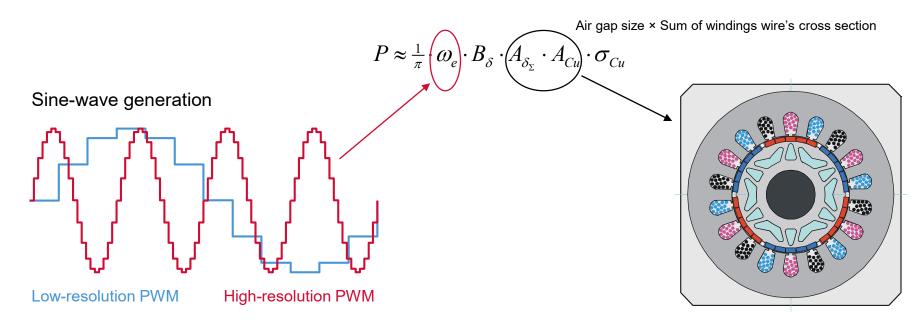

# S32K144 FlexTimer – PWM Synchronization

channel (n+1) match ---

FTM counter

channel (n) match

- PWM synchronization provides an opportunity to force FTM counter to the CNTIN value and opportunity to update MOD, CNTIN, CnV, OUTMASK, INVCTRL, SWOCTRL registers with their buffered value

- The commutation event timing depends on the rotor position and it is asynchronous to PWM (may occur anytime during the PWM cycle)

- FTM3 can be synchronized by FTM0 init trigger

trigger dissabled

[SEL0] -

trigger dissabled

trigger input 1

trigger input 63

[SEL3]

trigger input 1

hw\_trig init\_trig

FTM0

ext trig

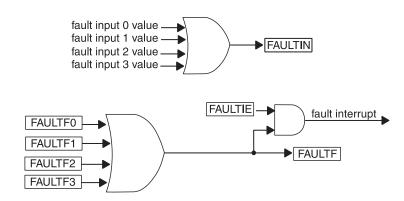

### S32K144 FlexTimer – Fault Control

- To protect system in critical moments:

over-current, under-voltage, over-temperature...

- 4 fault inputs OR-ed into single fault signal

- Fault signal disables all PWM outputs

- The polarity of a fault signal is user configurable

- All fault inputs have configurable dig. input filter

- Automatic or Manual fault clearing:

- AFC at new PWM cycle

- MFC at new PWM cycle, FAULTF has to be cleared

# S32K144 Analog Comparator (CMP)

- CMP output can be used as a fault input signal of FTM module

- Up to 8 independently selectable channels for positive and negative comparator inputs

- Some channels are shared with ADC input pins

- Internal 8-bit DAC with range of reference voltage:

- 3.9mV from 0 to 1V or

- 19mV over full 5V range

- Configurable hysteresis Control

- CMP output :

- Sampled

- Digitally filtered

- Windowed (via PDB or LPIT)

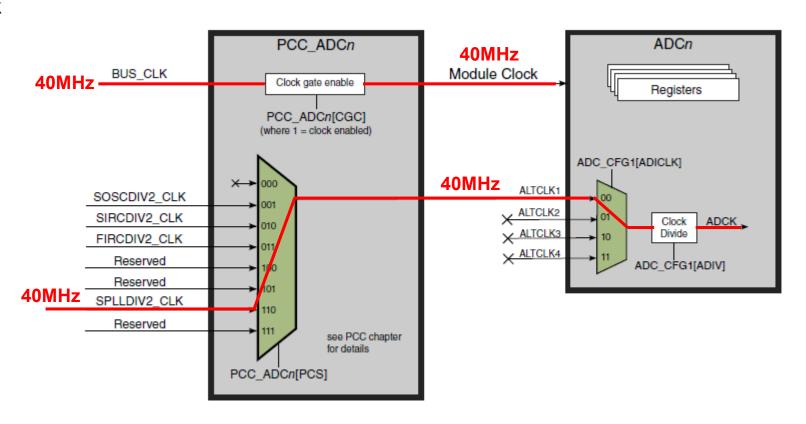

### S32K144 Clock Source for ADC

- Clock selection in Peripheral Clock Controller (PCC) – PCC\_ADCn register

- ADC module needs two clock sources:

- Module clock

- Asynchronous clock

- Asynchronous clock sources:

- Divided SOSC (SOSCDIV2\_CLK)

- Divided FIRC (48MHz-60MHz)

- Divided SIRC (SIRCDIV2 CLK)

- Divided SPLL (SPLLDIV2\_CLK = 40MHz)

- For short sample and maximum frequency 40 MHz  $T_{conv}$  = 1.25us

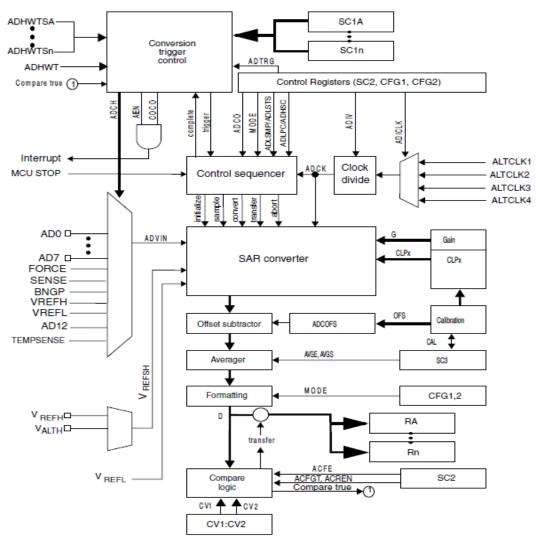

### S32K144 ADC Block Diagram

- Up to 16 single-ended external analog inputs some of them can be hardware interleaved:

- ADC0\_SE4 and ADC1\_SE14

- ADC0\_SE5 and ADC1\_SE15

- ADC1\_SE8 and ADC0\_SE8

- ADC1\_SE9 and ADC0\_SE9

- Input clock selectable from up to four sources (f<sub>ADCLK</sub> = 50 MHz)

- Self-Calibration mode

- Single or continuous conversion

- Hardware average function

- Automatic compare with interrupt for less-than, greater-than or equal-to, within range, or out-of-range, programmable value

- Programmable sample time and conversion speed/power (For short sample and 56 MHz frequency  $T_{conv} = 0.89us$ )

- DMA support

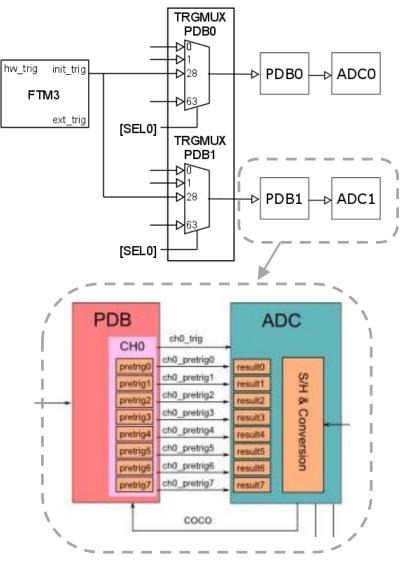

# S32K144 ADC Triggering by PDB

- ADC can be triggered by SW or HW

- Several hardware trigger sources: LPIT, CMP... routed through TRGMUX

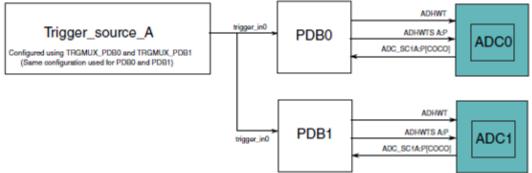

- One ADC and one PDB work as one pair: PDB0-ADC0, PDB1-ADC1

- PDB0 pre-triggers will connect directly to ADC0 ADHWTS ports to control the channels

- The ADC0 coco signals are directly feedbacked to PDB0 to deactivate the PDB lock state

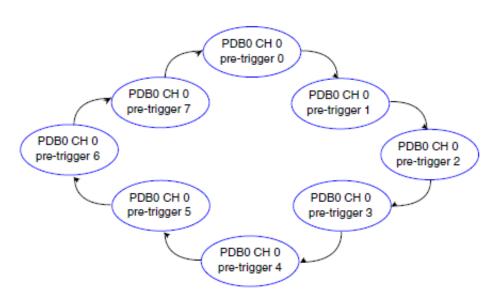

# S32K144 ADC Triggering by PDB (Back-to-back)

In **back-to-back** operation is enabled by CHnC1[BB[m]] bit and each *m* pre-trigger delay is ignored

PDB acknowledgment = COCO[n]

All acknowledgments are implemented in each PDB module FTM\_init\_trig

as a ring

**Back-to-Back Operation**

### S32K144 PDB Benefits

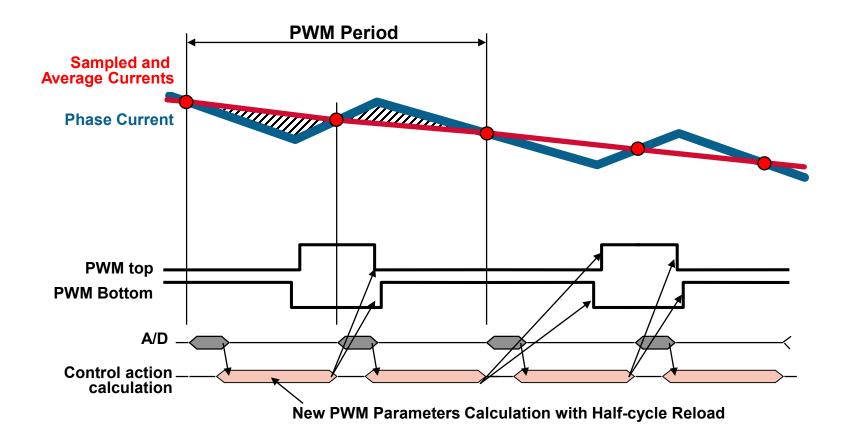

- ADC Sampling helps to filtering the measured current anti-aliasing

- Noise free ADC sampling when the power switch is not acting

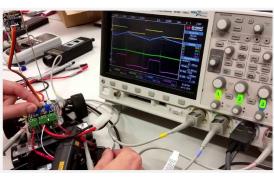

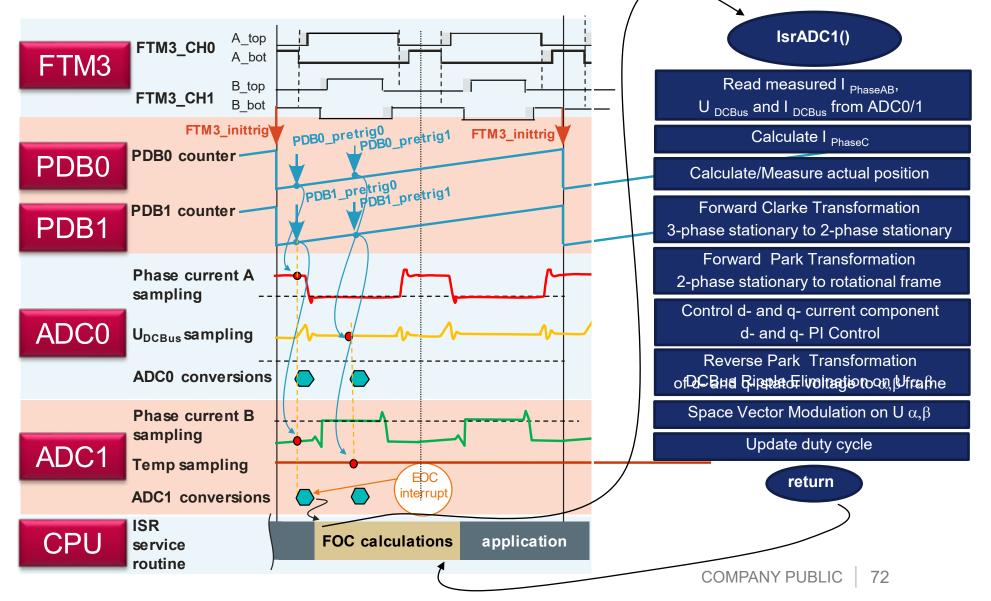

# Practical FOC Implementation with NXP S32K Evaluation Boards

FTM-PDB-ADC Synchronization

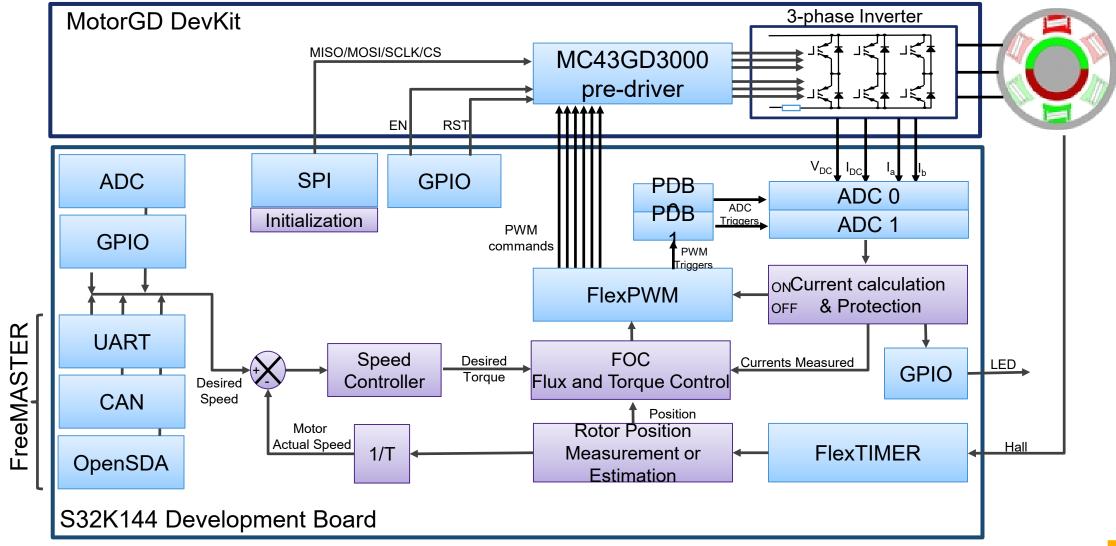

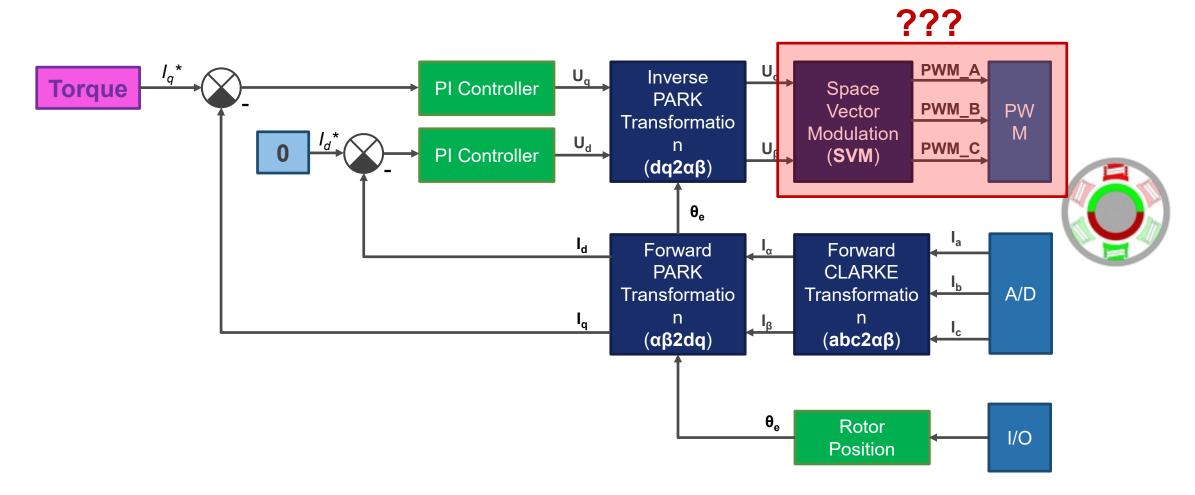

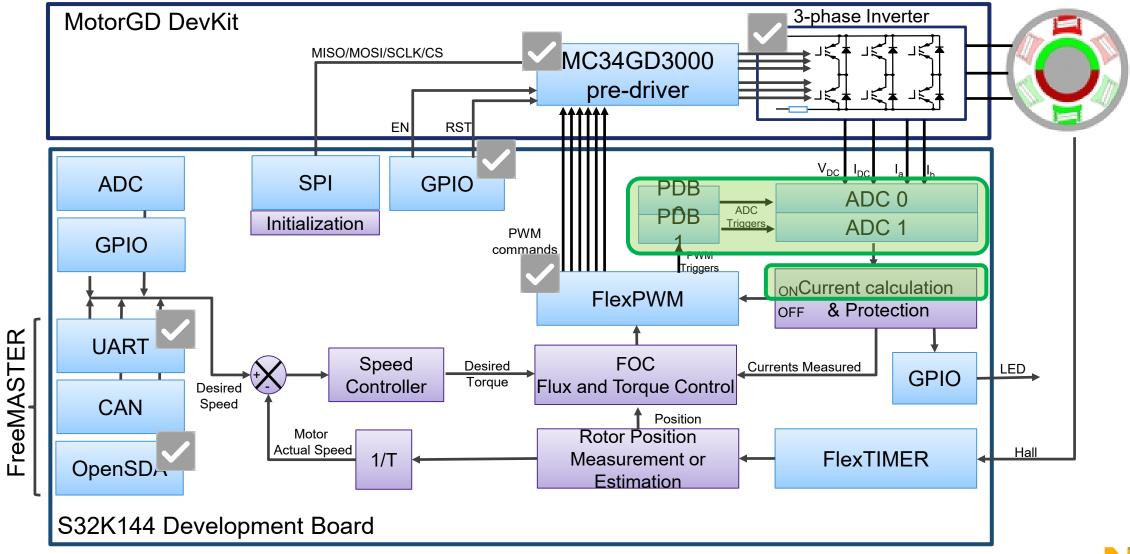

# PMSM FOC Block Diagram

S32K144 Modules Involvement in PMSM FOC Control Loop

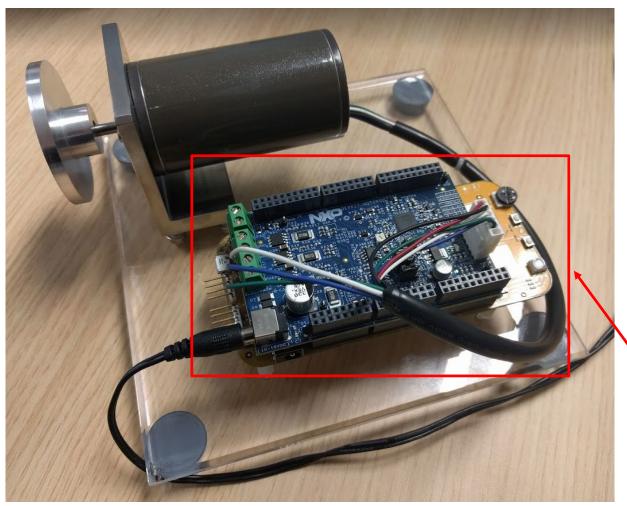

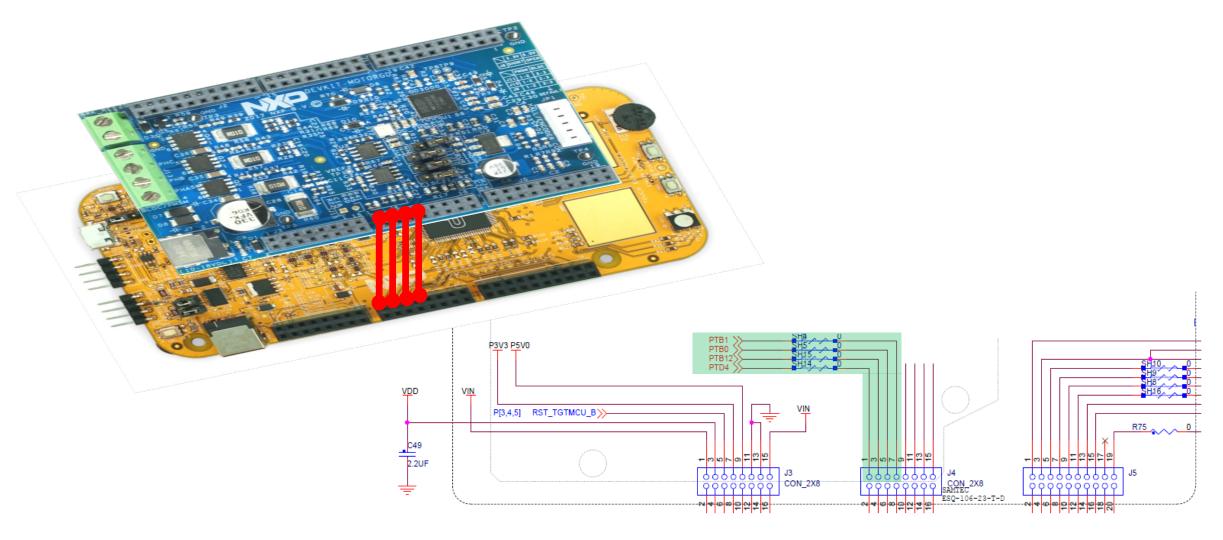

### MTRDEVKSPNK144 – Motor Control Development Kit

#### LINIX Motor 45ZWN24-40 – Data Sheet

| Type<br>型묵   | No.of m<br>相数 | No.of p<br>极数 | Rated voltage<br>额定电压<br>VDC | Rated current<br>额定电流<br>A | Rated torque<br>额定转矩<br>g.cm | Rated power<br>额定功率<br>W | Rated speed<br>额定转速<br>r/min |

|--------------|---------------|---------------|------------------------------|----------------------------|------------------------------|--------------------------|------------------------------|

| 45ZWN24-10   | 3             | 4             | 24                           | 0.8                        | 360                          | 10                       | 2600                         |

| 45ZWN24-13   | 3             | 4             | 24                           | 1.4                        | 800                          | 13                       | 1600                         |

| 45ZWN24-15   | 3             | 4             | 24                           | 1.4                        | 700                          | 15                       | 2100                         |

| 45ZWN24-25   | 3             | 4             | 24                           | 1.8                        | 820                          | 25                       | 3000                         |

| 45ZWN24-30   | 3             | 4             | 24                           | 2                          | 900                          | 30                       | 3200                         |

| 45ZWN24-40   | 3             | 4             | 24                           | 2.3                        | 990                          | 40                       | 4000                         |

| 40ZVVINZ4-90 | 3             | 4             | 24                           | ე.0                        | 930                          | 90                       | 9350                         |

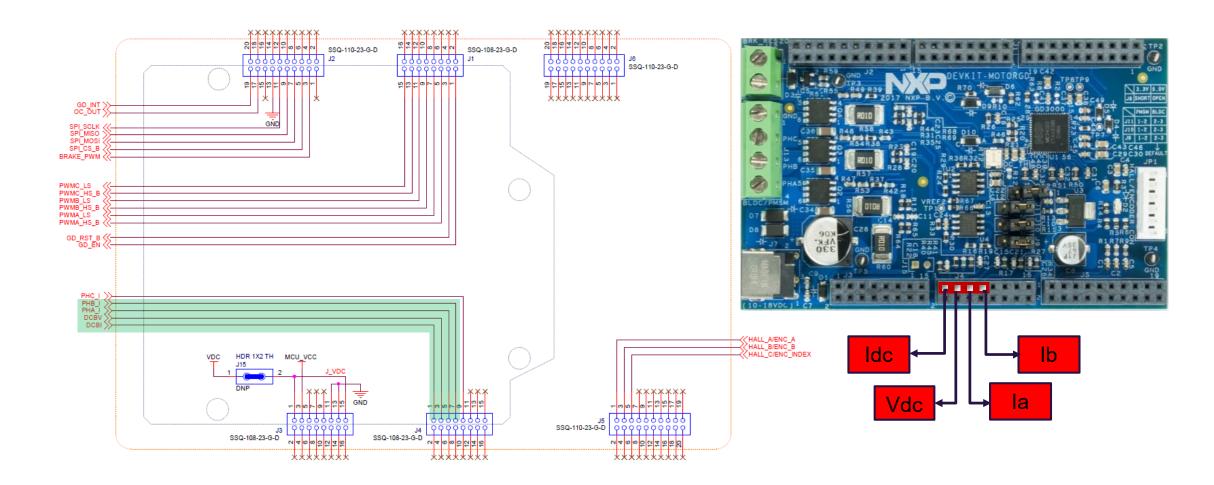

Control Tower: DEVKIT MOTORGD on top of S32K144EVB

\*All the parts can be bought and assembled separately \*Workshop is designed to be generic and valid for any other combination of S32K14x MCU and power inverter and 3 phase motors

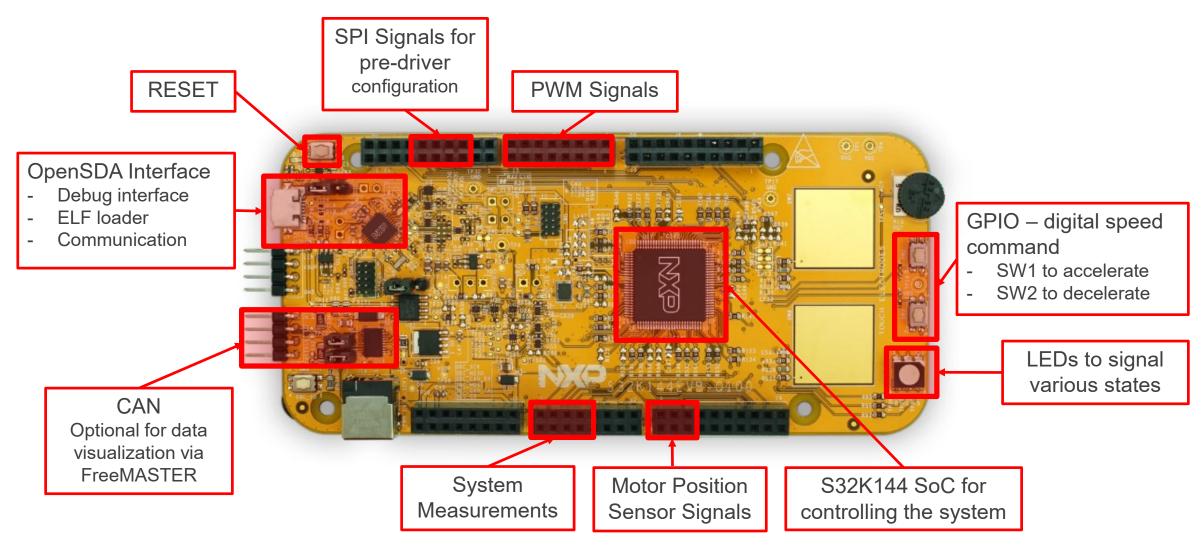

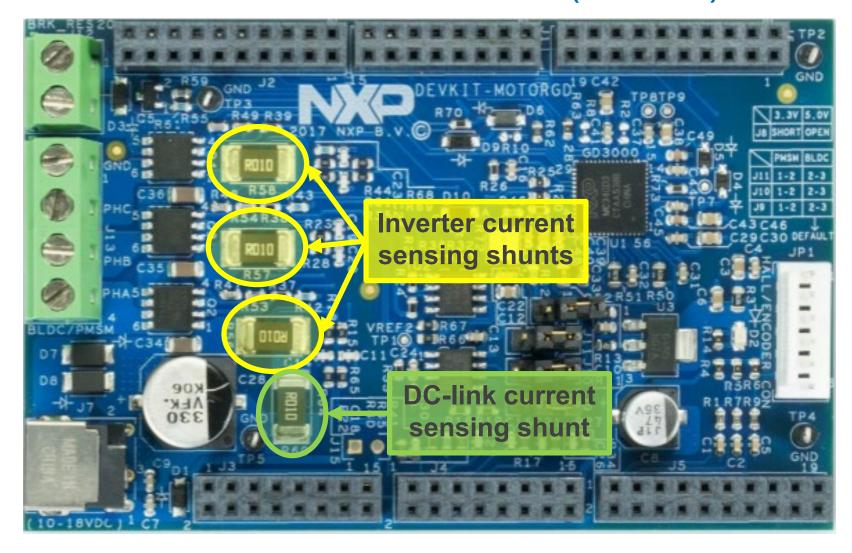

### S32K144EVB – Components Used During Workshop

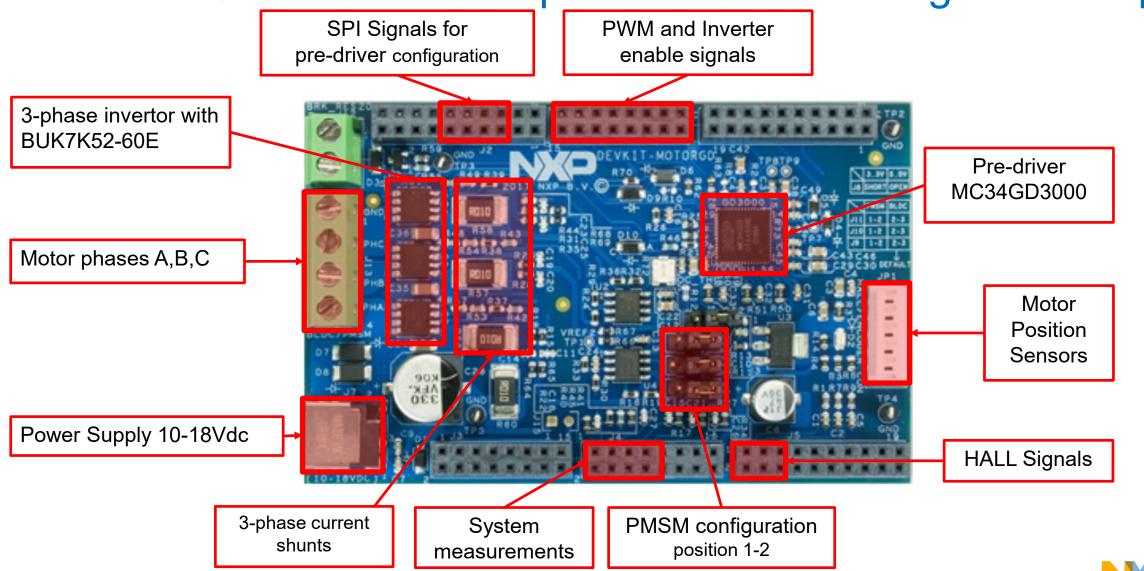

DEVKIT MOTORGD – Components Used During Workshop

# Agenda

- S32K Solutions

- S32K Motor Control Specific Modules

- -PMSM FOC

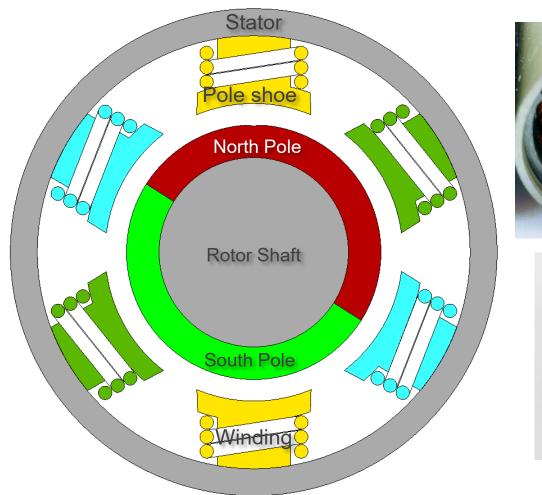

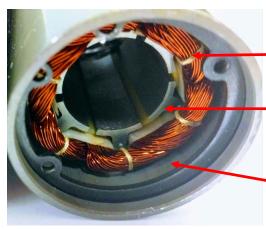

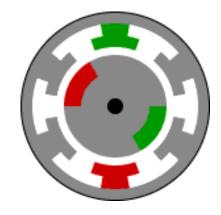

### PMSM – Construction Aspects

#### Stator parts:

- ◆ windings/coils form a 3 phase Y/∆ system energized with AC power

- pole shoe provides a low reluctance path for the magnetic flux

- frame/yoke forms a protective **∽**overing and support

#### Rotor parts:

- permanent magnets mounted on the surface (SPM) or interior (IPM) produces a constant magnetic flux

- shaft that transmits the mechanical torque

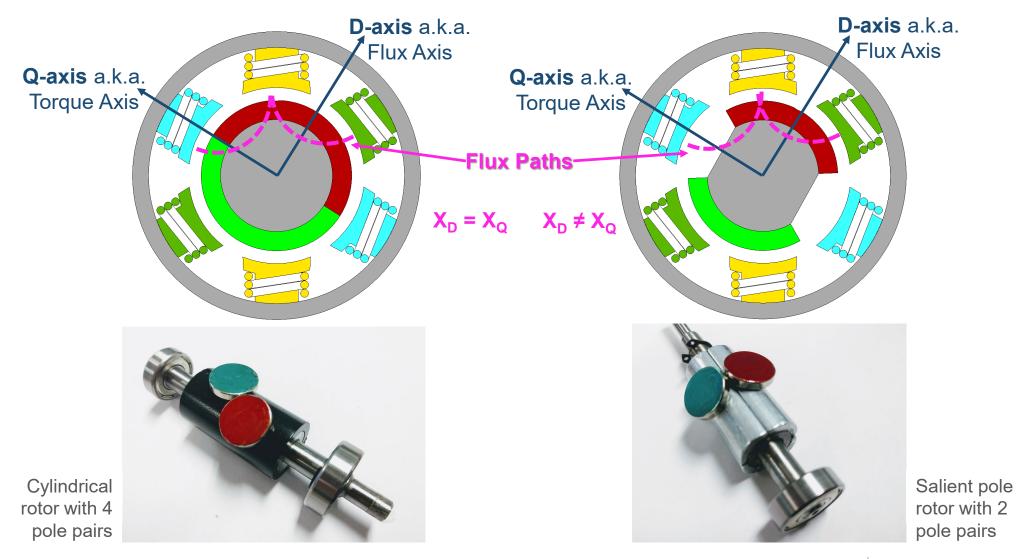

### PMSM – Cylindrical vs. Salient Pole Rotor Types

### BLDC vs. PMSM

#### **BLDC** motor

3-phase machine with PM on the rotor

Rotor position sensing required for rotor flux position

High torque per frame size

Synchronous operation

Trapezoidal Back-EMF

**Six-step commutation control**

**High torque ripple**

#### **PMSM** motor

= 3-phase machine with PM on the rotor

= Rotor position sensing required for rotor flux position

= High torque per frame size

= Synchronous operation

**≠** Sinusoidal Back-EMF

**≠** Field-oriented control

**≠** Low torque ripple

# BLDC vs. PMSM in Automotive Industry

### versus

| BLDC                          |                                                           | PMSM         |

|-------------------------------|-----------------------------------------------------------|--------------|

| HIGHER Level of torque ripple |                                                           | LOWER        |

| HIGHER                        | Vibration and noise as a consequence of the torque ripple | LOWER        |

| LOWER                         | Electromagnetic compatibility (EMC)                       | HIGHER       |

| LOWER                         | Control structure complexity level                        | HIGHER       |

| SHORTER                       | Execution time of the control approach                    | LONGER       |

| SIMPLE                        | Sensorless control                                        | MORE COMPLEX |

| HIGHER                        | Heating                                                   | LOWER        |

| LOWER                         | Price                                                     | HIGHER       |

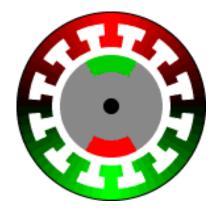

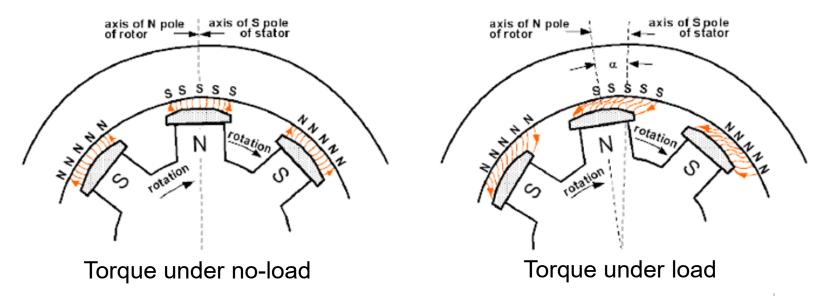

### PMSM – How is Torque Produced

- Attraction between stator and rotor magnetic poles cause the motor to spin

- Opposite polarity between rotor and stator facing poles create a strong magnetic field

- The mutual attraction between rotor and stator poles, locks the rotor in synchronism with rotating stator magnetic field

- Under no-load condition the rotor and stator pole axes are identical, while under load the axes of rotor poles will lag behind the stator pole axes but still turns at synchronous speeds

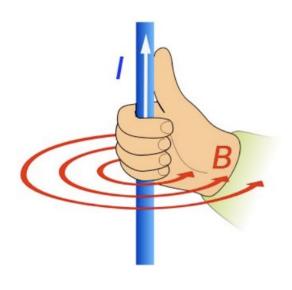

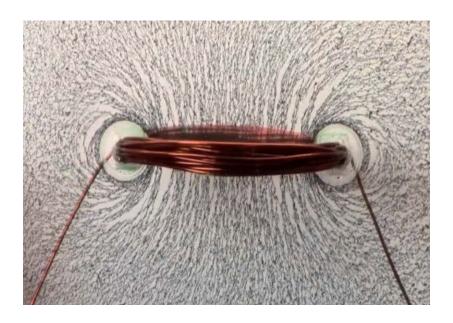

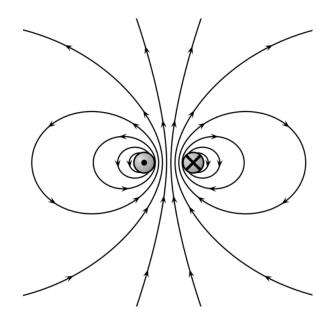

# PMSM – Magnetic Field Produced By Stator Windings

Magnetic field **B** around a conductor, produced by current **I**

Magnetic field produced by a coil/winding

Source: physics.stackexchange.com

Source: http://www.funscience.in

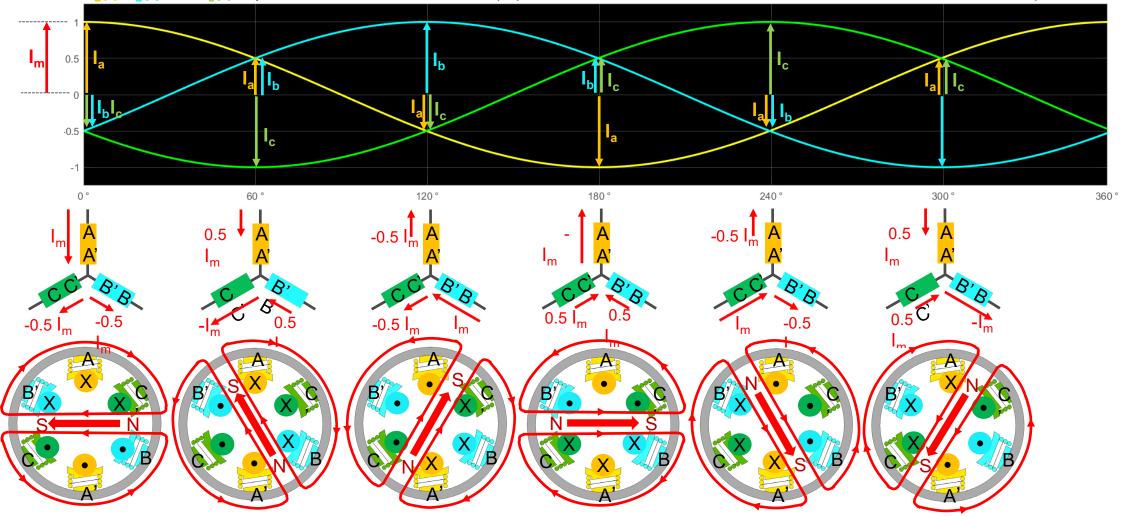

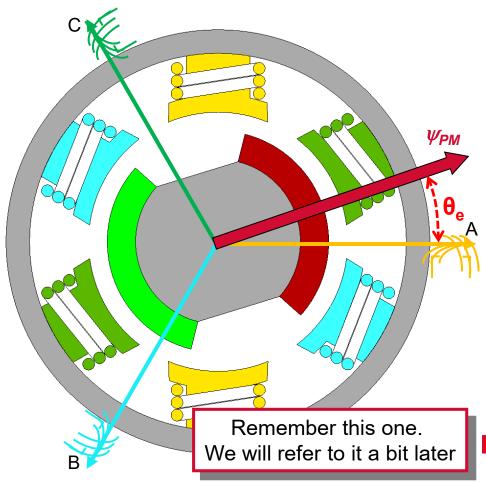

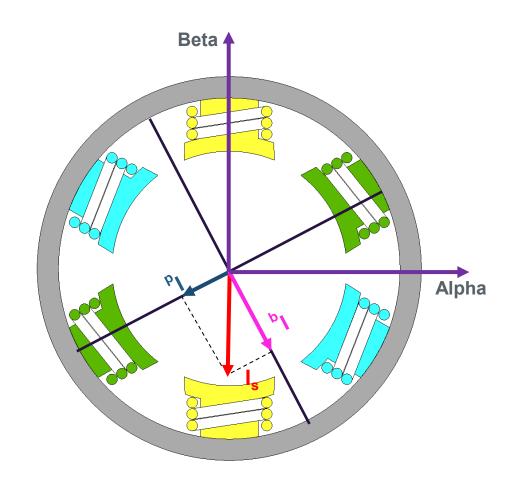

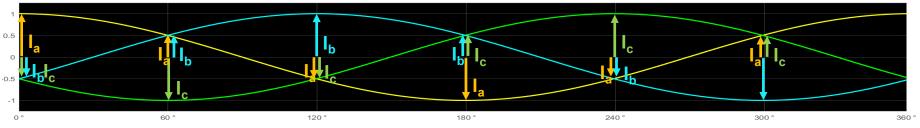

### PMSM – How Stator Rotating Magnetic Field is Produced

i<sub>a</sub>(t), i<sub>b</sub>(t) and i<sub>c</sub>(t) 3-phase AC balanced currents (a positive current is considered the one that enters the motor coil)

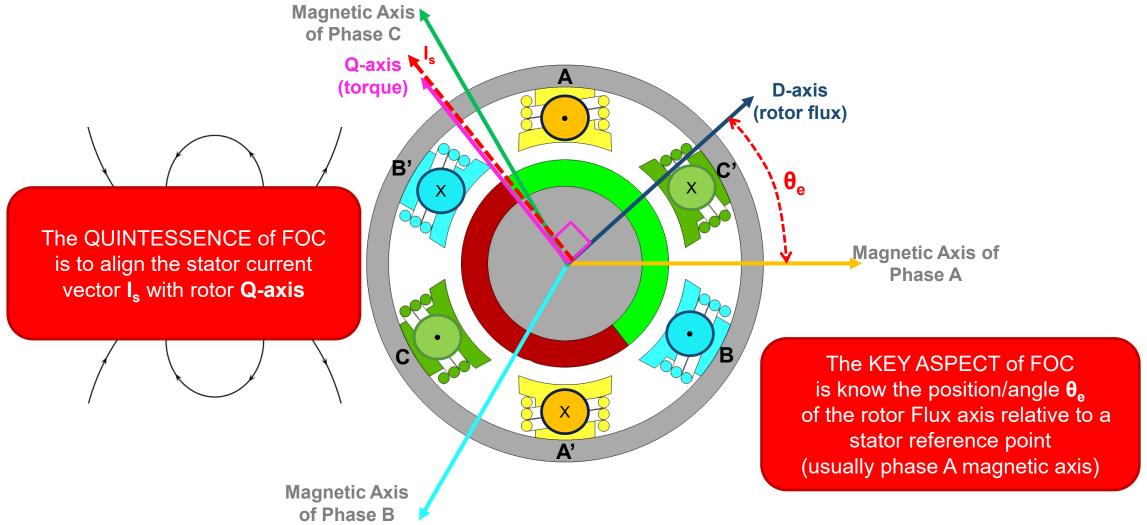

### PMSM – Field Oriented Control (FOC)

### PMSM – Why Should We Use FOC?

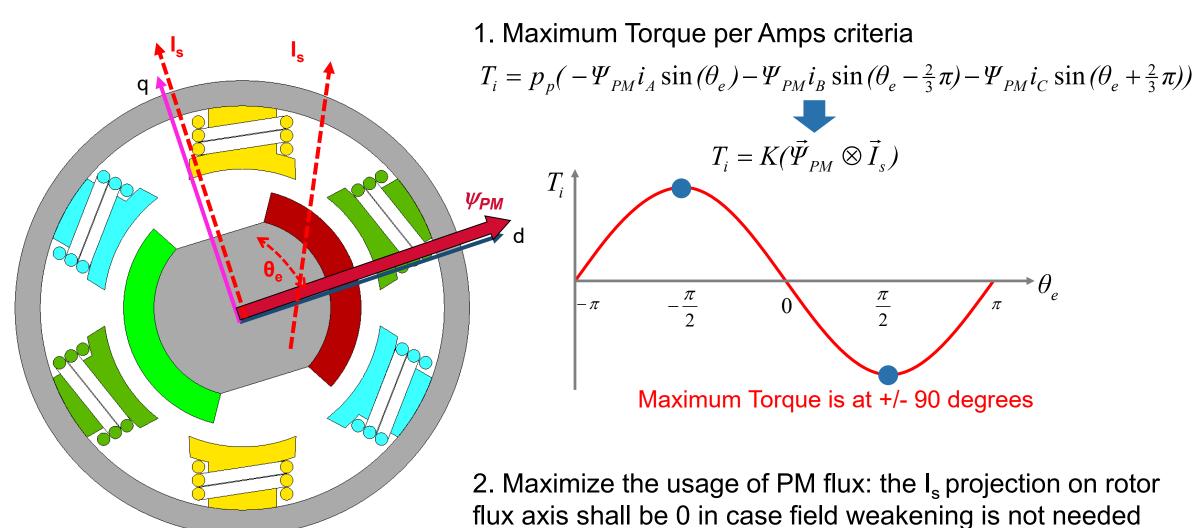

- For a PMSM motor the 3 sinusoidal phase currents i<sub>a</sub>, i<sub>b</sub> and i<sub>c</sub> have to be controlled to create a stator flux vector which is perpendicular to the rotor flux vector. (we will see later why 90 deg)

- Controllig the three sinusoidal currents independantly would be a very complex mathematical task since you have to track and regulate a sinusoidal reference.

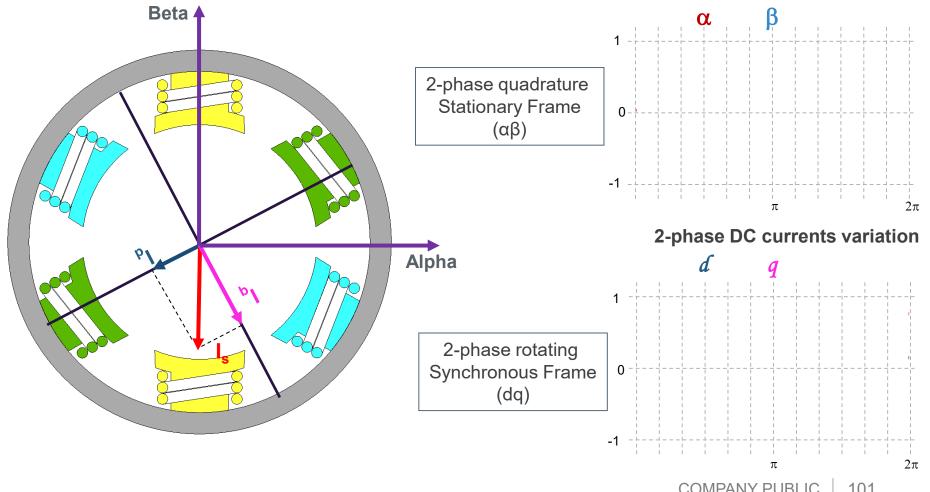

- FOC simplifies the math by transforming the 3 phase stationary system (abc) to a (dq) rotating synchronous with the rotor system.

- FOC decomposes the stator currents into two main components that can be controlled separately:

- magnetic field-generation (D-axis)

- torque generation (Q-axis)

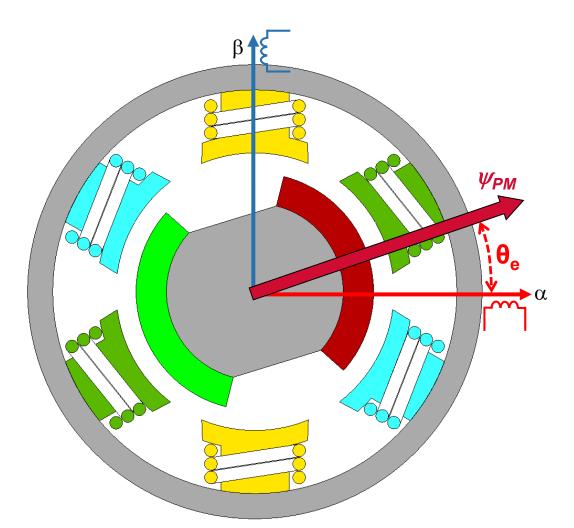

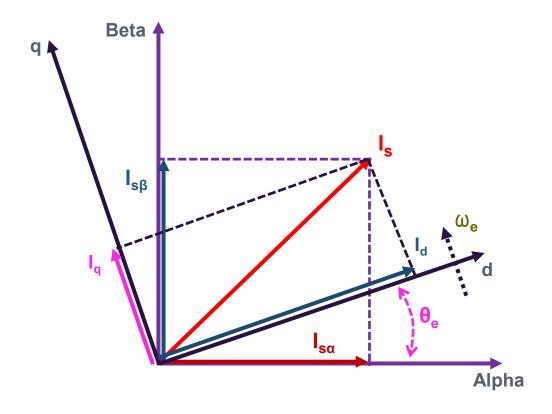

# PMSM – FOC Transformations from Stationary to Rotating Frame

### FOC - 3 Phase (ABC) PMSM Model

Assumptions: sinusoidal 3-phase distributed winding and neglecting effect of magnetic saturation and

leakage inductances

Stator voltage equátions

$$\begin{bmatrix} u_A \\ u_B \\ u_C \end{bmatrix} = R \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} + \begin{pmatrix} d \\ \psi_B \\ \psi_C \end{bmatrix}$$

Clarke Transformation 3 phase -> 2 phase

Time variation – how to get rid of it

Stator linkage flux

$$\begin{bmatrix} \psi_A \\ \psi_B \\ \psi_C \end{bmatrix} = \begin{bmatrix} L_{aa} & L_{ab} & L_{ac} \\ L_{ba} & L_{bb} & L_{bc} \\ L_{ca} & L_{cb} & L_{cc} \end{bmatrix} \begin{bmatrix} i_A \\ i_B \\ i_C \end{bmatrix} + \psi_{PM} \begin{bmatrix} \cos(\theta_e) \\ \cos(\theta_e - \frac{2}{3}\pi) \\ \cos(\theta_e + \frac{2}{3}\pi) \end{bmatrix}$$

Internal motor torque

$$T_i = \frac{P_i}{\omega_m} = \frac{p_p}{\omega_e} (u_{iA}i_A + u_{iB}i_B + u_{iC}i_C)$$

$$T_i = p_p(-\Psi_{PM}i_A\sin(\theta_e) - \Psi_{PM}i_B\sin(\theta_e - \frac{2}{3}\pi) - \Psi_{PM}i_C\sin(\theta_e + \frac{2}{3}\pi))$$

### FOC – 2 Phase (αβ) PMSM Model

Motor equations are getting simpler but still contains time variations (AC – component)

Stator voltage equations

$$\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \frac{d}{dt} \begin{bmatrix} \psi_{\alpha} \\ \psi_{\beta} \end{bmatrix}$$

Park Transformation AC -> DC

Stator linkage flux

$$\begin{bmatrix} \Psi_{S\alpha} \\ \Psi_{S\beta} \end{bmatrix} = \begin{bmatrix} L_S & 0 \\ 0 & L_S \end{bmatrix} \cdot \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \Psi_{PM} \Big|_{i_{Sd}=0} \cdot \begin{bmatrix} \cos \theta_e \\ \sin \theta_e \end{bmatrix}$$

Internal motor torque

$$T_i = \frac{3}{2} \frac{p_p}{\omega_e} (u_{i\alpha} i_{\alpha} + u_{i\beta} i_{\beta}) = \frac{3}{2} p_p (\Psi_{\alpha} i_{\beta} - \Psi_{\beta} i_{\alpha})$$

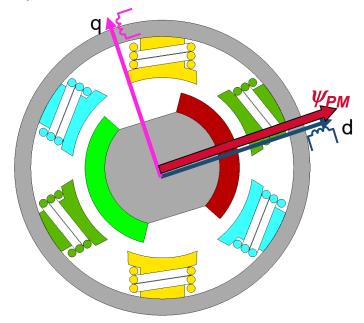

### FOC – (dq) Synchronous Frame PMSM Model

PMSM model in (dq) synchronous frame aligned with the rotor

All equations can now be resolved by simple linear algebra

#### Stator voltage equations

$$\begin{bmatrix} u_d \\ u_q \end{bmatrix} = R_s \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} s & \omega_e \\ -\omega_e & s \end{bmatrix} \begin{bmatrix} \psi_d \\ \psi_q \end{bmatrix}$$

#### Stator linkage flux

$$\begin{bmatrix} \psi_d \\ \psi_q \end{bmatrix} = \begin{bmatrix} L_d & 0 \\ 0 & L_q \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \psi_{PM} \begin{bmatrix} 1 \\ 0 \end{bmatrix}$$

#### Internal motor torque

$$T_{i} = \frac{3}{2} \frac{p_{p}}{\omega_{e}} (u_{id}i_{d} + u_{iq}i_{q}) = \frac{3}{2} p_{p} (\Psi_{d}i_{q} - \Psi_{q}i_{d}) = \frac{3}{2} p_{p} \cdot \Psi_{PM}i_{q}$$

### FOC – Transformations in Nutshell

(abc) stationary reference frame  $(\alpha\beta)$  stationary reference frame (dq) **rotating** reference frame 3 **DC** quantities (voltage/current/flux) 3 **AC** quantities (voltage/current/flux) 3 AC quantities (voltage/current/flux) 2 differential equations coupled 2 linear equations cross-coupled 3 differential equations coupled  $\psi_{PM}$  $\psi_{PM}$ Clarke Park linearize eq. simplify eq.  $\begin{bmatrix} u_{\alpha} \\ u_{\beta} \end{bmatrix} = R_s \begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} + \frac{d}{dt} \begin{bmatrix} \psi_{\alpha} \\ \psi_{\beta} \end{bmatrix}$  $\begin{vmatrix} u_d \\ u_q \end{vmatrix} = R_s \begin{vmatrix} i_d \\ i_q \end{vmatrix} + \begin{vmatrix} s & \omega_e \\ -\omega_e & s \end{vmatrix} \psi_d$

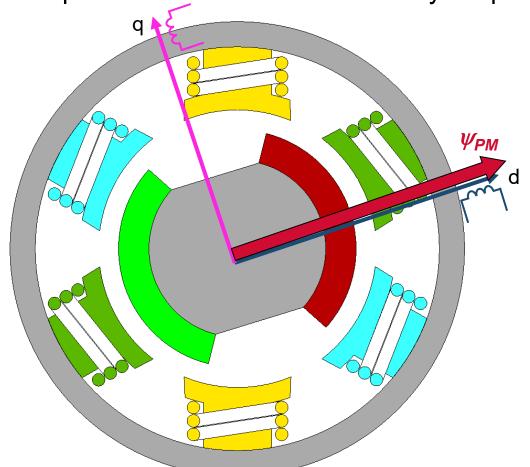

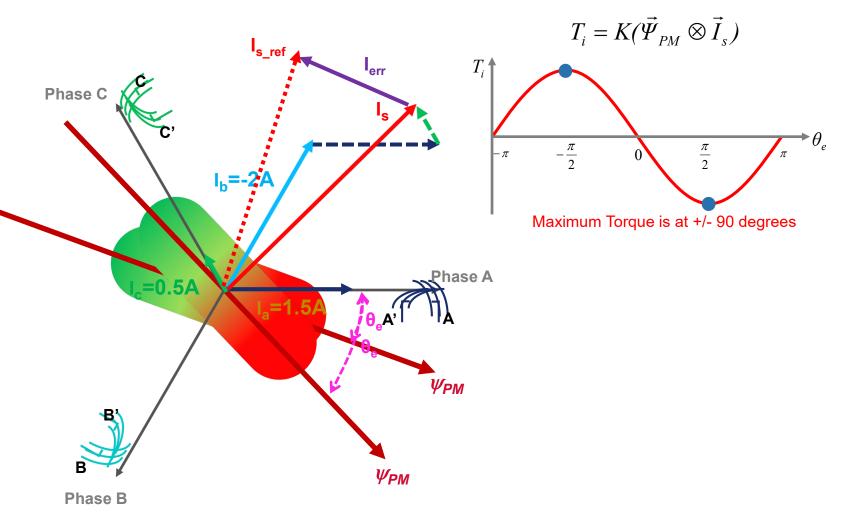

### PMSM – Why 90deg Between I<sub>s</sub> and Rotor Flux Vectors?

### PMSM – FOC Control Stages (Recap)

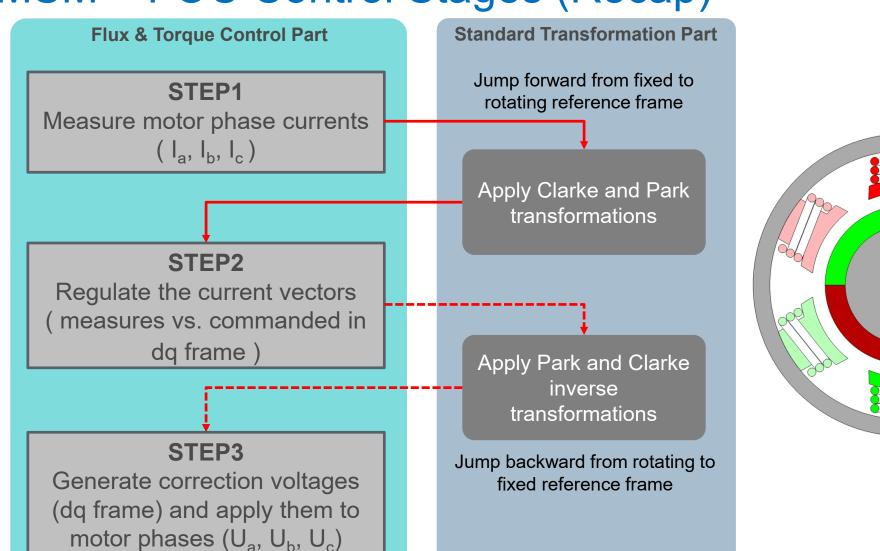

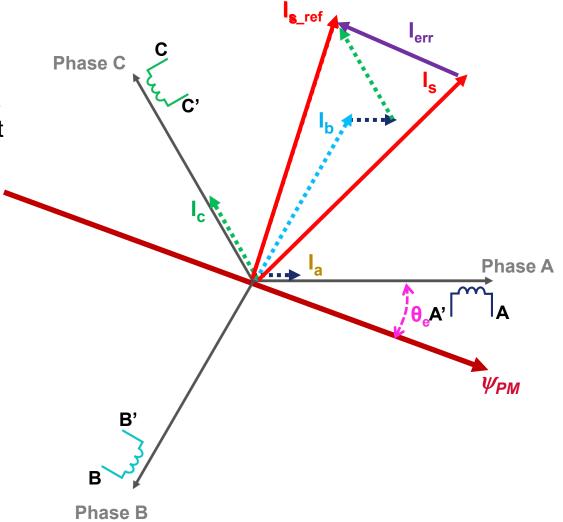

### Step 1: Motor Phase Current Measurement

### Step 2: Regulate Current Vector

Make sure I<sub>s</sub> is at 90 deg relative to rotor flux axis

Get the angle <sup>0</sup><sub>e</sub>

between rotor flux axis

and stator Phase A axis

Calculate the error between measured current vector  $I_s$  and the desired current vector  $I_{s\_ref}$  (  $I_{err} = I_{s\_ref} - I_s$  )

### **Step 3: Generate Corrections**

Compute the new appropriate I<sub>a</sub>, I<sub>b</sub> and I<sub>c</sub> that will minimize the I<sub>err</sub> forcing the stator current vector I<sub>s</sub> to align align with ideal I<sub>s\_ref</sub> stator reference vector

### FOC – From Theory to Action

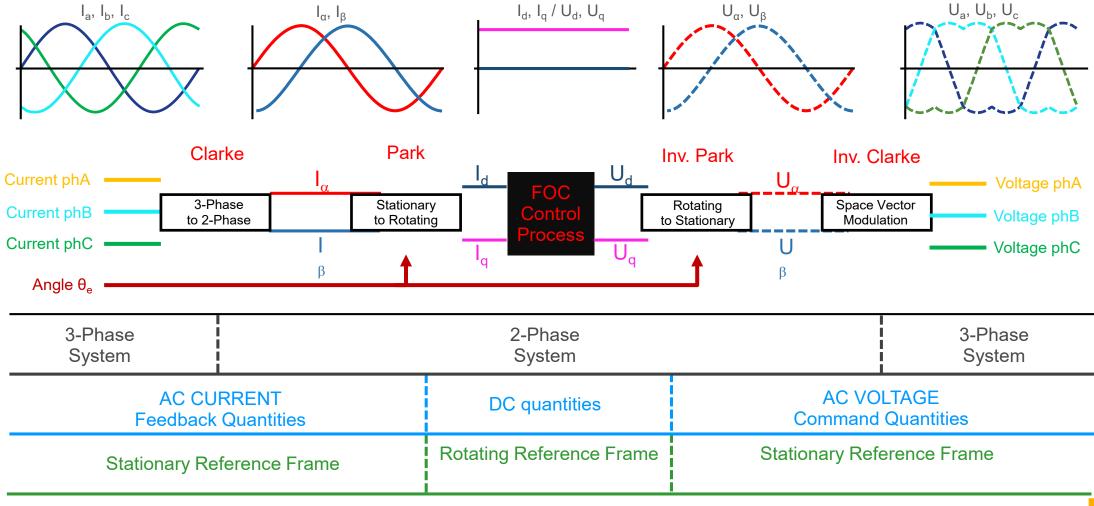

- The 3 control steps (Measure, Control and Correct) represent the "theory" behind Field Oriented Control;

- The "theory" is explained in static reference system (abc) which deals with time variant winding currents and voltages represented as vectors in previous diagrams;

- Even if the AC quantities control is doable in todays world of microprocessors, nobody use it since the limitations overcome the benefits. Designing a control system that tracks an time variant quantity pose big challenges in terms of controller frequency response and phase shift;

- Field Oriented Control solves this problem by controlling the current space vector directly in the dq reference frame of the rotor. Because the current space vector in the dq reference frame is static, the PI controllers operate on DC, rather than sinusoidal signals. Using Field Oriented Control, the quality of current control is largely unaffected by speed of rotation of the motor;

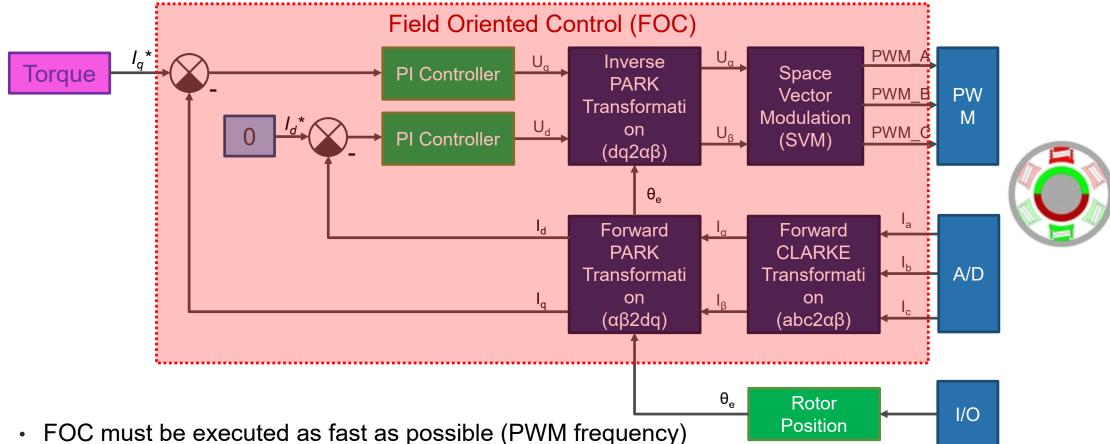

- To achieve that, the measured motor currents must be mathematically transformed from the three-phase static reference frame of the stator windings to the two axis rotating dq reference frame, prior to processing by the PI controllers. Similarly, the voltages to be applied to the motor are mathematically transformed from the dq frame of the rotor to the three-phase reference frame of the stator before they can be used for PWM output.

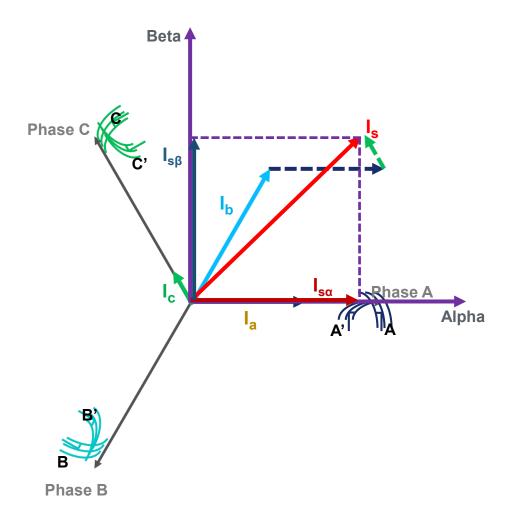

### FOC – Implementation (abc2αβ – Transformation)

3-phase Stationary to 2-phase Stationary (Forward Clarke Transform)

$$\begin{bmatrix} I_{s\alpha} \\ I_{s\beta} \end{bmatrix} = \begin{bmatrix} \frac{3}{2} & 0 & 0 \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} I_a \\ I_b \\ I_c \end{bmatrix}$$

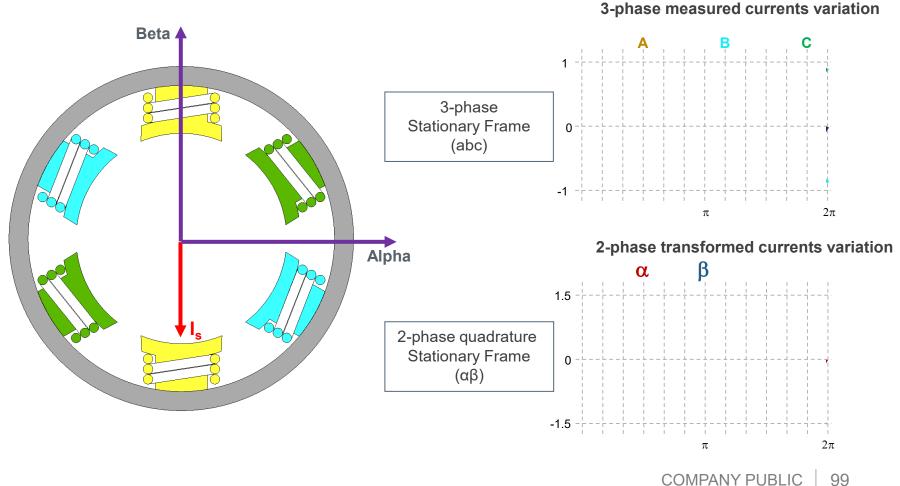

### FOC – Stationary Reference Frame Transformation

Measured currents variation before and after Forward Clarke Transformation

### FOC – Implementation (αβ2dq – Transformation)

2-phase Stationary to 2-phase Synchronous (Forward Park Transform)

$$\begin{bmatrix} I_d \\ I_q \end{bmatrix} = \begin{bmatrix} \cos(\theta_e) & \sin(\theta_e) \\ -\sin(\theta_e) & \cos(\theta_e) \end{bmatrix} \begin{bmatrix} I_{s\alpha} \\ I_{s\beta} \end{bmatrix}$$

### FOC – Synchronous Reference Frame Transformation

Measured currents variation before and after Forward Park Transformation

2-phase AC currents variation

### FOC – Quintessence

- In the dq rotating synchronous frame the space vector I<sub>s</sub> is described by a constant value of d and q components;

- The position and amplitude of the space vector I<sub>s</sub> can be fully controlled by two DC values.

- Control structure is simple since there are no AC values involved anymore.

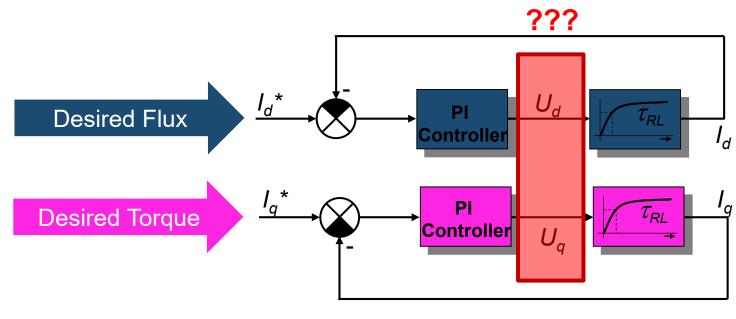

### FOC – Regulate PMSM Flux and Torque

#### Quick flashback from M2 module

Stator voltage equations

$$\begin{bmatrix} u_d \\ u_q \end{bmatrix} = R_s \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \begin{bmatrix} s & \omega_e \\ -\omega_e & s \end{bmatrix} \begin{bmatrix} \psi_d \\ \psi_q \end{bmatrix}$$

Stator linkage flux

$$\begin{bmatrix} \psi_d \\ \psi_q \end{bmatrix} = \begin{bmatrix} L_d & 0 \\ 0 & L_q \end{bmatrix} \begin{bmatrix} i_d \\ i_q \end{bmatrix} + \psi_{PM} \begin{bmatrix} 1 \\ 0 \end{bmatrix}$$

- I<sub>d</sub> and I<sub>q</sub> can be controlled independently in the rotating synchronous frame;

- In normal conditions when the stator flux vector is perpendicular to rotor flux vector then the I<sub>d</sub> reference is ZERO;

- l<sub>a</sub> controls the torque of the motor;

### FOC – Generate Correction Voltages

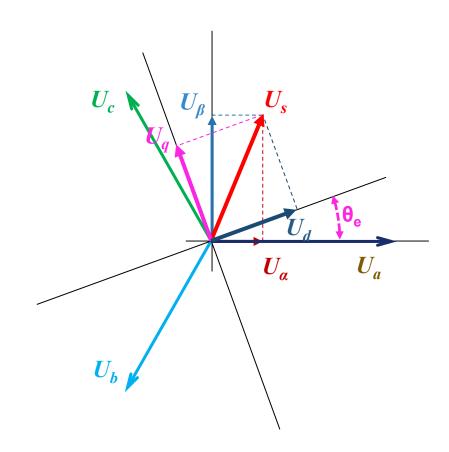

- U<sub>d</sub> and U<sub>a</sub> can not be applied directly to motor phases due to:

- 1. Exist only in the rotating reference frame (dq)

- 2. There are only 2 values and we need 3 to control a PMSM

2-phase Synchronous to 2-phase Stationary (Inverse Park Transform)

$$\begin{bmatrix} U_{\alpha} \\ U_{\beta} \end{bmatrix} = \begin{bmatrix} \cos(\theta_e) & -\sin(\theta_e) \\ \sin(\theta_e) & \cos(\theta_e) \end{bmatrix} \begin{bmatrix} U_d \\ U_q \end{bmatrix}$$

2-phase Stationary to 3-phase Stationary (Inverse Clarke Transform)

$$\begin{bmatrix} U_a \\ U_b \\ U_c \end{bmatrix} = \begin{bmatrix} \frac{2}{3} & 0 \\ -\frac{1}{3} & \frac{1}{\sqrt{3}} \\ -\frac{1}{3} & -\frac{1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} U_\alpha \\ U_\beta \end{bmatrix}$$

### FOC – Block Diagram

- FOC implements the current control loop a.k.a FAST LOOP

- · Any other loops (speed/position) that wraps over this inner loops will be referred as SLOW LOOP

### Application Mapping: SW vs. HW

# FOC – Block Diagram

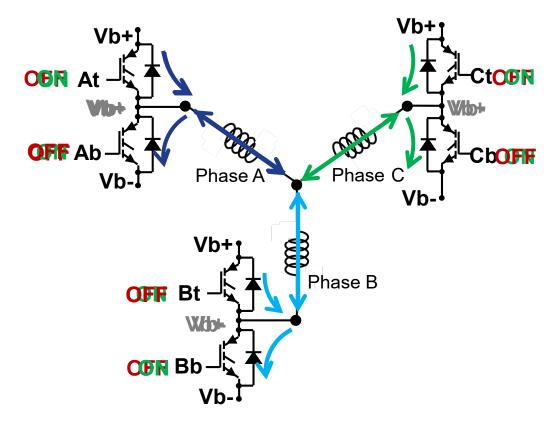

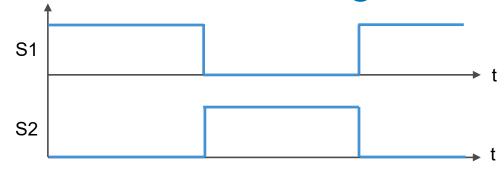

#### Commutation Used for PMSM

#### Commutation Used for PMSM (Cont'd)

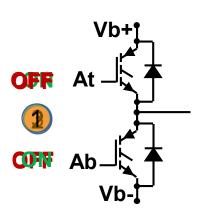

- All three inverter legs (6 transistors) are controlled at any time transistors are either switched ON or OFF

- PWM pairs are set to complementary mode:

- Top transistor ON

- Bottom transistor OFF

- Or vice versa

- Deadtime is inserted to protect inverter against short circuit

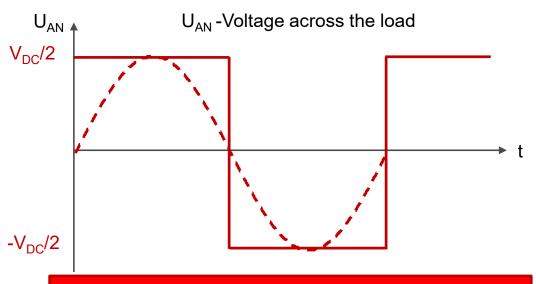

#### How to Generate a Sinusoidal Waveform Using PWM

The Sine-Wave amplitude is ONLY half of the  $V_{DC}$ . The is a better way!

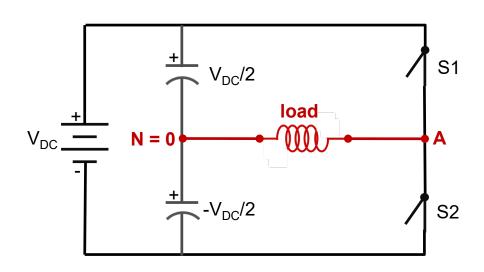

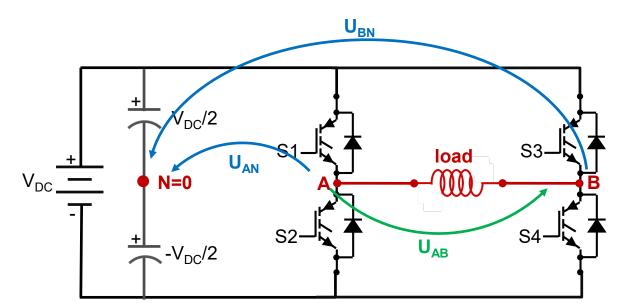

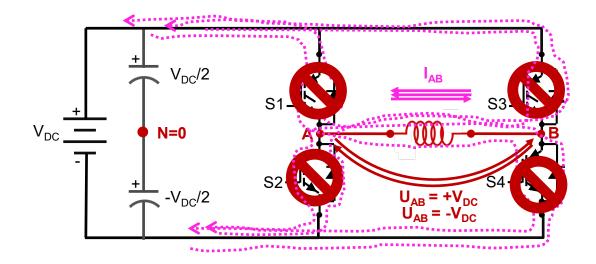

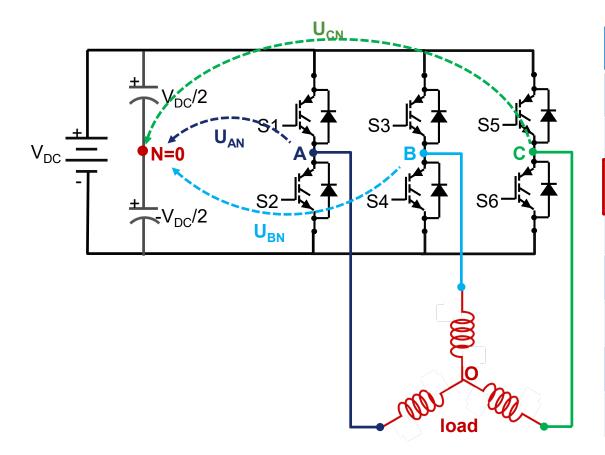

#### Single-Phase Inverter

- Has 2 legs that allows 4 main combinations for the top switches

- Allows full V<sub>DC</sub> voltage to be applied on the load

| S1  | S3  | U <sub>AN</sub>     | U <sub>BN</sub>     | U <sub>AB</sub>  |

|-----|-----|---------------------|---------------------|------------------|

| OFF | OFF | -V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | 0                |

| OFF | ON  | -V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | -V <sub>DC</sub> |

| ON  | OFF | +V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | +V <sub>DC</sub> |

| ON  | ON  | +V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | 0                |

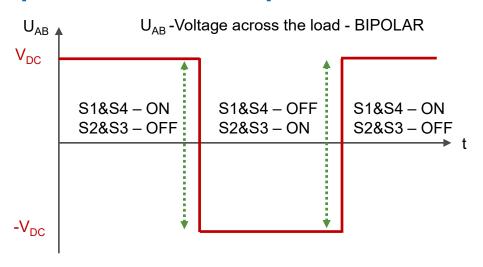

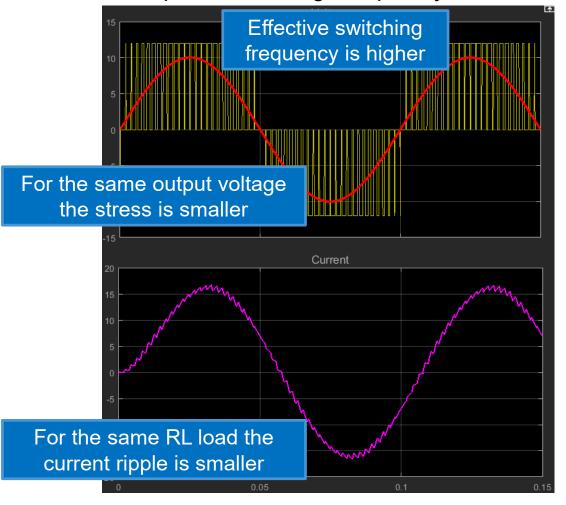

- BIPOLAR Modulation -> Load Voltage changes between -V<sub>DC</sub> and +V<sub>DC</sub>

- UNIPOLAR Modulation -> Load Voltage changes between 0 and  $+V_{DC}$  or between 0 and  $-V_{DC}$

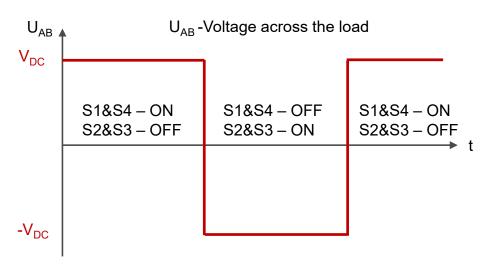

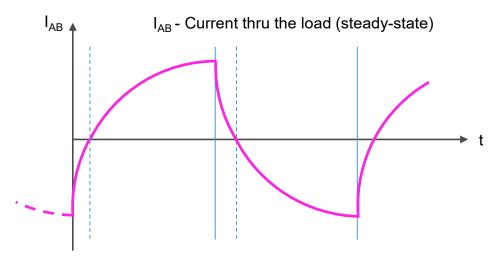

#### Single-Phase Inverter – Bipolar PWM Modulation

Increasing switching frequency and applying PWM make possible to control the  $U_{AB}$  rms and frequency of output voltage

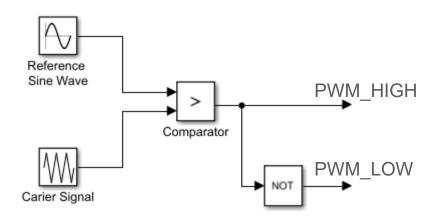

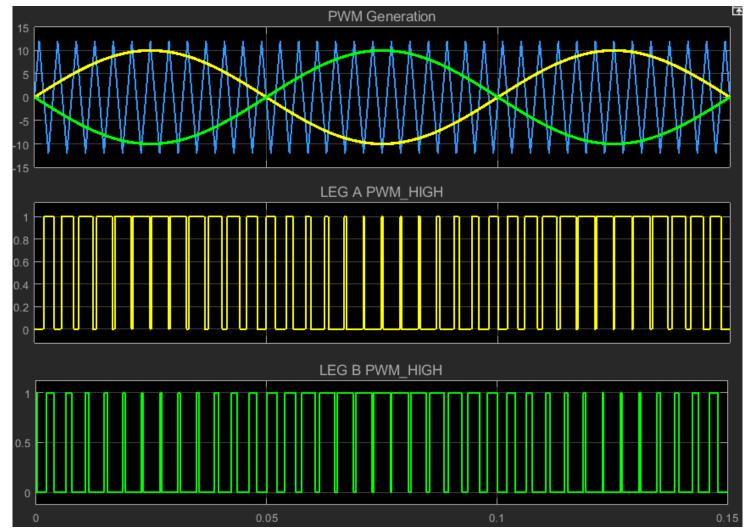

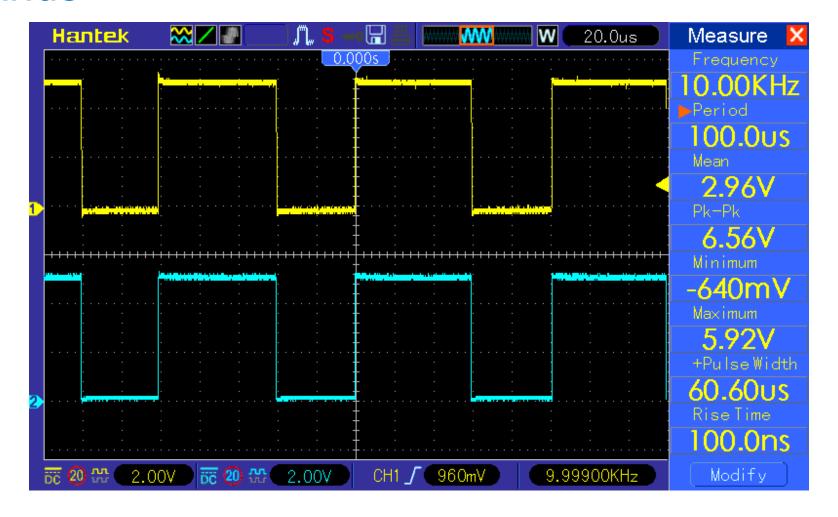

## Bipolar PWM Modulation for Single-Phase Use Case

- Simple logic to generate the PWM commands for transistor's gate

- 1kHz carrier sawtooth controls the switching frequency

- 10Hz@10V reference sine-wave

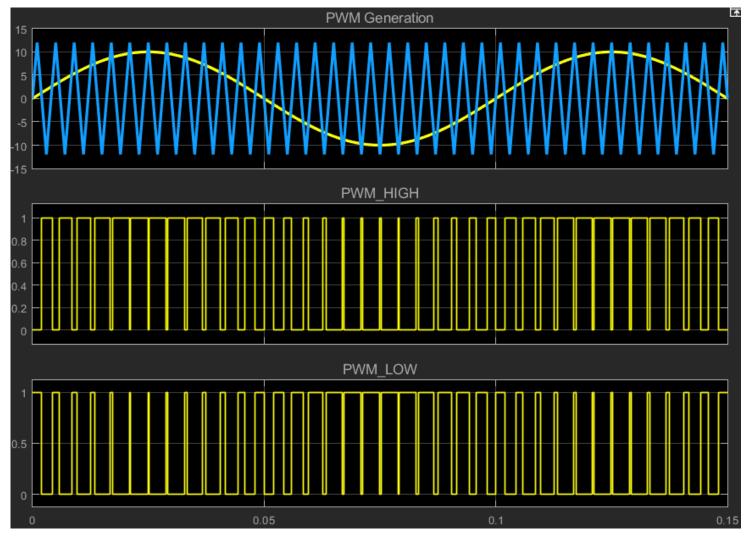

# Bipolar PWM Modulation – Effect of Switching Frequency

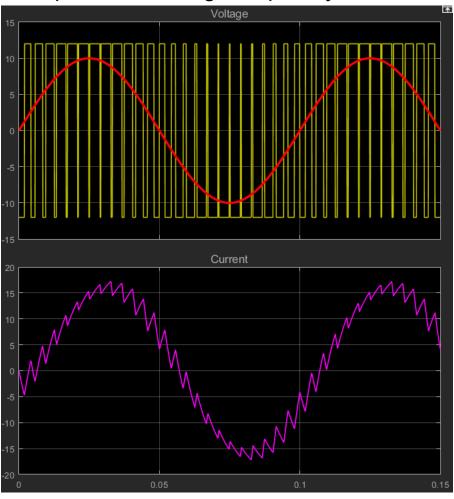

#### Bipolar vs. Unipolar PWM Modulation

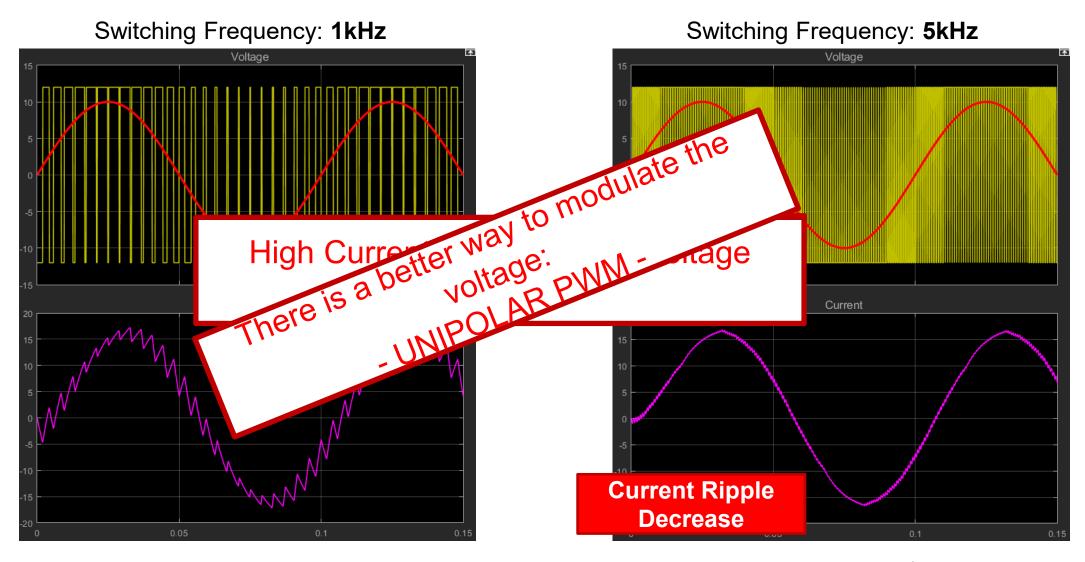

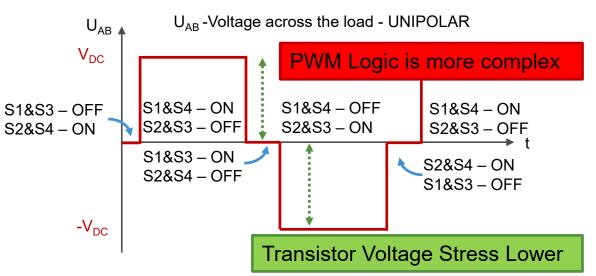

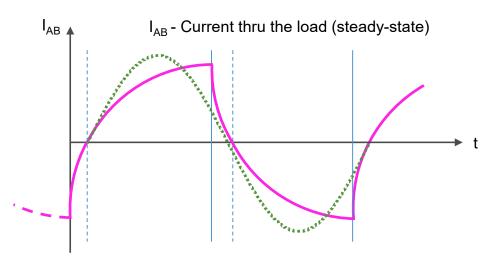

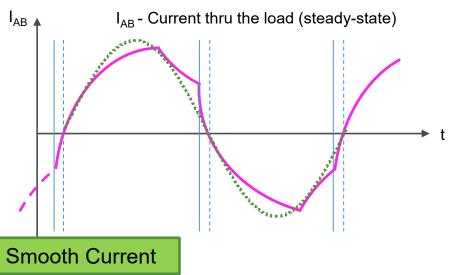

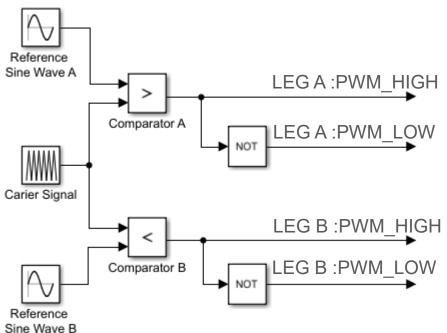

### Unipolar PWM Modulation for Single-Phase Use Case

- Simple logic to generate the PWM commands for transistor's gate

- 1kHz carrier sawtooth controls the switching frequency

- 2x10Hz@10V reference sine-waves phased out 180deg

#### Bipolar vs. Unipolar PWM Modulation

#### Unipolar Switching Frequency: 1kHz

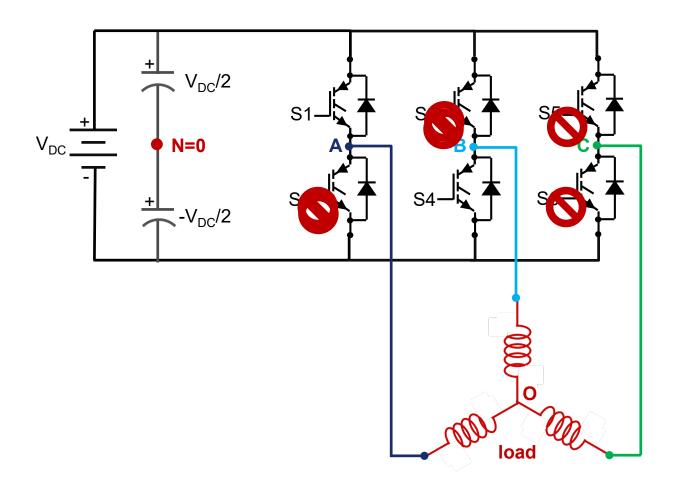

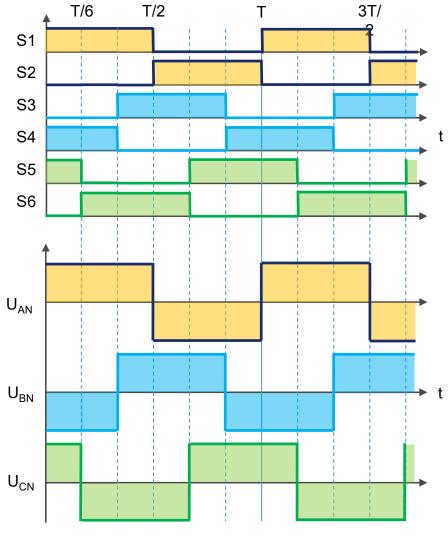

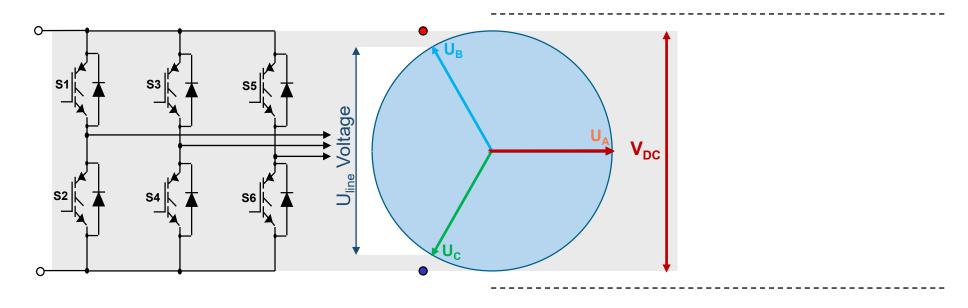

#### 3-Phase Inverter

- Has 3 legs that allows 8 main switching combinations for the top switches/transistors

- PWM pairs are set to complementary mode: S1/S2, S3/S4 and S5/S6

| S1  | S3  | <b>S</b> 5 | U <sub>AN</sub>     | U <sub>BN</sub>     | U <sub>CN</sub>     |

|-----|-----|------------|---------------------|---------------------|---------------------|

| OFF | OFF | OFF        | -V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 |

| OFF | OFF | ON         | -V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 |

| OFF | ON  | OFF        | -V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 |

| OFF | ON  | ON         | -V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 |

| ON  | OFF | OFF        | +V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 |

| ON  | OFF | ON         | +V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 |

| ON  | ON  | OFF        | +V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | -V <sub>DC</sub> /2 |

| ON  | ON  | ON         | +V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 | +V <sub>DC</sub> /2 |

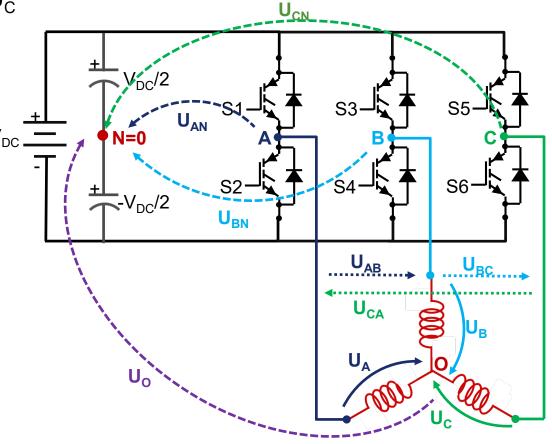

# 3-Phase Inverter – Terminal Voltages

• Terminal Voltage varies between  $-V_{DC}/2$  and  $+V_{DC}/2$  6ase 100: \$1=0N, \$3=0FF, \$5=0NF

**Gate Commands**

#### Terminal – Phase – Line – Common Voltages

- Phase Voltage motor winding voltage U<sub>A</sub>, U<sub>B</sub> and U<sub>C</sub>

- Common Mode Voltage PMSM neutral U<sub>O</sub>

- Terminal Voltage U<sub>AN</sub>, U<sub>BN</sub> and U<sub>CN</sub>

$$U_{AN} = U_A + U_0$$

$$U_{BN} = U_B + U_0$$

$$U_{CN} = U_C + U_0$$

How to compute the Common Mode Voltage?

$$U_{AN} + U_{BN} + U_{CN} \neq (U_A + U_B + U_C) + 3*U_0$$

$$U_0 = (U_{AN} + U_{BN} + U_{CN})/3$$

Line Voltage – U<sub>AB</sub>, U<sub>BC</sub> and U<sub>CA</sub>

$$U_{AB} = U_A - U_B$$

$$U_{BC} = U_B - U_C$$

$$U_{CA} = U_C - U_A$$

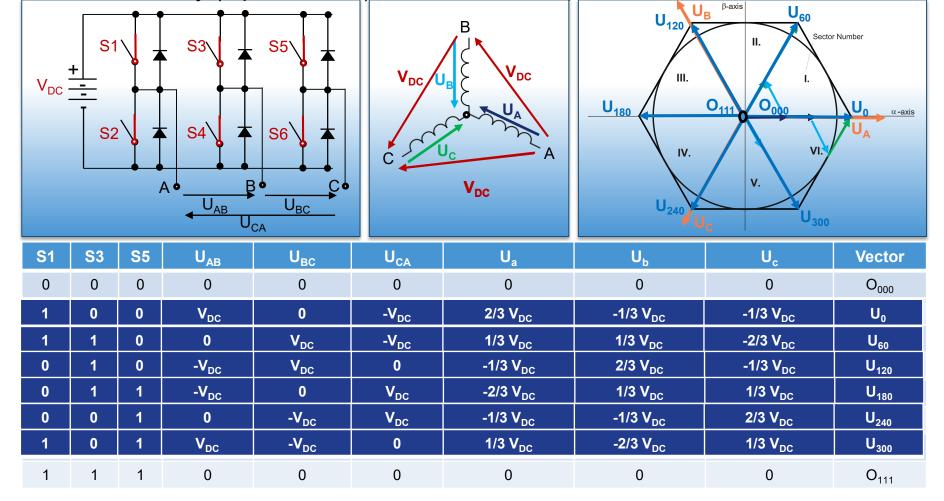

#### **Space Vector Modulation**

A 3-phase inverter can be configured to produce 8 distinct output states (2 null and 6 active)

Each output state produces an unique set of phase voltages that corresponds to a Voltage Space Vector

defined in the stationary (3 phase ABC) or (2 phase orthogonal αβ) reference frames

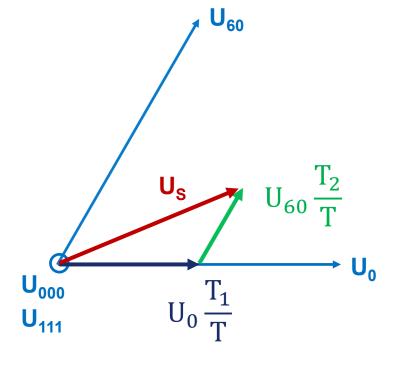

#### "The Essence" of Space Vector Modulation

- SVM allows creation of any reference voltage vector using a only 2 adjacent vectors and one convenient selected zero vector (000) or (111) to minimize the transistor commutations

- If T is the sampling period (aka PWM period) then:

- U<sub>0</sub> is applied for T<sub>1</sub>

- U<sub>60</sub> is applied for T<sub>2</sub>

- The zero vector is applied for the rest of the period so that the final voltage vector is obtained.

$$\mathsf{T}_0 = \mathsf{T} - \mathsf{T}_1 - \mathsf{T}_2$$

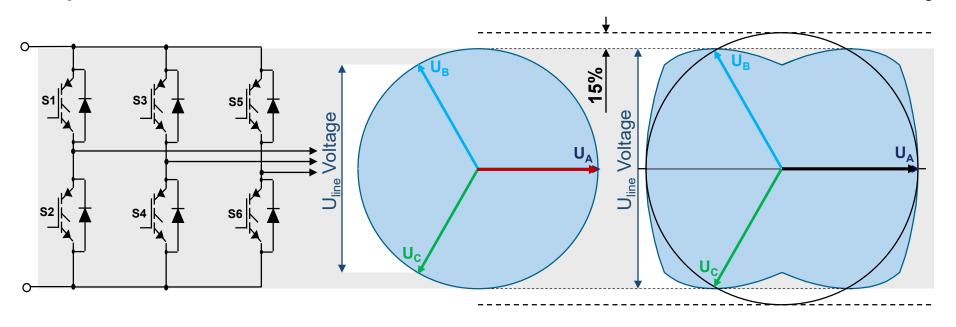

#### Sinusoidal Modulation Limitation

- Phase Voltage (U<sub>A</sub>, U<sub>B</sub> and U<sub>C</sub>) amplitude is limited to half of the DC-bus voltage

- The Line Voltage ( $U_{AB}$ ,  $U_{BC}$  and  $U_{CA}$ ) is lower then the  $V_{DC}$  voltage (although such voltage can be generated between the terminals)

How should we control the inverter switches to generate full line voltage?

#### Full Line Voltage Generation

- Full phase-to-phase voltage can be generated by continuously shifting the

- 3-phase voltage system

- The amplitude of the first harmonic can be then increased by 15.5%

# 3<sup>rd</sup> Harmonic Injection

- Line voltage is increased by adding the "shifting" voltage U<sub>0</sub>

- "Shifting" voltage U<sub>0</sub> must be the same for all three phases, thus it can only contain 3<sup>rd</sup> harmonics!

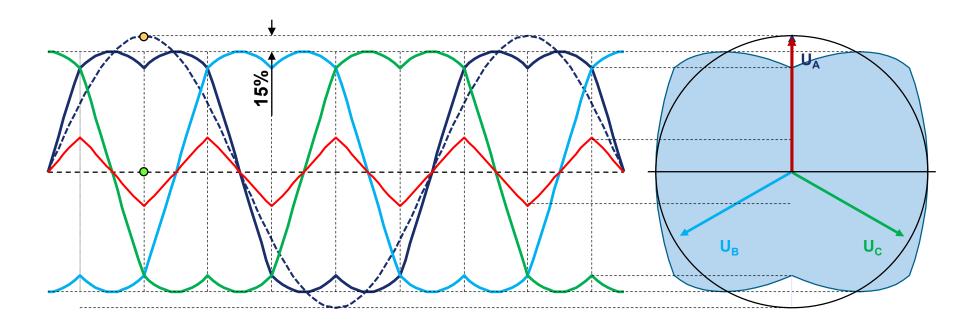

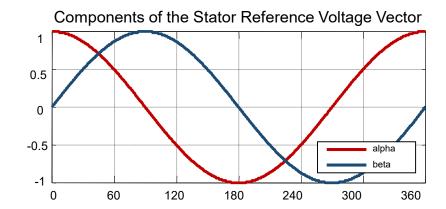

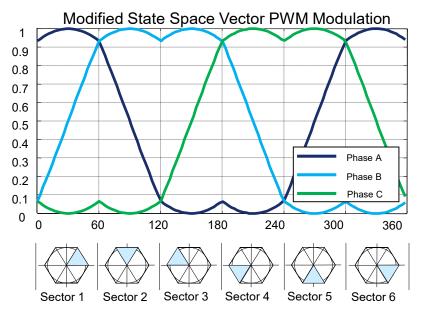

### Modified Space Vector Modulation Output Waveforms

- Output voltage vector is created by switching continuously between the adjacent base vectors and the "NULL" vectors so that the vectorial timeaverage of the asserted base space vectors is equal to the commanded voltage:

- Time spent in zero vectors is divided equally between (0,0,0) and (1,1,1);

- Switching waveforms should be symmetric, utilizing center-aligned PWM;

- Generates maximum phase voltage 0.57V<sub>DC</sub> instead of just 0.5V<sub>DC</sub>;

- Both nulls O000 and O111 are generated at each cycle

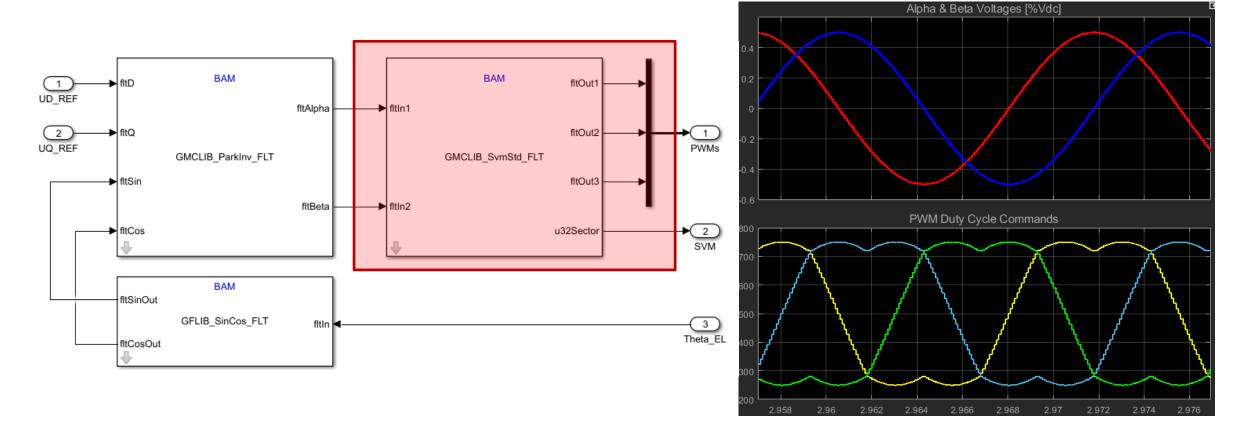

### Space Vector Modulation – Implementation

AMMCLIB provides a specialized block that computes the PWM duty cycles using modified space vector modulation.

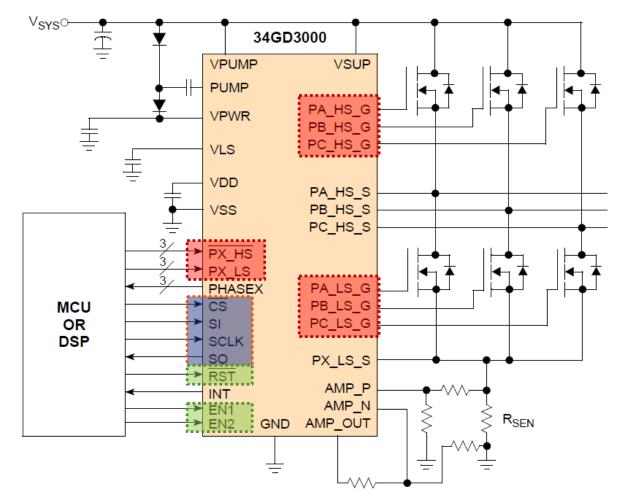

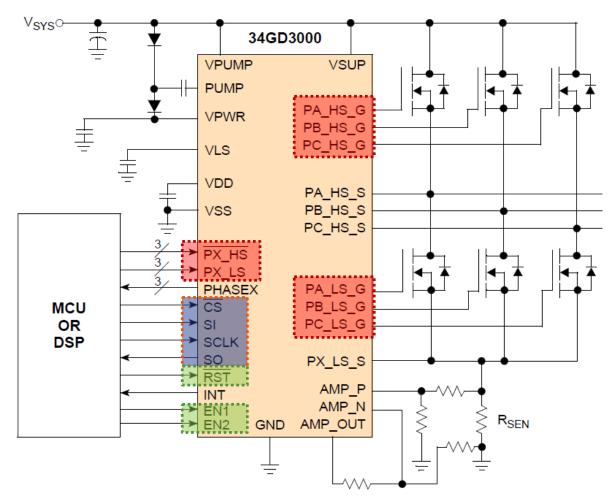

## MotorGD DevKit – Peripherals Used for Power Stage

| PORT J1         | PIN   | Function                                |  |

|-----------------|-------|-----------------------------------------|--|

| PWMC_LS/PS_LS   | J1-15 | Low switch phase C PWM command          |  |

| PWMC_HS_B/PC_HS | J1-13 | High switch phase C PWM command         |  |

| PWMB_LS/PB_LS   | J1-11 | Low switch phase B PWM command          |  |

| PWMB_HS_B/PB_HS | J1-09 | High switch phase B PWM command         |  |

| PWMA_LS/PA_LS   | J1-07 | Low switch phase A PWM command          |  |

| PWMA_HS_B/PA_HS | J1-05 | High switch phase A PWM command         |  |

| GD_RST_B/RST    | J1-03 | FET pre-driver reset pin                |  |

| GD_EN/EN1,EN2   | J1-01 | Enable FET pre-driver gate drive output |  |

Pre-driver MC34GD3000

### MC34GD3000 FET Pre-driver Configuration Sequence

#### A valid initialization sequence is:

- 1. RST goes high (EN1 and EN2 remain low)

- 2. 5. EN1 and EN2 are set high

- 6. PA\_LS\_G, PB\_LS\_G, and PC\_LS\_G are toggled high for about 1.0 µs (HS outputs are enabled, but not latched)

- 7. Toggle PA\_HS\_G, PB\_HS\_G, and PC\_HS\_G Low for deadtime plus at least 0.1 µs

Note: PX\_HS signal are inverted – active low

Source: MC34GD3000 datasheet Rev. 3.0, 5/2016

# PWM Generation: Top MOSFET vs. Bottom MOSFET Gate Commands

#### Application Mapping: SW vs. HW

#### **Current Sensing Methods**

- Motor drive systems need to measure current accurately for:

- Control Feedback;

- Protection for overcurrent, short-circuit, i2t, etc;

- Information about power consumption levels;

- There are 4 major methods to measure the current with the advantages and disadvantages of each

| Current Sense Method | Advantages                                   | Disadvantages                            |

|----------------------|----------------------------------------------|------------------------------------------|

| Shunt resistor       | Low cost, accuracy and wideband              | High power dissipation                   |

| Conductor            | No-cost, PCB tracks, reduce BOM              | Poor accuracy due temperature variations |

| Hall effect          | Galvanic isolation, low power dissipation    | High cost, limited bandwidth             |

| Transformer          | Isolation, high current sensing capabilities | Large size & mass, AC only               |

In general due to low cost and good accuracy, the shunt resistors are frequently the best answer for most

of the applications

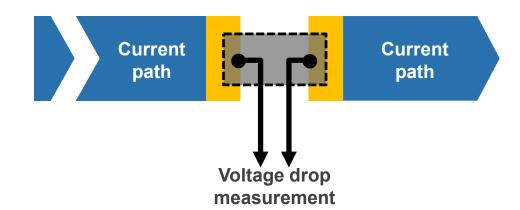

#### **Shunt Resistor Method**

Current is proportional with the voltage drop across the resistor: I = V/R

Parasitic inductance due to inductance components

To reduce/eliminate the parasitic inductances special resistors and PCB designs are used

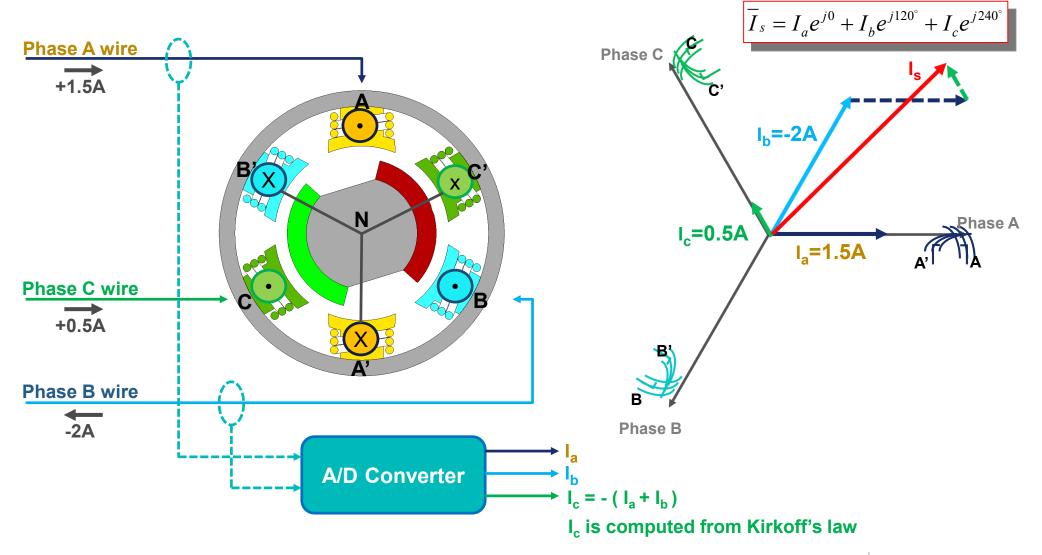

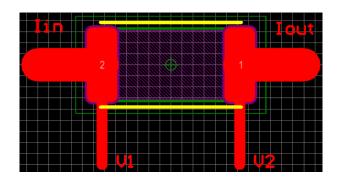

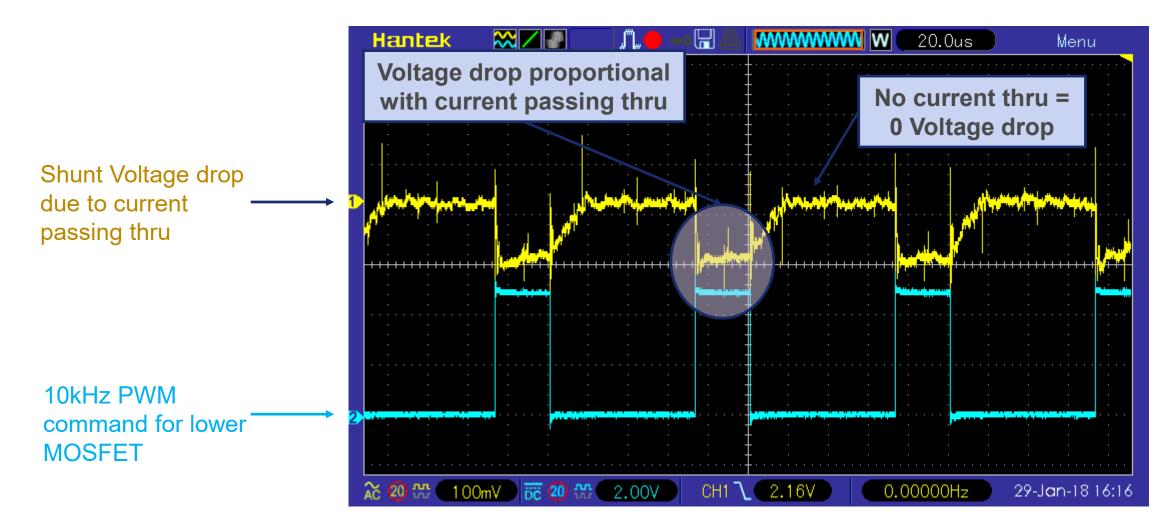

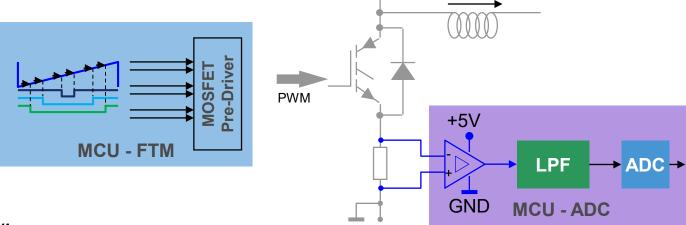

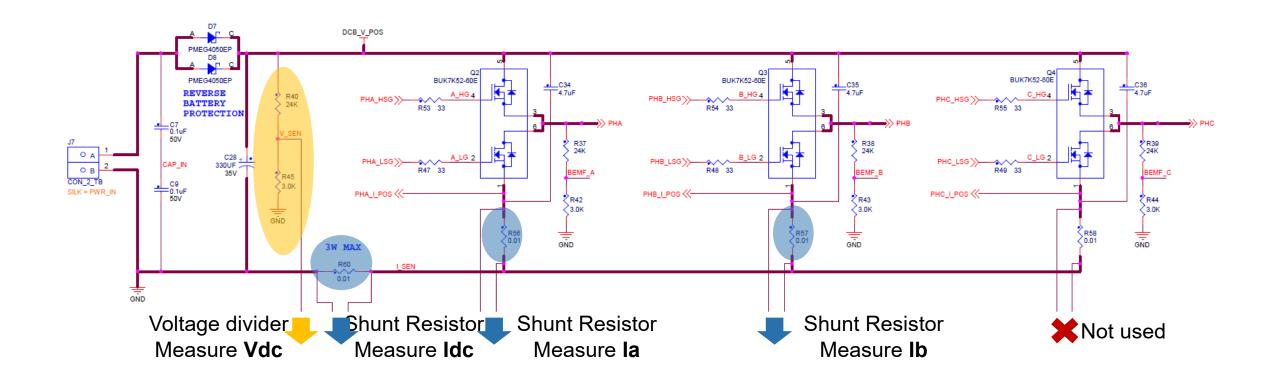

#### Motor Control: Dual Shunt Current Sensing

- For isolated 3 phase symmetric systems only two phase currents are needed to be sampled by the ADC, the third current being determined from Kirchhoff circuit law

- Measurements can be done only when the current flows thru lower switch

- ADC dual-sampling is required to read currents in the same moment

- As general rule: a positive current is defined as the current that flows into the motor winding while the negative current is defined a the one that flows out of the motor winding.

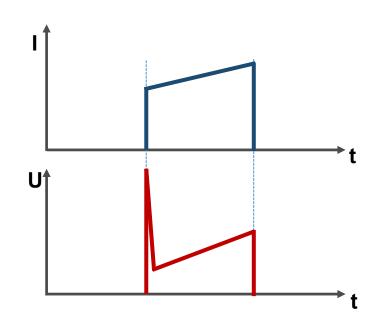

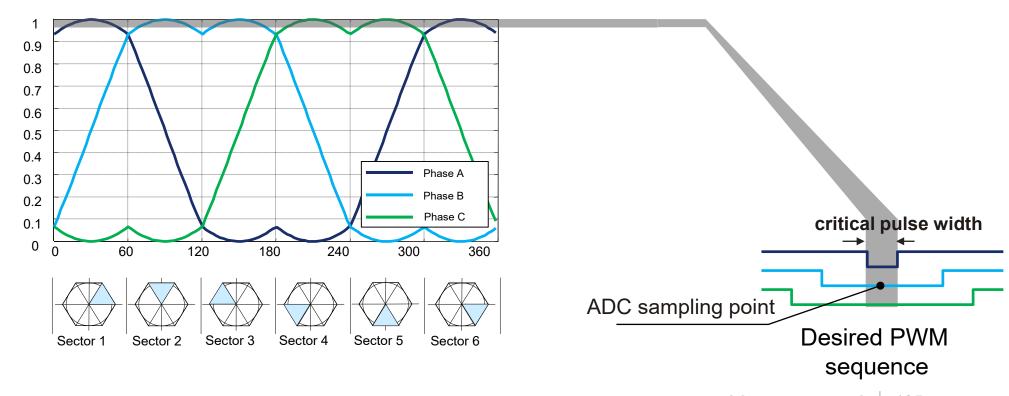

#### Motor Control: Current Sensing Considerations

- Bottom transistor must be switched on at least for a critical pulse width to get stabilized current shunt resistor voltage drop

- At any time, this rule needs to be accomplished for the legs where the shunts are located.

- Minimum pulse width defined by system delays and ADC sampling time

#### Voltage Drop Across the Shunt Resistor

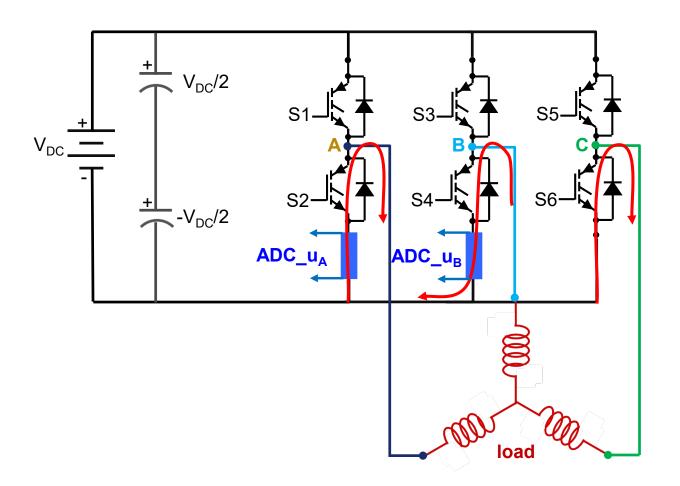

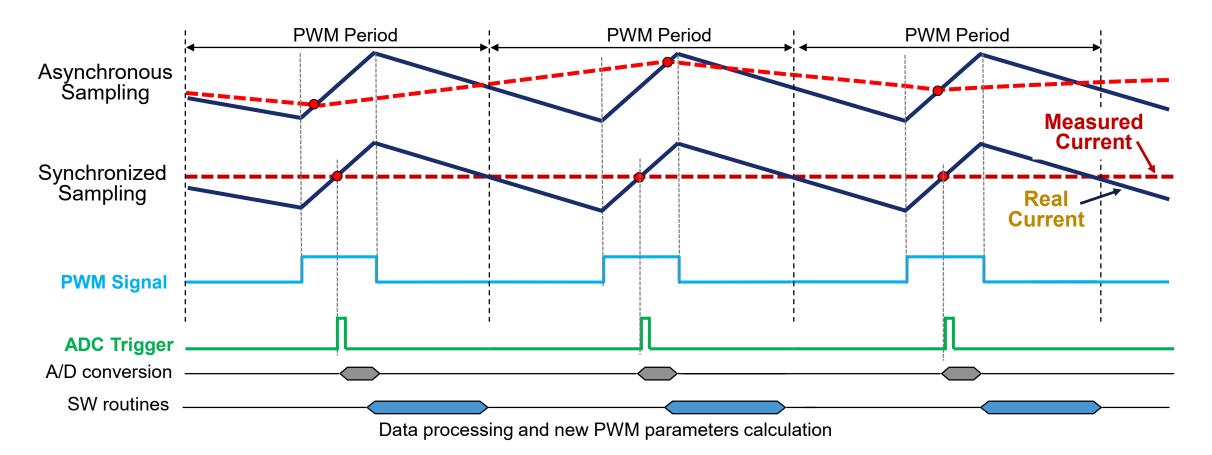

#### PWM – ADC Synchronization

• Enforce ADC sampling at regular time intervals & helps to filter the measured current - antialiasing

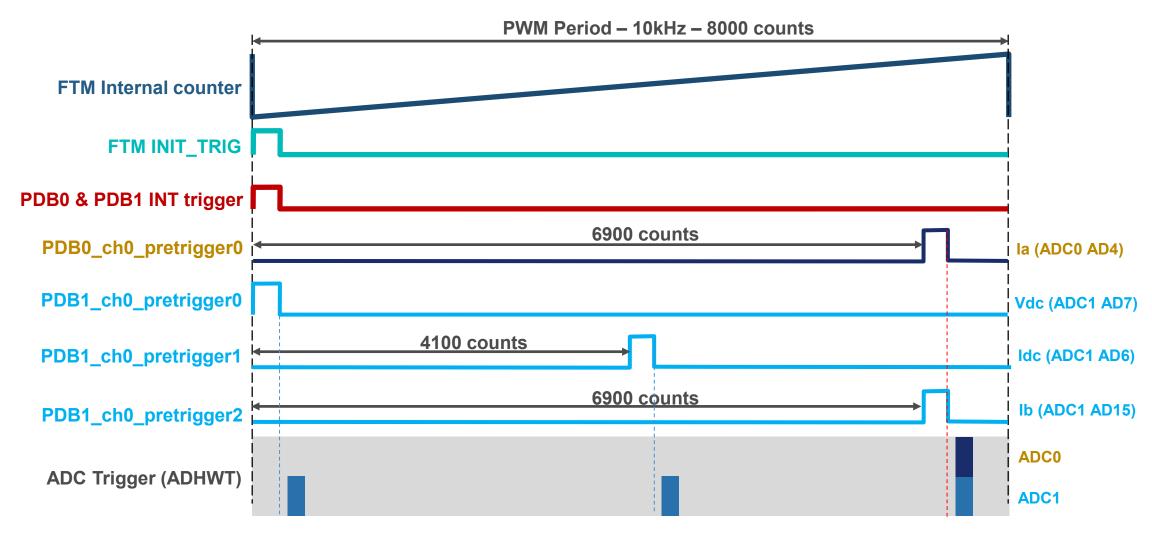

#### PWM – ADC Synchronization (Cont'd)

- On S32K MCU the synchronization can be done via Programable Delay Block (PDB).

- The FlexTimer trigger outputs are used as trigger source for PDB that in turns triggers the ADC

- Same FTM trigger is used to start both ADC instances

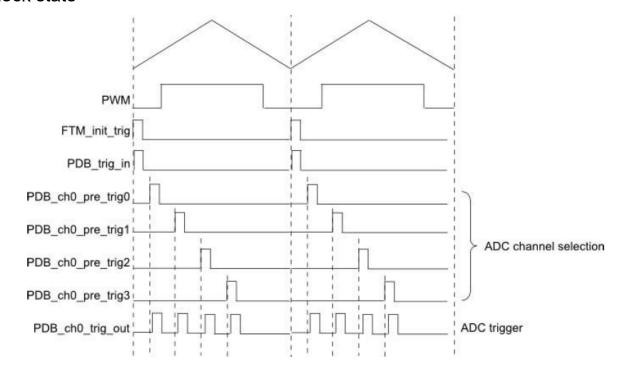

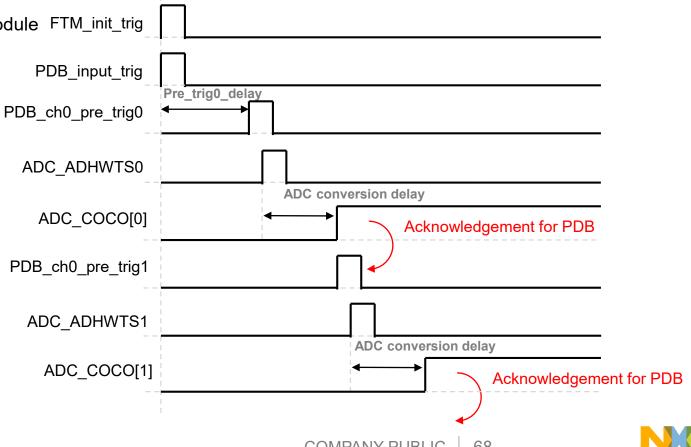

#### **ADC Trigger Concept**

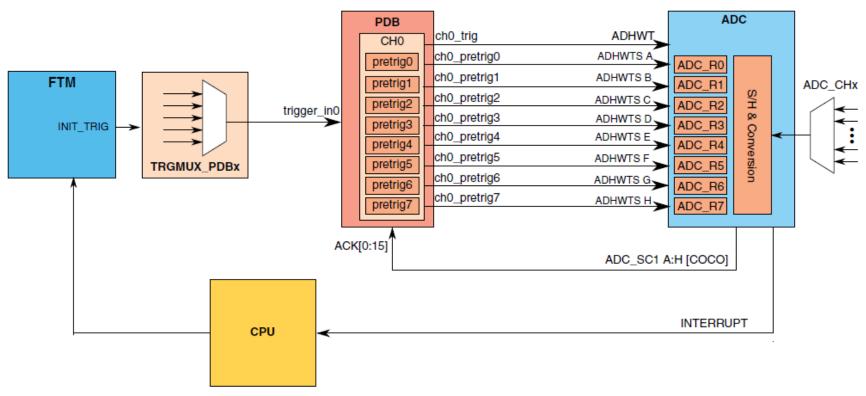

- The FTM supports the counter INIT\_TRIG which will be used as a trigger input of the PDB. The PDB then

triggers the ADC.

- Each ADC channel in the PDB module supports up to 8 pre-triggers used as the ADC hardware channel selection. After a pre-trigger, the ADC trigger initiates the ADC conversion.

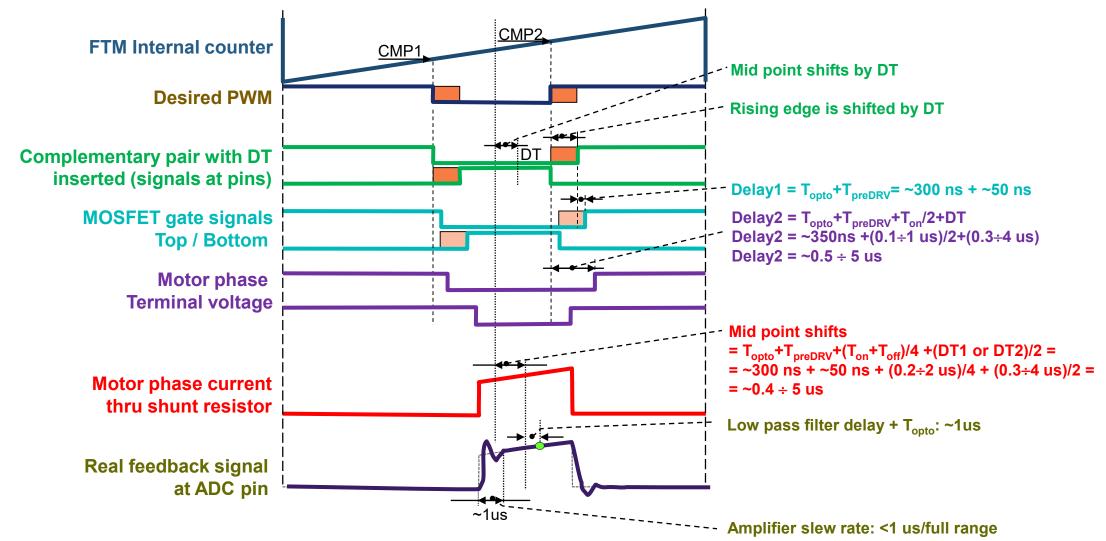

Delays Involved in PWM – ADC Synchronization

Current sensing processing chain

Delays are chained and are caused by:

| Delay Type                          | Delay impact | Time          |

|-------------------------------------|--------------|---------------|

| PWM Dead time insertion             |              | 100ns - 1/2us |

| Opto-coupler propagation delay      |              | 40ns - 300ns  |

| MOSFET pre-driver propagation delay |              | ~50ns         |

| MOSFET turn ON/OFF times            |              | 100ns – 1us   |

| Amplifier slew rate                 |              | <1us          |

| Low-pass filter (LPF) delay         |              | 1-2us         |

| ADC delays                          |              | 50ns-200ns    |

# Delays Involved in PWM – ADC Synchronization (Cont'd)

#### PWM-PDB-ADC Synchronization

#### MotorGD DevKit: Inverter Schematic

# MotorGD DevKit: Inverter Schematic (Cont'd)

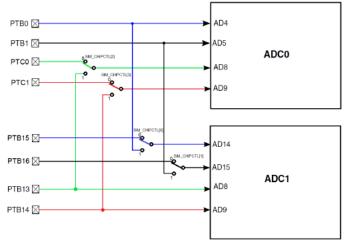

#### MotorGD DevKit: Pins Used for ADC Measurements

# S32K144 MCU Signal Assignment

## S32K144 MCU Signal Assignment (Cont'd)

ADC default pin assignment for sensing currents: can't synchronize the phase current sensing

| MotorGD DevKit  | MCU pin | ADC instance |  |

|-----------------|---------|--------------|--|

| Phase A current | PTB0    | ADC0/SE4     |  |

| Phase B current | PTB1    | ADC0/SE5     |  |

| DC bus voltage  | PTB12   | ADC1/SE7     |  |

| DC bus current  | PTD4    | ADC1/SE6     |  |

| ADC HW<br>Interleave |

|----------------------|

| ADC0/SE4             |

| ADC1/SE16            |

| ADC1/SE7             |

| ADC1/SE6             |

Solution is ADC Hardware Interleaved Channels

In the hardware interleaved mode, a signal on the pin PTB1 can be sampled

by both ADC0 and ADC1 in the same time. The interleaved mode is enabled

by SIM CHIPCTL[ADC INTERLEAVE EN] bits.

## MC34GD3000 FET Pre-driver Configuration Sequence

#### A valid initialization sequence is:

- 1. RST goes high (EN1 and EN2 remain low)

- 2. EN1 and EN2 are set high

- 3. PA\_LS\_G, PB\_LS\_G, and PC\_LS\_G are toggled high for about 1.0 µs (HS outputs are enabled, but not latched)

- 4. Toggle PA\_HS\_G, PB\_HS\_G, and PC\_HS\_G Low for deadtime plus at least 0.1 μs

Note: PX\_HS signal are inverted – active low

Source: MC34GD3000 datasheet Rev. 3.0, 5/2016

#### Getting Help

#### **MBDT Online Community** Examples & Help

#### MBDT home page www.nxp.com/mbdt

# SECURE CONNECTIONS FOR A SMARTER WORLD