# **QorlQ LX2160A Reference Design Board Getting Started Guide**

## 1 Introduction

The QorIQ<sup>®</sup> LX2160A reference design board (RDB) provides a comprehensive platform that enables design and evaluation of the QorIQ LX2160A processor. The LX2160ARDB comes pre-loaded with a board support package (BSP) based on a standard Linux kernel.

The LX2160ARDB functions with an integrated development environment (IDE), such as CodeWarrior Development Studio. For instructions on how to work with the CodeWarrior Development Studio IDE, see CodeWarrior Development Studio for QorIQ LS series - ARM V8 ISA, Targeting Manual.

This document provides details of different board interfaces and explains how to set up and boot the board.

# 2 Related documentation

The table below lists and explains the additional documents and resources that you can refer to for more information on the LX2160ARDB.

Some of the documents listed below may be available only under a non-disclosure agreement (NDA). To request access to these documents, contact your local NXP field applications engineer (FAE) or sales representative.

## Contents

| Introduction                       | 1                                                                                                                                                                                                                                                                                        |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Related documentation              | 1                                                                                                                                                                                                                                                                                        |

| Hardware kit contents              | 2                                                                                                                                                                                                                                                                                        |

| Chassis and board pictures         | 3                                                                                                                                                                                                                                                                                        |

| Power and reset buttons            |                                                                                                                                                                                                                                                                                          |

| Connectors                         | 6                                                                                                                                                                                                                                                                                        |

| Jumpers                            | 8                                                                                                                                                                                                                                                                                        |

| LEDs                               | 9                                                                                                                                                                                                                                                                                        |

| DIP switches                       | 12                                                                                                                                                                                                                                                                                       |

| Getting started with LX2160ARDB    | 15                                                                                                                                                                                                                                                                                       |

| Ethernet port mapping              | 20                                                                                                                                                                                                                                                                                       |

| Flash image layout                 | 20                                                                                                                                                                                                                                                                                       |

| Upgrading BSP images in LX2160ARDB | 21                                                                                                                                                                                                                                                                                       |

| Troubleshooting                    | 22                                                                                                                                                                                                                                                                                       |

| Revision history                   |                                                                                                                                                                                                                                                                                          |

|                                    | Related documentation.  Hardware kit contents.  Chassis and board pictures.  Power and reset buttons.  Connectors.  Jumpers.  LEDs.  DIP switches.  Getting started with LX2160ARDB.  Ethernet port mapping.  Flash image layout.  Upgrading BSP images in LX2160ARDB.  Troubleshooting. |

## Hardware kit contents

Table 1. Related documentation

| Document                                                                                   | Description                                                                                                                                                                                                                                        | Link / how to access                                                                       |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| QorlQ LX2160A Reference<br>Design Board Reference<br>Manual                                | Provides detailed description of the LX2160ARDB                                                                                                                                                                                                    | QorlQ LX2160A Reference<br>Design Board Reference<br>Manual                                |

| QorlQ LX2160A Reference<br>Design Board Errata                                             | Describes known errata and workarounds for the LX2160ARDB                                                                                                                                                                                          | QorlQ LX2160A Reference<br>Design Board Errata                                             |

| QorlQ LX2160A Product<br>Brief                                                             | Provides a brief overview of the LX2160A processor                                                                                                                                                                                                 | QorlQ LX2160A Product<br>Brief                                                             |

| QorlQ LX2160A Data Sheet                                                                   | Provides information about electrical characteristics, hardware design considerations, and ordering information                                                                                                                                    | Contact FAE / sales representative                                                         |

| QorlQ LX2160A Family<br>Reference Manual                                                   | Provides a detailed description about the LX2160A QorlQ multicore processor and its features, such as memory map, serial interfaces, power supply, chip features, and clock information                                                            | Contact FAE / sales representative                                                         |

| QorlQ LX2160A Chip Errata                                                                  | Lists the details of all known silicon errata for the LX2160A                                                                                                                                                                                      | Contact FAE / sales representative                                                         |

| QorlQ LX2160A Design<br>Checklist, AN5407                                                  | This document provides recommendations for new designs based on the LX2160A. This document can also be used to debug newly designed systems by highlighting those aspects of a design that merit special attention during initial system start-up. | Contact FAE / sales representative                                                         |

| Layerscape LX2160A BSP                                                                     | This document explains how to use the QorlQ LX2160A BSP, which is a Linux-based development kit, to evaluate and explore the features of the LX2160A SoC.                                                                                          | Contact FAE / sales representative                                                         |

| CodeWarrior Development<br>Studio for QorlQ LS series -<br>ARM V8 ISA, Targeting<br>Manual | This manual explains how to use the CodeWarrior Development Studio for QorlQ LS series - ARM V8 ISA product.                                                                                                                                       | CodeWarrior Development<br>Studio for QorlQ LS series -<br>ARM V8 ISA, Targeting<br>Manual |

| CodeWarrior TAP Probe<br>User Guide                                                        | Provides details of CodeWarrior® TAP, which enables target system debugging through a standard debug port (usually JTAG) while connected to a developer workstation through Ethernet or USB                                                        | CodeWarrior TAP Probe<br>User Guide                                                        |

# 3 Hardware kit contents

The table below lists the items included in the LX2160ARDB hardware kit.

Table 2. Hardware kit contents

| Item description                                                        | Quantity |

|-------------------------------------------------------------------------|----------|

| LX2160ARDB hardware assembly with enclosure                             | 1        |

| 3-conductor power cord                                                  | 1        |

| DB9 shielded serial cable                                               | 1        |

| Cat-6 Ethernet cable, 1.8 meter                                         | 1        |

| Zip lock bag containing 1U chassis braket (2 pieces) + screw (8 pieces) | 1        |

| LX2160ARDB insert card                                                  | 1        |

QorlQ LX2160A Reference Design Board Getting Started Guide, Rev. 0, 09/2018

Apart from the main LX2160ARDB kit, two optional kits are also available for purchase at nxp.com:

- LX2RDBKIT1-10-40: Contains transceivers and cables recommended to be used for testing 10/40 Gigabit Ethernet performance on the LX2160ARDB

- LX2RDBKIT2-25G: Contains transceivers and cables recommended to be used for testing 25 Gigabit Ethernet performance on the LX2160ARDB

The table below describes the items included in the LX2RDBKIT1-10-40 kit.

Table 3. LX2RDBKIT1-10-40 kit contents

| Item description                                                                                                             | Manufacturer          | Manufacturing part number | For port/slot | Quantity |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|---------------|----------|

| Cat-6 Ethernet cable, 6 ft length, orange                                                                                    |                       | 10X8-03106                | 10G MAC3/4    | 2        |

| 40G-BASE-SR4 QSFP<br>+ optical transceiver<br>module, 40 Gbit/s multi-<br>mode, 850 nm<br>wavelength, 150 m<br>maximum reach | Mellanox Technologies | MC2210411-SR4             | 40G MAC2      | 1        |

| QSFP+ LAN optical<br>cable, multi-mode, OM3<br>50/125, MPO<br>connector, 3 m length                                          |                       | 12FMPOOM3 - 66239         | 40G MAC2      | 1        |

| Samsung 32 GB (U1)<br>EVO select micro-SD<br>card with adapter                                                               | Samsung               | MB-ME32GA/AM              | SD card       | 1        |

The table below describes the items included in the LX2RDBKIT2-25G kit.

Table 4. LX2RDBKIT2-25G kit contents

| Item description                                                                                                | Manufacturer          | Manufacturing part number          | For port/slot | Quantity |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|---------------|----------|

| SFP-25G-SR optical<br>transceiver module, 25<br>Gbit/s multi-mode, 850<br>nm wavelength, 100 m<br>maximum reach | Mellanox Technologies | MMA2P00-AS                         | 25G MAC5/6    | 1        |

| LAN optical cable,<br>multi-mode, OM3<br>50/125, LC duplex<br>connector, 3 m length                             |                       | OM3-LC-LC-DX-<br>FS-3M-PVC - 41728 | 25G MAC5/6    | 1        |

# 4 Chassis and board pictures

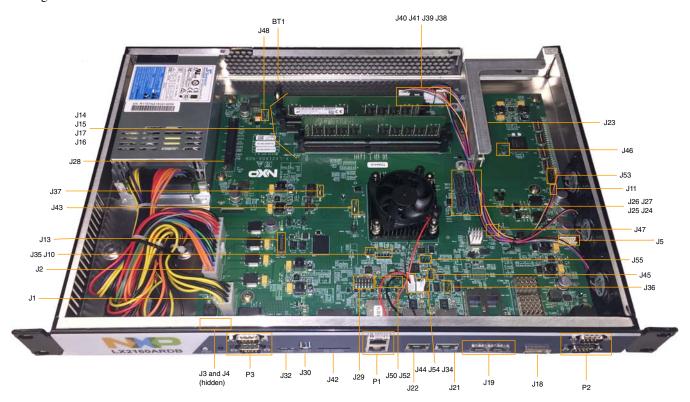

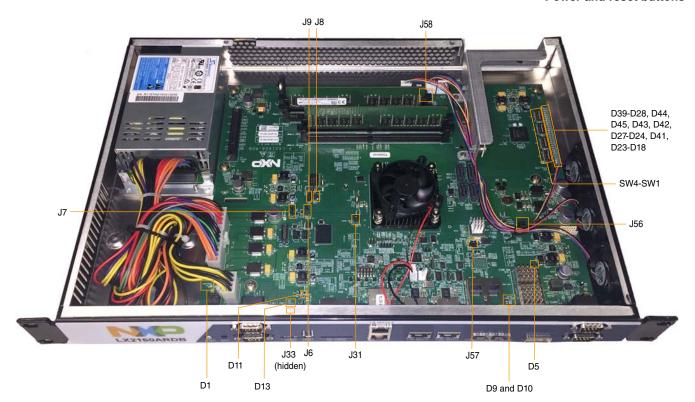

This section provides labelled images of the LX2160ARDB chassis and board for easy identification of different board components. The board components marked with labels are described in the subsequent sections.

The figure below shows the front side view of the LX2160ARDB chassis.

QorlQ LX2160A Reference Design Board Getting Started Guide, Rev. 0, 09/2018

## Chassis and board pictures

Figure 1. LX2160ARDB chassis

The figure below shows the back panel of the LX2160ARDB chassis.

Figure 2. Chassis back panel

The figure below shows the onboard connectors of the LX2160ARDB.

Figure 3. Connectors

The figure below shows the jumpers, LEDs, and DIP switches available on the LX2160ARDB.

Figure 4. Jumpers, LEDs, and DIP switches

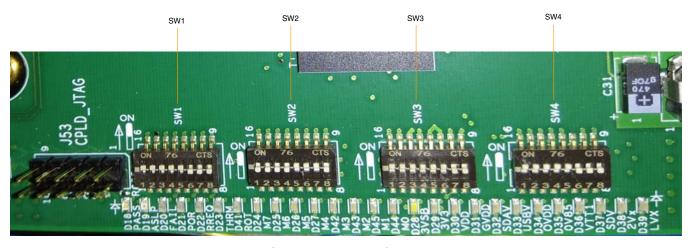

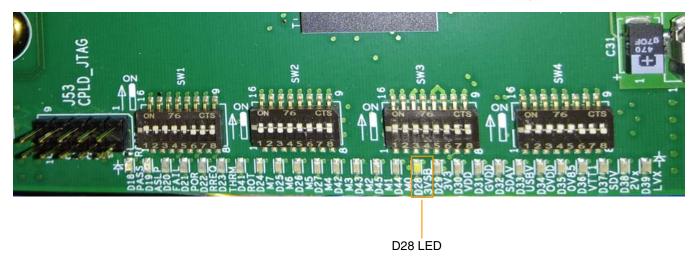

The figure below shows a closer look of the DIP switches.

Figure 5. DIP switches

# 5 Power and reset buttons

The power and reset buttons are present on the front panel of the LX2160ARDB chassis (see Figure 1). Both power and reset buttons are push buttons. The table below describes the power and reset buttons.

QorlQ LX2160A Reference Design Board Getting Started Guide, Rev. 0, 09/2018

## **Connectors**

Table 5. Power and reset buttons

| Identifier | Label | Function    | Description                                                                          |

|------------|-------|-------------|--------------------------------------------------------------------------------------|

| SW5        | PWR   | Power cycle | Press SW5 to turn the power on or off                                                |

| SW7        | RST   | 1 -         | Press SW7 to reset the system, including the device and all the attached peripherals |

You cannot switch off the board completely when the SW\_AUTO\_ON switch (SW4[2]) is set to ON/1. In this mode, pressing the power switch turns the power off briefly, then it immediately turns back on. To turn off power, set the SW\_AUTO\_ON switch to OFF/0 or disconnect the AC power.

# 6 Connectors

The LX2160ARDB has numerous onboard connectors (see Figure 3). The table below describes the LX2160ARDB connectors.

Table 6. LX2160ARDB connectors

| Connector | Description                                                             | Connector type             | Typical connection                                                                     |

|-----------|-------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|

| BT1       | RTC battery                                                             | 3-pin battery holder       | Connects to 3 V standby CR2032 lithium coin cell battery                               |

| J1        | 12 V ATX power supply                                                   | 2x4-pin ATX 12 V connector | Connects to the ATX power supply; both connections are required                        |

| J2        | Main ATX power supply                                                   | 2x12-pin ATX connector     |                                                                                        |

| J3        | Remote power                                                            | 1x2-pin header             | Connects to remote power switch                                                        |

| J4        | Remote reset                                                            | 1x2-pin header             | Connects to remote reset switch                                                        |

| J5        | VDD_DEBUG                                                               | 2x6-pin header             | Connects to Linear Technology PMBus monitoring tool (not included in the hardware kit) |

| J47       | VDD measurement                                                         | 1x2-pin connector          | Allows remote measurement of VDD                                                       |

| J48       | GVDD measurement                                                        | 1x2-pin connector          | Allows remote measurement of GVDD                                                      |

| J11       | Arm JTAG                                                                | 2x5-pin Arm JTAG header    | Connects to CodeWarrior TAP using a 10-pin cable                                       |

| J53       | CPLD JTAG                                                               | 2x5-pin header             | Connects to JTAG interface for CPLD programming                                        |

| J18       | 40G MAC2: 40 Gbit<br>Ethernet                                           | QSFP+ cage                 | Accepts one zQSFP+ transceiver (optical or copper) (not included in the hardware kit)  |

| J19       | 25G MAC5/6: 25 Gbit<br>Ethernet                                         | SFP cage (2)               | Accepts two SFP+ transceivers (optical or copper) (not included in the hardware kit)   |

| J21       | 10G MAC3: 10 Gbit<br>USXGMII                                            | RJ45-19 connector          | Connects to external RJ45 Ethernet cable                                               |

| J22       | 10G MAC4: 10 Gbit<br>USXGMII                                            | RJ45-19 connector          | Connects to external RJ45 Ethernet cable                                               |

| P1        | 1G MAC17/18: 1 Gbit<br>RGMII<br>• 1G MAC17 (bottom)<br>• 1G MAC18 (top) | RJ45 connector (2)         | Connects to external RJ45 Ethernet cable                                               |

Table continues on the next page...

Table 6. LX2160ARDB connectors (continued)

| Connector | Description                        | Connector type             | Typical connection                                                                                              |

|-----------|------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| J45       | 40G interface programming          | 1x3-pin connector          | Provides direct access to CS4223 data EEPROM for programming purposes                                           |

| P2        | UART1 (bottom)                     | DB9 connector (2)          | Connects to external RS-232 cable                                                                               |

|           | UART2 (top)                        |                            |                                                                                                                 |

| P3        | CAN1 (bottom)                      | DB9 connector (2)          | Connects to external CAN adapter cable                                                                          |

|           | CAN2 (top)                         |                            |                                                                                                                 |

| J23       | PCI Express slot #1                | PCIe Gen 4 x4 connector    | Connector for Gen 1/2/3/4 PCIe cards, or right-<br>angle/low-profile chassis adapter accepting<br>Gen 1/2 cards |

| J28       | PCI Express slot #2                | PCle Gen 4 x8 connector    | Connector for Gen 1/2/3/4 PCIe cards                                                                            |

| J24       | SATA1                              | SATA-3 header              | Connector for user-supplied SATA disk                                                                           |

| J25       | SATA2                              | SATA-3 header              | Connector for user-supplied SATA disk                                                                           |

| J26       | SATA3                              | SATA-3 header              | Connector for user-supplied SATA disk                                                                           |

| J27       | SATA4                              | SATA-3 header              | Connector for user-supplied SATA disk                                                                           |

| J30       | USB1 (Host mode by default)        | USB 3.0 Type-A connector   | Connects to USB-compatible device                                                                               |

| J32       | USB2 (OTG mode by default)         | USB 3.0 Micro-AB connector | Connects to USB-compatible device                                                                               |

| J42       | SD card slot                       | SD card receptacle         | Provides access to an SDHC/SDXC card                                                                            |

| J13       | QSPI emulator                      | 2x10-pin connector         | Connects to DediProg EM100Pro QSPI emulator using a sideband cable (ISP-ADP-intel-B)                            |

| J46       | QSPI emulator reset                | 1x2-pin connector          | Allows system reset to be triggered by DediProg EM100Pro emulator using the ISP-ADP-intel-B cable               |

| J34       | I2C1                               | 1x3-pin header             | Provides remote access to I2C1 bus                                                                              |

| J36       | I2C1_CH0                           | 1x3-pin header             | Provides remote access to I2C1 channel 0 segment                                                                |

| J55       | I2C1_CH1                           | 1x3-pin header             | Provides remote access to I2C1 channel 1 segment                                                                |

| J37       | I2C1_CH3                           | 1x3-pin header             | Provides remote access to I2C1 channel 3 segment                                                                |

| J35       | I2C5                               | 1x3-pin header             | Provides remote access to I2C5 bus                                                                              |

| J43       | I2C6                               | 1x3-pin header             | Provides remote access to I2C6 bus                                                                              |

| J10       | GPIO/event access                  | 1x5-pin header             | Provides access to GPIO/event pins                                                                              |

| J38       | Fan #1 (placed near bottom of PCB) | 1x4 connector              | Provides PWM-controlled 12 V power for cooling fans                                                             |

| J39       | Fan #2 (placed near bottom of PCB) | 1x4 connector              |                                                                                                                 |

| J41       | Fan #4 (placed near bottom of PCB) | 1x4 connector              |                                                                                                                 |

| J40       | Fan #3 (placed near bottom of PCB) | 1x4 connector              |                                                                                                                 |

Table continues on the next page...

**Jumpers**

Table 6. LX2160ARDB connectors (continued)

| Connector | Description                          | Connector type                                 | Typical connection                                                              |

|-----------|--------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------|

| J44       | Fan #5 (placed near top of PCB)      | 1x4 connector                                  |                                                                                 |

| J54       | Heatsink fan (placed near<br>Fan #5) | 1x3 connector                                  |                                                                                 |

| J29       | 1588 test                            | 2x6-pin header                                 | Provides access to IEEE 1588 pins                                               |

| J50       | SMA #1                               | Subminiature version A (SMA) coaxial connector | Provides access to recovered IEEE-1588 clock. J50 is not installed, by default. |

| J52       | SMA #2                               | SMA coaxial connector                          | J52 is not installed, by default                                                |

| J14       | DDR4#1 DIMM#1                        | 288-pin DDR4 UDIMM socket                      | Single/dual rank UDIMM inserted                                                 |

| J15       | DDR4#1 DIMM#2                        | 288-pin DDR4 UDIMM socket                      | Single/dual rank UDIMM (optional)                                               |

| J17       | DDR4#2 DIMM#1                        | 288-pin DDR4 UDIMM socket                      | Single/dual rank UDIMM inserted                                                 |

| J16       | DDR4#2 DIMM#2                        | 288-pin DDR4 UDIMM socket                      | Single/dual rank UDIMM (optional)                                               |

# 7 Jumpers

Jumpers (or shorting headers) are used to select some options that either do not change often or involve power conduction. The LX2160ARDB jumpers are shown in Figure 4 and are described in the table below.

Table 7. LX2160ARDB jumpers

| Jumper | Туре              | Name/function                                  | Description                                                                                                |

|--------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| J6     | 1x2-pin connector | TA_BB_TMP_DETECT_B enable                      | Open: TA_BB_TMP_DETECT_B pin is grounded                                                                   |

|        |                   |                                                | Shorted: TA_BB_TMP_DETECT_B pin is powered (default setting)                                               |

| J7     | 1x2-pin connector | VBAT power for TA_BB_VDD enable                | Not supported. Do not install J7. See <i>QorlQ LX2160A Reference Design Board Errata</i> for more details. |

| J8     | 1x2-pin connector | PROG_MTR voltage control (for NXP use only)    | Open: PROG_MTR pin is powered off (default setting)                                                        |

|        |                   |                                                | Shorted: PROG_MTR pin is powered by OVDD (1.8 V)                                                           |

| J9     | 1x2-pin connector | TA_PROG_SFP voltage control (for NXP use only) | Open: TA_PROG_SFP pin is powered off (default setting)                                                     |

|        |                   |                                                | Shorted: TA_PROG_SFP pin is powered by OVDD (1.8 V)                                                        |

| J31    | 1x2-pin connector | USB1 mode setting                              | Open: USB1 works in Device mode                                                                            |

|        |                   |                                                | Shorted: USB1 works in Host mode (default setting)                                                         |

Table continues on the next page...

Table 7. LX2160ARDB jumpers (continued)

| Jumper | Туре              | Name/function           | Description                                                |

|--------|-------------------|-------------------------|------------------------------------------------------------|

| J33    | 1x2-pin connector | USB2 mode setting       | Open: USB2 works in On-The-Go (OTG) mode (default setting) |

|        |                   |                         | Shorted: USB2 works in Host mode                           |

| J56    | 2x3-pin connector | Inphi CS4223 GUI access | Normal: 1-2 short, 5-6 short (default setting)             |

|        |                   |                         | GUI mode: 1-2 open, 5-6 open                               |

| J57    | 1x2-pin connector | Inphi CS4223 GUI enable | Normal: Open (default setting)                             |

|        |                   |                         | GUI mode: Short                                            |

| J58    | 1x2-pin connector | Fan speed               | Open: 100% speed                                           |

|        |                   |                         | Short: 50% speed (default setting)                         |

## **NOTE**

Most of these jumpers are installed during assembly, and they do not require any change.

## 8 LEDs

The LX2160ARDB has numerous onboard light-emitting diodes (LEDs), which can be used to monitor various system functions, such as power on, reset, board faults, and so on. The information collected from LEDs can be used for debugging purposes. The table below lists all the LEDs present on the LX2160ARDB.

Table 8. LX2160ARDB LEDs

| Reference<br>designator | LED color | LED name | Description (when LED is ON)                                                                                                                                                                                                                              |

|-------------------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D1                      | Yellow    | PRELOAD  | The PSU-loading FET is active; it may be hot during power-up or shortly afterward. Avoid touching this area.                                                                                                                                              |

| D18                     | Blue      | PASS     | The CPLD has completed power and reset sequencing and no errors are detected                                                                                                                                                                              |

| D19                     | Yellow    | ASLEEP   | The processor has not exited Sleep mode, which generally indicates:  • Improper RCW source selection  • Boot memory does not contain a valid RCW/PBL  • PLL multipliers in the RCW data are not compatible with the fixed SYSCLK, DDRCLK, or SDCLK values |

| D20                     | Red       | FAIL     | One of the following has happened:  • A thermal over-temperature fault has occurred  • One or more power supplies have not started  • Software has set the register CTL[0] (FAIL) to indicate a software fault                                            |

| D21                     | Red       | PORST    | The CPLD is asserting PORESET_B to the processor and is in the process of restarting the system                                                                                                                                                           |

| D22                     | Red       | RST REQ  | The processor is asserting RESET_REQ_B. This is typically due to the reasons described for the ASLEEP LED.                                                                                                                                                |

| D23                     | Red       | THERM    | Thermal monitors have detected a thermal fault and have shut down the system                                                                                                                                                                              |

Table continues on the next page...

QorlQ LX2160A Reference Design Board Getting Started Guide, Rev. 0, 09/2018

Table 8. LX2160ARDB LEDs (continued)

| Reference<br>designator | LED color | LED name | Description (when LED is ON)  NOTE: Unless reprogrammed by user software, the thermal trip point is 85 °C.  The processor has been installed in the socket rotated 90, 180, or 270 degrees from the pin 1 orientation. The system and device power supplies have been shut down to protect the device.  General status. See Multi-status LEDs for details. |  |  |

|-------------------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| -                       |           |          |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D41                     | Red       | ROTERR   | 180, or 270 degrees from the pin 1 orientation. The system and device power supplies have been shut down to protect                                                                                                                                                                                                                                        |  |  |

| D24                     | Green     | M7       | General status. See Multi-status LEDs for details.                                                                                                                                                                                                                                                                                                         |  |  |

| D25                     | Green     | M6       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D26                     | Green     | M5       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D27                     | Green     | M4       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D42                     | Green     | M3       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D43                     | Green     | M2       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D45                     | Green     | M1       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D44                     | Green     | M0       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| D28                     | Green     | 3VSB     | The ATX power supply is supplying 3.3 V "standby power" to the system. The system cannot power up unless this supply is provided.                                                                                                                                                                                                                          |  |  |

| D29                     | Green     | 3V3      | 3V3 ATX power supply is operating correctly                                                                                                                                                                                                                                                                                                                |  |  |

| D30                     | Green     | VDD      | VDD (processor core) power supply is operating correctly                                                                                                                                                                                                                                                                                                   |  |  |

| D31                     | Green     | GVDD     | GVDD (DDR4) power supply is operating correctly                                                                                                                                                                                                                                                                                                            |  |  |

| D32                     | Green     | SDAV     | SD_AVDD power supply is operating correctly                                                                                                                                                                                                                                                                                                                |  |  |

| D33                     | Green     | USBV     | USB_SVDD power supply is operating correctly                                                                                                                                                                                                                                                                                                               |  |  |

| D34                     | Green     | OVDD     | OVDD power supply is operating correctly                                                                                                                                                                                                                                                                                                                   |  |  |

| D35                     | Green     | 0V85     | 0V85 power supply is operating correctly                                                                                                                                                                                                                                                                                                                   |  |  |

| D36                     | Green     | VTT1     | VTT1 power supply is operating correctly                                                                                                                                                                                                                                                                                                                   |  |  |

| D37                     | Green     | SDV      | SD_VDD power supply is operating correctly                                                                                                                                                                                                                                                                                                                 |  |  |

| D38                     | Green     | 2Vx      | 2V1 and 2V5 power supplies are operating correctly                                                                                                                                                                                                                                                                                                         |  |  |

| D39                     | Green     | LVX      | 0V9 and 1V2 power supplies are operating correctly                                                                                                                                                                                                                                                                                                         |  |  |

| D5                      | Green     | QSFP     | A QSFP module is installed in the QSFP port                                                                                                                                                                                                                                                                                                                |  |  |

| D9                      | Green     | 25GMAC5  | An SFP module is installed in 25G MAC5 SFP port                                                                                                                                                                                                                                                                                                            |  |  |

| D10                     | Green     | 25GMAC6  | An SFP module is installed in 25G MAC6 SFP port                                                                                                                                                                                                                                                                                                            |  |  |

| D11                     | Green     | USB1_5V  | 5 V power is supplied to the USB #1 connector for external devices                                                                                                                                                                                                                                                                                         |  |  |

| D13                     | Green     | USB2_5V  | 5 V power is supplied to the USB #2 connector for external devices                                                                                                                                                                                                                                                                                         |  |  |

## 8.1 Multi-status LEDs

The board includes eight multi-status LEDs that indicate hardware activity; however, software can override these LEDs to use them for debugging purposes. The table below describes the functions of the multi-status LED arrays.

# Table 9. LED array functions

| LED | Startup (from power on to power-up complete + 2 seconds) | Normal (after 2 seconds)                             | User-defined (if register CTL[1] (LED) = 1) |

|-----|----------------------------------------------------------|------------------------------------------------------|---------------------------------------------|

| M7  | Power Sequencer state                                    | "Idle" pattern, a pattern shown to indicate that the |                                             |

| M6  | (see Table 10)                                           | FPGA has completed all startup activities            | the LED register                            |

| M5  |                                                          |                                                      |                                             |

| M4  |                                                          | Off always                                           |                                             |

| МЗ  | Reset Sequencer state                                    | Live I2C1_SCL activity                               |                                             |

| M2  | (see Table 11)                                           | Live I2C remote activity                             |                                             |

| M1  |                                                          | Same as M[3:2], except that short pulses are         |                                             |

| MO  |                                                          | stretched to 500 ms for easier detection             |                                             |

## **NOTE**

The LX2160ARDB power up voltage sequence diagram (LX2160ARDB Reference Manual) lists the power supplies assigned to each tier.

Table 10. Power Sequencer state

| State    | LED: M[7:4] | Description                                                                                 |

|----------|-------------|---------------------------------------------------------------------------------------------|

| IDLE     | 1110 = 0xE  | Waiting for power-on events (for example, switch)                                           |

| WAIT_ATX | 0000 = 0x0  | Waiting for ATX PSU to report stable                                                        |

| EN_TIER1 | 0001 = 0x1  | Enable tier 1 PSUs, wait for tier 1 power-good reports                                      |

| EN_TIER2 | 0010 = 0x2  | Enable tier 2 PSUs, wait for tier 2 power-good reports                                      |

| EN_TIER3 | 0011 = 0x3  | Enable tier 3 PSUs, wait for tier 3 power-good reports                                      |

| EN_TIER4 | 0100 = 0x4  | Enable tier 4 PSUs, wait for tier 4 power-good reports                                      |

| WAIT_ALL | 0110 = 0x6  | Wait for all unmanaged PSUs to report power-good                                            |

| PG_FAIL  | 0111 = 0x7  | All power supplies were not stable within 1800*30 ns after the last power was enabled       |

| STABLE   | 1000 = 0x8  | Power sequencing complete. Wait for power-off events.                                       |

| DISABLE  | 1101 = 0xD  | Disable tiers 41 PSUs, in that order, with 1 ms delay                                       |

| FAULT    | 1111 = 0xF  | Fault occurred. Power supplies were shut down due to thermal faults or die rotation errors. |

Table 11. Reset Sequencer state

| State       | LED: M[3:0] | Description                                       |

|-------------|-------------|---------------------------------------------------|

| IDLE        | 0000 = 0x0  | Waiting for initial reset events                  |

| RECONFIG    | 0010 = 0x2  | Update configuration from registers               |

| CLOCK_LOCK  | 0101 = 0x5  | Wait for clock PLLs to stabilize                  |

| RELEASE_ALL | 0110 = 0x6  | Release all hardware resets except DUT            |

| RELEASE_DUT | 0111 = 0x7  | Release DUT from reset                            |

| STABLE      | 1000 = 0x8  | Reset sequencing complete. Wait for reset events. |

| RESET_REQ   | 1001 = 0x9  | Start reset due to DUT RESET_REQ_B                |

Table continues on the next page...

## **DIP** switches

Table 11. Reset Sequencer state (continued)

| State      | LED: M[3:0] | Description                                              |

|------------|-------------|----------------------------------------------------------|

| PORESET    | 1010 = 0xA  | Start reset due to JTAG_RST_B                            |

| RST_WATCH  | 1011 = 0xB  | Start reset due to watchdog timeout                      |

| RST_BY_REG | 1100 = 0xC  | Start reset due to setting register bit RST_CTL[RST] = 1 |

| RST_BY_SW  | 1101 = 0xD  | Start reset due to pushbutton switch                     |

| RECONFIG   | 1110 = 0xE  | Start reset due to reconfig request via RCFG[GO] = 1     |

| POST_RST   | 1111 = 0xF  | Wait for reset requests to clear                         |

# 9 DIP switches

The LX2160ARDB provides dual inline package (DIP) switches to allow easy configuration of the system for the most popular board options. These switches are stored in BRDCFG and DUTCFG registers by CPLD before being used, allowing software (either local or remote) to reconfigure the system as needed.

The table below explains the DIP switches available in the LX2160ARDB. For each DIP switch:

- If the switch is up (on), the value is 1

- If the switch is down (off), the value is 0

Table 12. Switch settings

| Switch   | Supported function    |                                                                                                                                                                                                                                                                               | Description     |                       |                                    |  |

|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|------------------------------------|--|

| SW1[1:4] | RCW fetch location    | SW_RCW_SRC[                                                                                                                                                                                                                                                                   | SW_RCW_SRC[3:0] |                       |                                    |  |

|          | CFG_RCW_SRC[3:0]      | <ul> <li>0000: Hard-coded RCW</li> <li>1000: SDHC1: SD card</li> <li>1001: SDHC2: eMMC</li> <li>1010: I2C boot EEPROM</li> <li>1100: XSPI sNAND, 2 KB pages</li> <li>1101: XSPI sNAND, 4 KB pages</li> <li>1111: XSPI serial NOR, 24-bit address (default setting)</li> </ul> |                 |                       |                                    |  |

| SW1[5]   | Reset mode            | SW_RST_MODE                                                                                                                                                                                                                                                                   |                 |                       |                                    |  |

|          | RESET_REQ_B           | <ul> <li>0: Ignore RESET_REQ_B</li> <li>1: Trigger system reset on assertion of RESET_REQ_B (default setting)</li> </ul>                                                                                                                                                      |                 |                       |                                    |  |

| SW1[6:8] | XSPI_A device mapping |                                                                                                                                                                                                                                                                               | <del>-</del>    | A chip-selects are co | onnected to                        |  |

|          | CFG_XSPI_MAP[3:0]     | devices/periphera                                                                                                                                                                                                                                                             | als.            |                       |                                    |  |

|          |                       | Bit value XSPI_A_CS0 XSPI_A_CS1 Description                                                                                                                                                                                                                                   |                 |                       |                                    |  |

|          |                       | 000 (default DEV#0 DEV#1 Boot from de setting)                                                                                                                                                                                                                                |                 |                       |                                    |  |

|          |                       | 001                                                                                                                                                                                                                                                                           | DEV#1           | DEV#0                 | Boot from alternative flash memory |  |

Table continues on the next page...

Table 12. Switch settings (continued)

| Switch   | Supported function                     |                                                                                                                                         | Des                                       | cription                           |                                                                       |  |

|----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|-----------------------------------------------------------------------|--|

|          |                                        | Bit value                                                                                                                               | XSPI_A_CS0                                | XSPI_A_CS1                         | Description                                                           |  |

|          |                                        | 010                                                                                                                                     | QSPI emulator                             | DEV#0                              | Boot from QSPI<br>emulator,<br>program default<br>flash memory        |  |

|          |                                        | 011                                                                                                                                     | QSPI emulator                             | DEV#1                              | Boot from QSPI<br>emulator,<br>program<br>alternative flash<br>memory |  |

|          |                                        | 100                                                                                                                                     | DEV#0                                     | QSPI emulator                      | Emulator access                                                       |  |

| SW2[1]   | PCIe Spread-Spectrum enable CFG_SPREAD |                                                                                                                                         |                                           | ts are fixed (default stare spectr |                                                                       |  |

| SW2[2]   | CS4223 configuration                   | SW_P40IN                                                                                                                                |                                           |                                    |                                                                       |  |

|          | CFG_40GE_ROM                           | 0: CS4223 40 GbE PHY is not self-configured (default setting)     1: CS4223 40 GbE PHY is self-configured on reset                      |                                           |                                    |                                                                       |  |

| SW2[3]   | PCIe slot clock enable                 | SW_SLOTCLK                                                                                                                              |                                           |                                    |                                                                       |  |

|          | CFG_CLKEN_SLOT[1:2]_B                  | <ul> <li>0: PCle slots are clocked only when a card is installed (default setting)</li> <li>1: PCle slots are clocked always</li> </ul> |                                           |                                    |                                                                       |  |

| SW2[4]   | CS4223 MDC clock generation            | SW_MDC40G_EN  • 0: CS4223 does not receive clock during PORESET_B (default setting)  • 1: CS4223 receives ~1 MHz clock during PORESET_B |                                           |                                    |                                                                       |  |

| SW2[5]   | SDHC voltage control                   | SW_SDHC_VCTL                                                                                                                            |                                           |                                    |                                                                       |  |

| SW2[6]   | Unused                                 | SW_ENGUSE0                                                                                                                              |                                           |                                    |                                                                       |  |

|          | CFG_ENG_USE0                           | Reserved with 1                                                                                                                         | as the default setting                    | 9                                  |                                                                       |  |

| SW2[7]   | Unused                                 | SW_ENGUSE1                                                                                                                              |                                           | -                                  |                                                                       |  |

|          | CFG_ENG_USE1                           | Reserved with 1                                                                                                                         | as the default setting                    | 9                                  |                                                                       |  |

| SW2[8]   | DDR clock source selection             | SW_ENGUSE2                                                                                                                              |                                           |                                    |                                                                       |  |

|          | CFG_ENG_USE2                           |                                                                                                                                         | cked from DDRCLK<br>cked from differentia |                                    |                                                                       |  |

| SW3[1:3] | Device type selection                  | SW_TESTSEL_E                                                                                                                            | 3 + SW_SVR[0:1]                           |                                    |                                                                       |  |

|          | TEST_SEL_B,<br>CFG_SVR[0:1]            |                                                                                                                                         |                                           | g)                                 |                                                                       |  |

| SW3[4]   | SoC use                                | SW_SOCUSE                                                                                                                               |                                           |                                    |                                                                       |  |

|          | CFG_SOC_USE                            | 1: Normal mode (default setting)                                                                                                        |                                           |                                    |                                                                       |  |

|          |                                        | NOTE: Do not o                                                                                                                          | hange the default se                      | etting of this switch.             |                                                                       |  |

| SW3[5:6] | CPU device override                    | SW_CPU_SEL                                                                                                                              |                                           |                                    |                                                                       |  |

Table continues on the next page...

Table 12. Switch settings (continued)

| Switch   | Supported function                             | Description                                                                                                                                      |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                | 00: Override to LS2-family device     01: Override to LX2-family device     10: Reserved     11: Reserved (default setting)                      |

|          |                                                | NOTE: This switch's settings are ignored if SW3[7] is set to 0.                                                                                  |

| SW3[7]   | Force CPU selection                            | SW_CPU_FORCE  • 0: Normal mode (default setting)  • 1: Use SW_CPU_SEL instead of CPU_ID  NOTE: Do not change the default setting of this switch. |

| SW3[8]   | Unused                                         | Reserved with 0 as the default setting                                                                                                           |

| SW4[1]   | Bypass mode                                    | SW_BYPASS_B                                                                                                                                      |

|          |                                                | <ul><li>0: Disable thermal monitors and other alarms</li><li>1: Normal operation (default setting)</li></ul>                                     |

| SW4[2]   | Automatic power on                             | SW_AUTO_ON  • 0: Normal power on/off (default setting)  • 1: Always power up                                                                     |

| SW4[3]   | System configuration write protect  CFG_MEM_WP | SW_CFG_WP  • 0: Allow writes to SYSID and I2C flash  • 1: Write-protect SYSID and I2C flash (default setting)                                    |

| SW4[4]   | JTAG Scan mode                                 | SW_TBSCAN                                                                                                                                        |

| S [1]    | TBSCAN_EN_B                                    | 0: Boundary Scan mode     1: Debugging mode (default setting)                                                                                    |

| SW4[5]   | Boot Box mode                                  | SW_BOOTBOX_B  • 0: Enable Boot Box mode  • 1: Normal operating mode (default setting)                                                            |

| SW4[6]   | VDD power enable                               | SW_VDD_DIS  • 0: Enable VDD power supply (default setting)  • 1: Disable VDD power supply                                                        |

| SW4[7:8] | General purpose                                | SW_GPIN[7:6]                                                                                                                                     |

|          | CFG_GPIN[7:6]                                  | 00: Software or end-user defined (default setting)                                                                                               |

The table below summarizes the default switch settings of the LX2160ARDB DIP switches.

Table 13. Default switch settings

| DIP switch | Default setting |

|------------|-----------------|

| SW1        | 1111_1000       |

| SW2        | 0000_0110       |

| SW3        | 1111_1100       |

| SW4        | 1011_1000       |

# 10 Getting started with LX2160ARDB

This section explains:

- Prerequisites

- Booting LX2160ARDB

# 10.1 Prerequisites

To set up your LX2160ARDB, you need the items listed in the table below.

Table 14. Prerequisites

| Item                                                        | Available in | Purpose / required action                                                                                                                                                      |

|-------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                             | board kit?   |                                                                                                                                                                                |

|                                                             |              | Hardware                                                                                                                                                                       |

| Host computer system capable of running a terminal emulator | No           | Host computer (for example, Windows PC, Linux system, or Mac) to control and monitor the LX2160ARDB from the serial console via a serial terminal emulator, such as Tera Term. |

|                                                             |              | NOTE: You can also use a Linux machine to connect to the board console via a Linux utility, such as minicom.                                                                   |

| AC power cord                                               | Yes          | To connect the board to AC power supply                                                                                                                                        |

| DB9 female to DB9 female serial cable                       | Yes          | To make a console connection from UART1 port of the board                                                                                                                      |

| USB-to-serial adapter                                       | No           | To connect the serial port of DB9 cable to the USB port of the host computer                                                                                                   |

| Cat-6 Ethernet cable                                        | Yes          | To connect the board to network to get updated board software                                                                                                                  |

| CodeWarrior TAP (optional)                                  | No           | To debug and control the board using the CodeWarrior IDE                                                                                                                       |

|                                                             |              | Software                                                                                                                                                                       |

| USB to serial/UART/RS-232 driver                            | No           | Download and install on the host computer from Internet                                                                                                                        |

| Tera Term (serial terminal emulator)                        | No           | Download and install on the host computer from Internet                                                                                                                        |

| TFTP server                                                 | No           | Download and install on the host computer from Internet                                                                                                                        |

# 10.2 Booting LX2160ARDB

When power is supplied to the board, then the boot loader (U-Boot) image located in FlexSPI NOR flash DEV#0 runs, if the board is configured with the default switch settings.

Follow these steps to boot the board:

- 1. Ensure that you have met the prerequisites described in Table 14.

- 2. Open the chassis top cover and ensure that the board is configured with the default switch settings, as mentioned in Table 13.

- 3. Verify that the board has default jumper settings (see Jumpers).

QorlQ LX2160A Reference Design Board Getting Started Guide, Rev. 0, 09/2018

## Getting started with LX2160ARDB

4. Connect one end of the AC power cord to the wall mount power switch and the other end of the cable to the power jack available on the chassis back panel, as shown in the figure below.

Figure 6. Power supply connection

## **NOTE**

As a precautionary step, the power switch mounted on the wall (if available) must be turned off before connecting the power cord.

5. Turn on the wall mount power switch. The D28 LED (3VSB) turns ON when the standby power is available (see fgure below).

## Figure 7. Standby power indicator

6. Connect one end of the DB9 female to DB9 female cable to the UART1 port available on chassis front panel (see figure below) and the other end of the cable to the USB-to-serial adapter. Connect the other end of the USB-to-serial adapter to the USB port of the host machine. This connection allows you to make a console connection between the board and host computer to see the console output.

## Figure 8. Console connection

7. Optionally, connect the CodeWarrior TAP to the board by performing the following steps:

#### NOTE

Follow the instructions included with the CodeWarrior package to set up the environment and host attachment, such as USB and Ethernet.

- a. Connect the 10-pin micro adapter (CWH-CTP-CTX10-YE), provided with the CodeWarrior TAP, to the CodeWarrior TAP.

- b. Connect one end of the 10-wire cable (gray ribbon cable) to the 10-pin micro adapter (both ends of the wire are keyed and can be connected on either side).

- c. Connect the other end of the 10-wire cable to the 10-pin Arm JTAG header (J11) on the board, as shown in the figure below.

## Getting started with LX2160ARDB

Figure 9. CodeWarrior TAP connection

## NOTE

Pin 1 of the gray ribbon cable connector should align with pin 1 of the debug port header on the board.

- 8. Optionally, connect the Ethernet cable if you want to connect your board to the network, for example, for obtaining latest board software and updating board images.

- 9. Set up Tera Term on the host computer:

- a. Start Tera Term. The Tera Term console appears along with the **Tera Term: New connection** dialog.

- b. On the **Tera Term: New connection** dialog, select the **Serial** option, and ensure that **COM: USB-to-Serial Comm Port** is selected in the **Port** menu.

- c. Click **OK** to close the **Tera Term: New connection** dialog.

- d. Choose **Setup > Serial port** from the Tera Term console menu bar. The **Tera Term: Serial port setup** dialog appears.

- e. On the **Tera Term: Serial port setup** dialog, configure the serial port of the host computer with the following settings:

• Baud rate: 115200

Data: 8 bitParity: noneStop: 1 bit

• Flow control: none