#### **Testhouse**

C&S group GmbH Am Exer 19b

D-38302 Wolfenbuettel

Phone: +49 5331/ 90 555 - 0 Fax: +49 5331/ 90 555 - 110

Date of Approval: 2016-Mar-17

P15 0209-

**Final**

**Test Report**

**Device Under Test**

Customer

Name

Object Family MC9S12ZVL

Manufacturer Freescale Semiconductor

Type S12ZVL128

Sample marking P9ZV LA12MLF ON37P

**CCTCJA**

Order No. P15\_0209

Freescale Semiconductor Mexico

2\_017\_MagniV\_S12ZVL128\_L22\_Report00

Address Periférico Sur 8110

Col. El Mante

TLAQUEPAQUE, JALISCO, 45609

**MEXICO**

Number of Pages

**Test Period**

51

from ww11/2016 until ww11/2016

**Test Method / Test Requirement**

**Performed Tests and References**

LIN Conformance Test Specification

1 LIN OSI Layer 1 – Physical Layer For LIN devices with Rx and Tx access For the LIN Physical Layer Specification

Revision 2.2 (Dec. 31th, 2010)

LIN OSI Layer1 Physical Layer for LIN Specification 2.2

Version 2.2

**Conformance Test Results**

The Test Results refer to the delivered device.

1 LIN OSI Layer 1 for Revision 2.2

Pass

For detailed information see chapter Test List at the following pages.

This Test Report shall not be reproduced without written approval of the test house, except in full and unchanged.

Approved by Test performed by

L. Kukla, Project Manager

J. Eversmeier, Project Engineer

## **Table of Content**

| REVISION HISTORY                                                                                             | 3       |

|--------------------------------------------------------------------------------------------------------------|---------|

| 1 DEVICE UNDER TEST (DETAILED)                                                                               | 4       |

| 2 SETUP FOR DEVICE UNDER TEST                                                                                | 5       |

| 3 TEST EQUIPMENT                                                                                             | 10      |

| 4 TECHNICAL CORRESPONDENCE                                                                                   | 11      |

| 5 TEST LIST                                                                                                  |         |

| 5.1 DYNAMIC TESTS                                                                                            |         |

| 5.2 STATIC TESTS                                                                                             |         |

| 6 TEST PROTOCOL DYNAMIC TESTS                                                                                |         |

|                                                                                                              |         |

| TC 2.1 OPERATING VOLTAGE RANGE                                                                               |         |

| TC 2.1.2 Voltage Ramp [18V7.0V], 0.1V/s [down]                                                               |         |

| TC 2.2 THRESHOLD VOLTAGES                                                                                    |         |

| TC 2.2.1 IUT as Receiver: V <sub>SUP</sub> @ V <sub>BUS_DOM</sub> (down)                                     |         |

| TC 2.2.2 IUT as Receiver: V <sub>SUP</sub> @ V <sub>BUS REC</sub> (up)                                       |         |

| TC 2.2.3 IUT as Receiver: VSUP @ V <sub>BUS</sub>                                                            |         |

| TC 2.3 VARIATION OF V <sub>SUP NON OP</sub> ∈ [- 0.3V7V], [18V40V]                                           |         |

| TC 2.3.3 IUT as Transceiver 1.1k $\Omega$ + diode to $V_{LIN}$ = 18 V                                        |         |

| TC 2.4 I <sub>BUS</sub> UNDER SEVERAL CONDITIONS                                                             | 34      |

| TC 2.4.1 I <sub>BUS_LIM</sub> @ Dominant State (Driver On)                                                   | 34      |

| TC 2.4.2 $I_{BUS\_PAS\_dom}$ : IUT in Recessive State: $V_{BUS} = 0V$                                        | 34      |

| TC 2.4.3 $I_{BUS\_PAS\_rec}$ : IUT in Recessive State: $V_{SUP} = 7V$ with Variation of $V_{BUS} \in [8V 1]$ | !8V] 35 |

| TC 2.5 SLOPE CONTROL                                                                                         | 36      |

| TC 2.5.1 Measuring the Duty Cycle @ 10.4 kBit/sec – IUT as Transmitter                                       |         |

| TC 2.5.2 Measuring the Duty Cycle @ 20 kBit/sec – IUT as Transmitter                                         |         |

| TC 2.6 PROPAGATION DELAY                                                                                     |         |

| TC 2.7 GND/V <sub>BAT</sub> SHIFT TEST – DYNAMIC                                                             |         |

| TC 2.8 FAILURE                                                                                               |         |

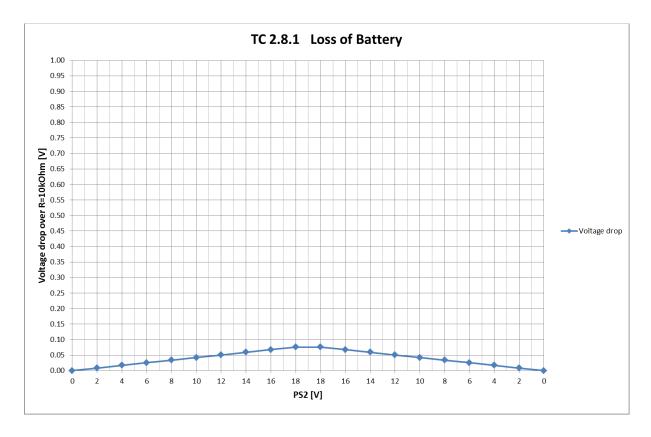

| TC 2.8.1 Loss of Battery                                                                                     |         |

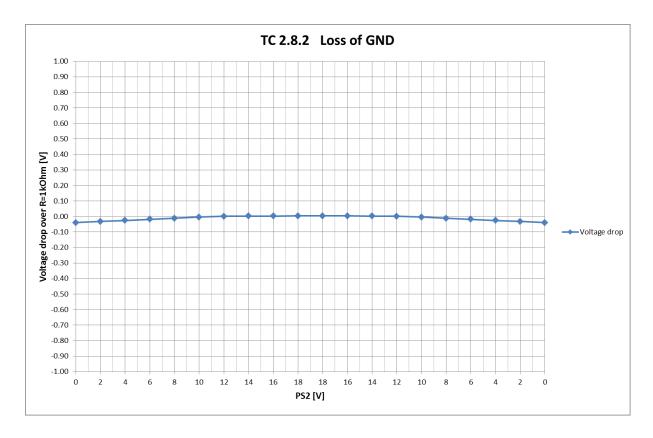

| TC 2.8.2 Loss of GND                                                                                         |         |

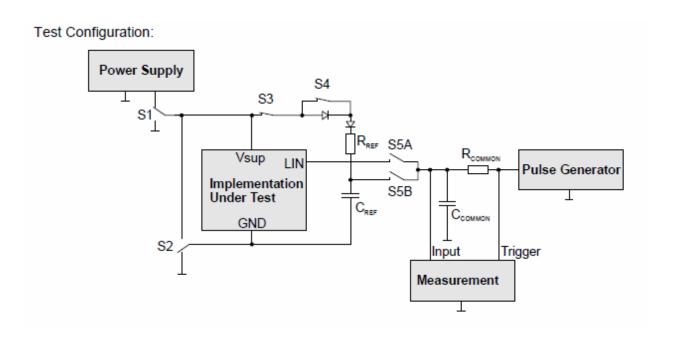

| TC 2.9 VERIFYING INTERNAL CAPACITANCE AND DYNAMIC INTERFERENCE – IUT AS SLAVE                                |         |

| TC 2.9.2 IUT loss of GND                                                                                     |         |

| TC 2.9.3 IUT loss of $V_{SUP}$                                                                               |         |

| 1 0 2.0.0 10 1 1000 of 1 Sup                                                                                 | 01      |

# **Revision History**

| Old revision | New revision | Amendment Description | Editor |

|--------------|--------------|-----------------------|--------|

| _            | 00           | Final version         | LK     |

# **Device Under Test (detailed)**

| General                     |                           |  |

|-----------------------------|---------------------------|--|

| Date of Sample Arrival      | 26.02.2016                |  |

| Manufacturer                | Freescale Semiconductor   |  |

| Sample Marking              | P9ZV LA12MLF ON37P CCTCJA |  |

| Test performed with DUT no. | #1                        |  |

| Device Specification |           |  |

|----------------------|-----------|--|

| Family Name          | MC9S12ZVL |  |

| Version              | S12ZVL128 |  |

| Design step          | -         |  |

| HW-Version           | -         |  |

| SW-Version           | -         |  |

| Documentation           |                                                                                                    |  |

|-------------------------|----------------------------------------------------------------------------------------------------|--|

| Hardware manual         | [DRAFT]TRK-S12ZVL128_QuickStartGuide_05_11_2015.pdf ZVL128[Preliminary]_Schematic_EVBSPF-28765.pdf |  |

| User manual / datasheet | MC9S12ZVL_Rev2.00_Draft_G.pdf                                                                      |  |

| Device Classification |    |  |

|-----------------------|----|--|

| According to          | A+ |  |

| Software Specification |   |  |  |

|------------------------|---|--|--|

| IDE -                  |   |  |  |

| Compiler               | - |  |  |

| Device                 | - |  |  |

| Supplement             |                                                               |  |

|------------------------|---------------------------------------------------------------|--|

| Node Capability File - |                                                               |  |

| Connection plan        | P15_0209-<br>2_009_MagniV_S12ZVL128_L22_Connection_Plan00.pdf |  |

- 4 of 51 -

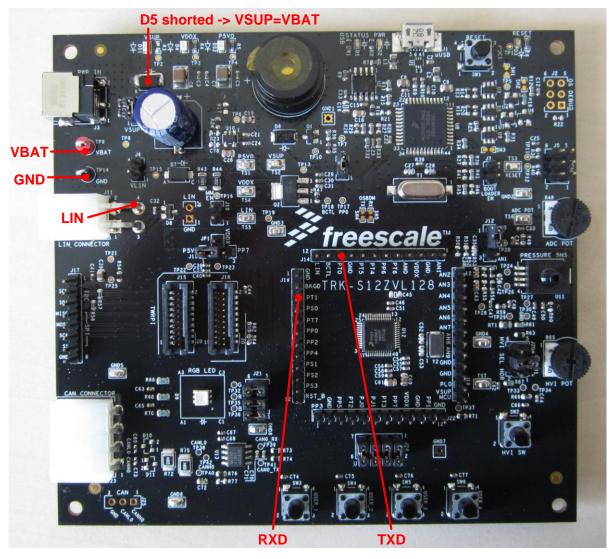

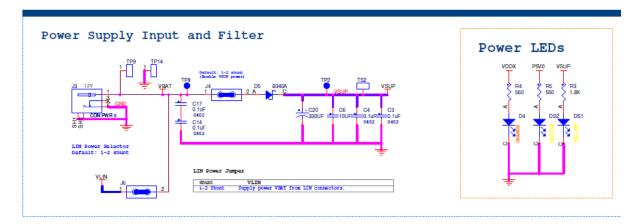

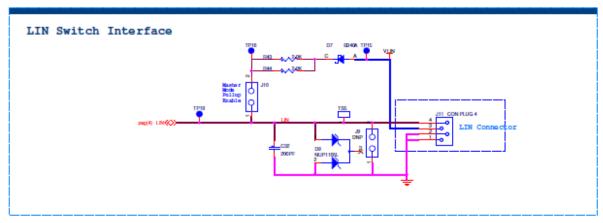

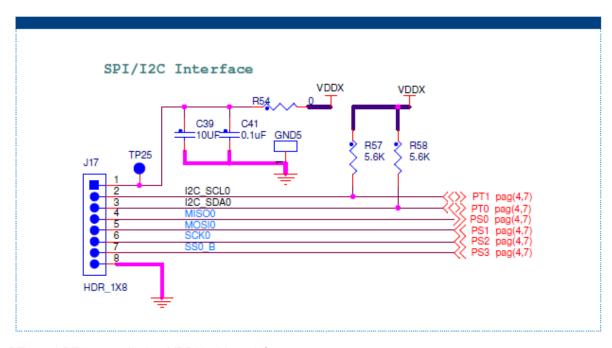

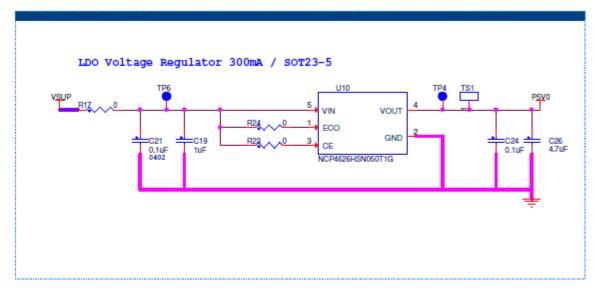

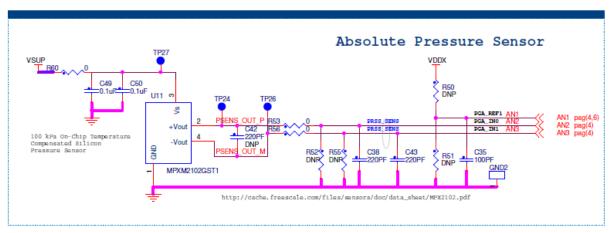

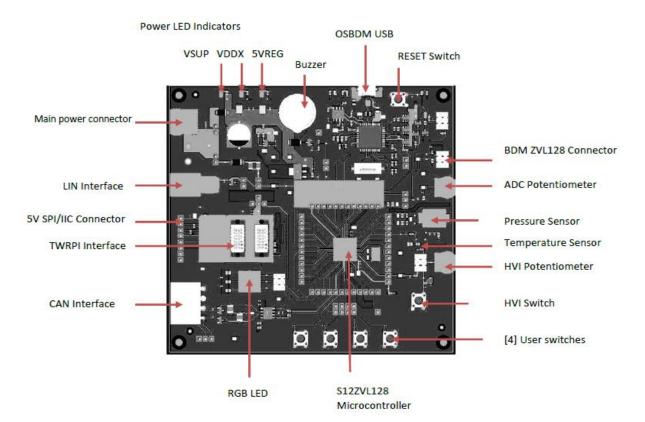

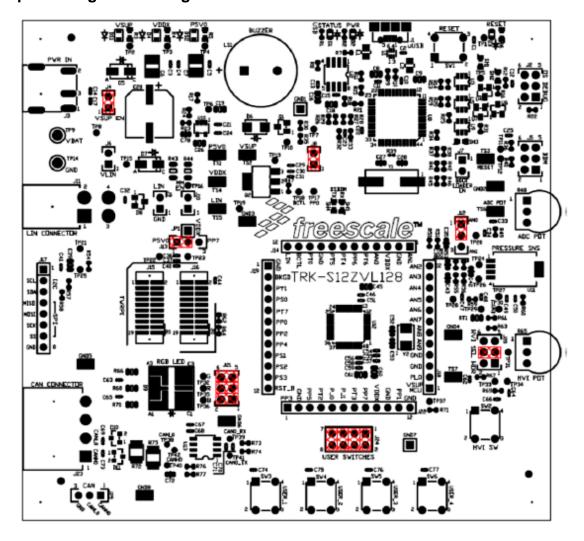

## 2 Setup for Device Under Test

| Function             | Description                                                                                                                                                           |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RXD                  | Internal signal LPRXD was routed to port PT1 (J19 pin 3). PS0 has a push/pull output, no external pull-up resistor required.                                          |  |  |

| TXD                  | Internal signal LPTXD was routed to port PT0 (J14 pin 10).                                                                                                            |  |  |

| LIN                  | C32 = 200pF Slave node capacitance; D8 = NUP1105L (ESD Diode)                                                                                                         |  |  |

| VSUP                 | VSUP=VBAT; D5 shorted                                                                                                                                                 |  |  |

| IO Voltage VDDX=3.3V |                                                                                                                                                                       |  |  |

| Slew Rate            | All Tests were performed with a slew rate optimized for 20kBit/s, except test group 2.5.1.  Test group 2.5.1 was performed with a slew rate optimized for 10.4kBit/s. |  |  |

#### **Schematic**

D5 shorted -> VSUP=VBAT; R3 removed; C20 replaced for 50V

J10 open

PT0 and PT1 are pulled to VDDX with  $5.6k\Omega$

#### R17 removed

R60 removed

#### TRK-S12ZVL

## **Jumper Configuration Diagram**

# 3 Test Equipment

The following test equipment and test system have been used.

| No.                              | Component                                           | Manufacturer    | Version / Type    | ID          |  |

|----------------------------------|-----------------------------------------------------|-----------------|-------------------|-------------|--|

| C&S                              | C&S Hardware                                        |                 |                   |             |  |

| LIN 2.2                          |                                                     |                 |                   |             |  |

| 1                                | LIN-Power switch Board                              | C&S             | Rev 2.1 CSHW_0000 |             |  |

| 2                                | LIN-Stimulation Board                               | C&S             | Rev 2.2           | CSHW_000096 |  |

| 3                                | LIN-GND-shift Board                                 | C&S             | Rev 1.3           | CSHW_000075 |  |

| 4                                | LIN-IUT Board                                       | C&S             | Rev 2.1           | CSHW_000071 |  |

| 5                                | LIN-Adapter Board                                   | C&S             | Rev 2.2           | CSHW_000097 |  |

| 6                                | LIN-Adapter Board                                   | C&S             | Rev 2.2           | CSHW_000073 |  |

| 7                                | LIN-Adapter Board                                   | C&S             | Rev 1.1           | CSHW_000040 |  |

| 8                                | LIN-Adapter Board                                   | C&S             | Rev 1.1           | CSHW_000099 |  |

| 9                                | LIN Stimuli Board                                   | C&S             | Rev.1.2           | CSHW_000010 |  |

| 10                               | LIN IUT Board                                       | C&S             | Rev 2.1           | CSHW_000193 |  |

| LIN e                            | xt. Duty Cycle Test                                 |                 |                   |             |  |

| 11                               | Duty Cycle Board                                    | C&S             | Rev 1.0           | CSHW_000212 |  |

| Test                             | System Hardware                                     |                 |                   |             |  |

| 12                               | Power Supply                                        | Hameg           | HM 8142           | CS140142    |  |

| 13                               | Power Supply                                        | Hameg           | HM 8142           | 700013      |  |

| 14                               | Power Supply                                        | Hameg           | HM 8142           | CS140220    |  |

| 15                               | Oscilloscope                                        | Agilent         | 54622D            | 700035      |  |

| 16                               | Oscilloscope                                        | Agilent         | MSO8104A          | 700090      |  |

| 17                               | Function/ Waveform generator                        | Hewlett Packard | 33120A            | 700007      |  |

| 18                               | Function/ Waveform generator                        | Hewlett Packard | 33120A            | 700043      |  |

| 19                               | 19 Data Acquisition /Switch Unit Agilent 34970A CS1 |                 | CS140147          |             |  |

| 20 Data Acquisition /Switch Unit |                                                     | Agilent         | 34970A            | CS140146    |  |

| 21                               | 20-Channel-Multiplexer Module (2/4 Wire)            | Agilent         | 34901A            | 700096      |  |

| 22                               | 20-Channel-Multiplexer Module (2/4 Wire)            | Agilent         | 34901A            | 700095      |  |

| 23                               | 20-Channel Actuator Module                          | Agilent         | 34903A            | CS140145    |  |

| Software                         |                                                     |                 |                   |             |  |

| 24                               | LIN_PL_Supervisor                                   | C&S             | 1.0.5.0, Build 5  |             |  |

|                                  |                                                     |                 |                   |             |  |

- 10 of 51 -

# 4 Technical Correspondence

| Name  | Lothar Kukla        |

|-------|---------------------|

| Phone | +49 5331 90555 400  |

| Fax   | +49 5331 90555 110  |

| Email | L.Kukla@cs-group.de |

## 5 Test List

## 5.1 Dynamic Tests

Following test case numeration relates on the corresponding test specification

| No.     | Description                                                   |                                                      |                              | Result                                                                           | Comment          |

|---------|---------------------------------------------------------------|------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------|------------------|

| 2.1     | Operating Voltage Range                                       |                                                      |                              |                                                                                  |                  |

| 2.1.1   | Voltage Ramp V <sub>SUP</sub> = [7V18V], 0.1V/s [up]          |                                                      | Pass                         | RX shows the 10kHz Signal,<br>The maximum deviation is less or<br>equal than 10% |                  |

| 2.1.2   | Voltage Ramp V <sub>SUP</sub> = [18V7V], 0.1V/s [down]        |                                                      | Pass                         | RX shows the 10kHz Signal,<br>The maximum deviation is less or<br>equal 10%      |                  |

| 2.2     | Threshold V                                                   | oltages                                              |                              |                                                                                  |                  |

| 2.2.1   | IUT as Recei                                                  | iver: V <sub>SUP</sub> @ V <sub>BUS_DOM</sub> (down) |                              |                                                                                  |                  |

| 2.2.1.1 | V <sub>SUP</sub> = 7V                                         | Signal Range [18V4.2V]                               | Expected RX Signal recessive | Pass                                                                             | RX is recessive. |

|         | $V_{SUP} = 7V$                                                | Signal Range [2.8V1.05V]                             | Expected RX Signal dominant  | Pass                                                                             | RX is dominant.  |

| 2.2.1.2 | V <sub>SUP</sub> = 13V                                        | Signal Range [18V7.8V]                               | Expected RX Signal recessive | Pass                                                                             | RX is recessive. |

|         | V <sub>SUP</sub> = 13V                                        | Signal Range [5.2V2.1V]                              | Expected RX Signal dominant  | Pass                                                                             | RX is dominant.  |

| 2.2.1.3 | V <sub>SUP</sub> = 18V                                        | Signal Range [20.7V10.8V]                            | Expected RX Signal recessive | Pass                                                                             | RX is recessive. |

|         | V <sub>SUP</sub> = 18V                                        | Signal Range [7.2V2.7V]                              | Expected RX Signal dominant  | Pass                                                                             | RX is dominant.  |

| 2.2.2   | IUT as Receiver: V <sub>SUP</sub> @ V <sub>BUS_REC</sub> (up) |                                                      |                              |                                                                                  |                  |

| 2.2.2.1 | V <sub>SUP</sub> = 7V                                         | Signal Range [-1.05V2.8V]                            | Expected RX Signal dominant  | Pass                                                                             | RX is dominant.  |

|         | V <sub>SUP</sub> = 7V                                         | Signal Range [4.2V18V]                               | Expected RX Signal recessive | Pass                                                                             | RX is recessive. |

| 2.2.2.2 | V <sub>SUP</sub> = 13V                                        | Signal Range [-2.1V5.2V]                             | Expected RX Signal dominant  | Pass                                                                             | RX is dominant.  |

|         | V <sub>SUP</sub> = 13V                                        | Signal Range [7.8V18V]                               | Expected RX Signal recessive | Pass                                                                             | RX is recessive. |

| No.     | Description                                                                                              | Result         | Comment                                                                                                                        |

|---------|----------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| 2.2.2.3 | V <sub>SUP</sub> = 18V Signal Range [-2.7V7.2V] Expected RX Signal dominant                              | Pass           | RX is dominant.                                                                                                                |

|         | V <sub>SUP</sub> = 18V Signal Range [10.8V20.7V] Expected RX Signal recessive                            | Pass           | RX is recessive.                                                                                                               |

| 2.2.3   | IUT as Receiver: V <sub>SUP</sub> @ V <sub>BUS</sub>                                                     |                |                                                                                                                                |

| 2.2.3.1 | V <sub>SUP</sub> = 7V Signal Range [-1.05V8.05V] up [8.05V1.05V] down                                    | Pass           | $V_{\text{BUS\_CNT}}$ is in range of [0.4750.525]* $V_{\text{SUP}}$ , $V_{\text{HYS}}$ is less than 0.175* $V_{\text{SUP}}$ .  |

| 2.2.3.2 | V <sub>SUP</sub> = 14V Signal Range [-2.1V16.1V] up [16.1V2.1V] down                                     | Pass           | $V_{\text{BUS\_CNT}}$ is in range of $[0.4750.525]^*V_{\text{SUP}},$ $V_{\text{HYS}}$ is less than $0.175^*$ $V_{\text{SUP}}.$ |

| 2.2.3.3 | V <sub>SUP</sub> = 18V Signal Range [-2.7V20.7V] up [20.7V2.7V] down                                     | Pass           | $V_{\text{BUS\_CNT}}$ is in range of [0.4750.525]* $V_{\text{SUP}}$ , $V_{\text{HYS}}$ is less than 0.175* $V_{\text{SUP}}$ .  |

| 2.3     | Variation of V <sub>SUP_NON_OP</sub> ∈ [- 0.3V 7.0V ]; [18V 40V]                                         |                |                                                                                                                                |

| 2.3.1   | Master ECU $V_{BAT} = [-0.3V8V], [18V40V]$ 60 kΩ + diode to $V_{LIN} = 18 \text{ V}$                     | Not applicable | IUT as Transceiver                                                                                                             |

| 2.3.2   | Slave ECU $V_{BAT} = [-0.3V8V], [18V40V]$ 1.1k $\Omega$ + diode to $V_{LIN} = 18 \text{ V}$              | Not applicable | IUT as Transceiver                                                                                                             |

| 2.3.3   | Transceiver $V_{SUP} = [-0.3V7V], [18V40V]1.1 \text{ k}\Omega + \text{diode to } V_{LIN} = 18 \text{ V}$ | Pass           | No dominant state occurs,<br>the IUT is not destroyed,<br>the recessive voltage afterwards is<br>less or equal +/-5%           |

| 2.4     | I <sub>BUS</sub> Under Several Conditions                                                                |                |                                                                                                                                |

| 2.4.1   | I <sub>BUS_LIM</sub> @ Dominant State ( Driver On ); V <sub>IUT</sub> = 18V                              | Pass           | LIN shows the rectangular signal, the dominant state bus level is lower than th_dom=4.518V for Transceiver                     |

| 2.4.2   | $I_{BUS\_PAS\_dom}$ : IUT in Recessive State : $V_{IUT} = 12V$ ; $V_{BUS} = 0V$                          | Pass           | The maximum voltage drop is higher than -500mV.                                                                                |

| 2.4.3   | $I_{BUS\_PAS\_rec}$ : IUT in Recessive State: $V_{SUP}$ = 7V with Variation of $V_{BUS}$ $\in$ [8V 18V]  | Pass           | The maximum voltage drop is less or equal than 20mV.                                                                           |

| No.       | Description             |                                  |                        | Result | Comment                                                                                                            |

|-----------|-------------------------|----------------------------------|------------------------|--------|--------------------------------------------------------------------------------------------------------------------|

| 2.5       | Slope Contro            | ol                               |                        |        |                                                                                                                    |

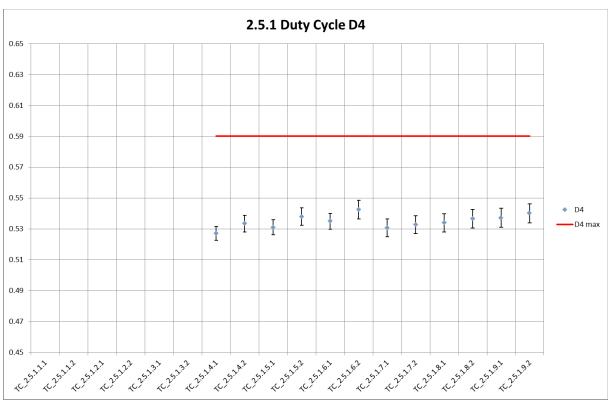

| 2.5.1     | Measuring th            | ne Duty Cycle @ 10.4 kBit/sec    | - IUT as Transmitter   |        |                                                                                                                    |

| 2.5.1.1.1 | V <sub>SUP</sub> = 7V   | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.1.2 | V <sub>SUP</sub> = 7V   | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.2.1 | V <sub>SUP</sub> = 7V   | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.2.2 | V <sub>SUP</sub> = 7V   | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.3.1 | V <sub>SUP</sub> = 7V   | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.3.2 | V <sub>SUP</sub> = 7V   | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417.                                                         |

| 2.5.1.4.1 | V <sub>SUP</sub> = 7.6V | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.4.2 | V <sub>SUP</sub> = 7.6V | Bus Load = 1nF, 1k $\Omega$      | V <sub>PS2</sub> =7.2V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.5.1 | V <sub>SUP</sub> = 7.6V | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.5.2 | V <sub>SUP</sub> = 7.6V | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =7.2V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| No.       | Description             |                                  |                         | Result | Comment                                                                                                            |

|-----------|-------------------------|----------------------------------|-------------------------|--------|--------------------------------------------------------------------------------------------------------------------|

| 2.5.1.6.1 | V <sub>SUP</sub> = 7.6V | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =6.6V  | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.6.2 | V <sub>SUP</sub> = 7.6V | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =7.2V  | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.7.1 | V <sub>SUP</sub> = 18V  | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.7.2 | V <sub>SUP</sub> = 18V  | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.8.1 | V <sub>SUP</sub> = 18V  | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.8.2 | V <sub>SUP</sub> = 18V  | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.9.1 | V <sub>SUP</sub> = 18V  | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| 2.5.1.9.2 | V <sub>SUP</sub> = 18V  | Bus Load = $10$ nF, $500\Omega$  | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D3 is greater or equal than 0.417, the measured duty cycle D4 is less or equal than 0.590. |

| No.       | Description             |                                  |                        | Result | Comment                                                                                                            |

|-----------|-------------------------|----------------------------------|------------------------|--------|--------------------------------------------------------------------------------------------------------------------|

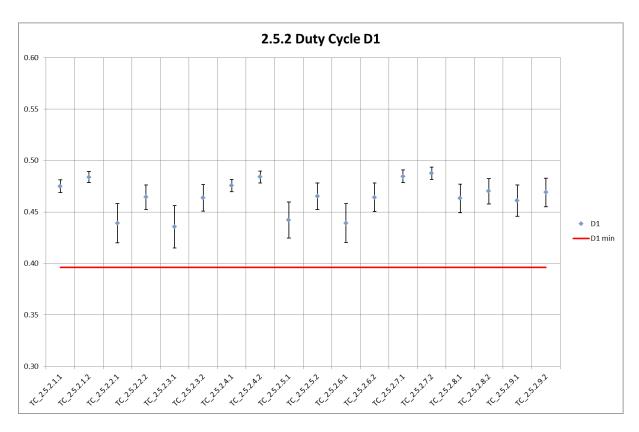

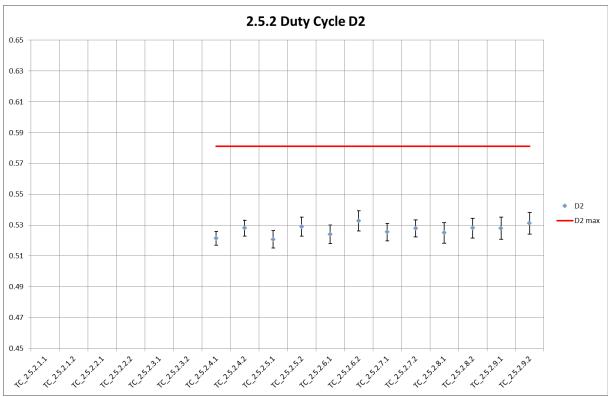

| 2.5.2     | Measuring th            | e Duty Cycle @ 20.0 kBit/sec     | - IUT as Transmitter   |        |                                                                                                                    |

| 2.5.2.1.1 | V <sub>SUP</sub> = 7V   | Bus Load = $1nF$ , $1k\Omega$    | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.1.2 | V <sub>SUP</sub> = 7V   | Bus Load = $1nF$ , $1k\Omega$    | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.2.1 | V <sub>SUP</sub> = 7V   | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.2.2 | V <sub>SUP</sub> = 7V   | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.3.1 | V <sub>SUP</sub> = 7V   | Bus Load = 10nF, $500\Omega$     | V <sub>PS2</sub> =6.0V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.3.2 | V <sub>SUP</sub> = 7V   | Bus Load = 10nF, $500\Omega$     | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D1 is greater or equal than 0.396.                                                         |

| 2.5.2.4.1 | V <sub>SUP</sub> = 7.6V | Bus Load = $1nF$ , $1k\Omega$    | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.4.2 | V <sub>SUP</sub> = 7.6V | Bus Load = 1nF, 1k $\Omega$      | V <sub>PS2</sub> =7.2V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.5.1 | V <sub>SUP</sub> = 7.6V | Bus Load = 6.8nF, 660Ω           | V <sub>PS2</sub> =6.6V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.5.2 | V <sub>SUP</sub> = 7.6V | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =7.2V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| No.       | Description             |                                  |                         | Result | Comment                                                                                                            |

|-----------|-------------------------|----------------------------------|-------------------------|--------|--------------------------------------------------------------------------------------------------------------------|

| 2.5.2.6.1 | V <sub>SUP</sub> = 7.6V | Bus Load = 10nF, 500Ω            | V <sub>PS2</sub> =6.6V  | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.6.2 | V <sub>SUP</sub> = 7.6V | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =7.2V  | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.7.1 | V <sub>SUP</sub> = 18V  | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.7.2 | V <sub>SUP</sub> = 18V  | Bus Load = 1nF, $1k\Omega$       | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.8.1 | V <sub>SUP</sub> = 18V  | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.8.2 | V <sub>SUP</sub> = 18V  | Bus Load = $6.8$ nF, $660\Omega$ | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.9.1 | V <sub>SUP</sub> = 18V  | Bus Load = 10nF, 500Ω            | V <sub>PS2</sub> =17.0V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| 2.5.2.9.2 | V <sub>SUP</sub> = 18V  | Bus Load = $10nF$ , $500\Omega$  | V <sub>PS2</sub> =17.6V | Pass   | The measured duty cycle D1 must be greater or equal than 0.396, the measured duty cycle D2 is less or equal 0.581. |

| No.     | Description                                                            | Result | Comment                                                                                                                                           |

|---------|------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.6     | Propagation Delay                                                      |        |                                                                                                                                                   |

| 2.6.1   | Propagation Delay of the Receiver                                      |        |                                                                                                                                                   |

| 2.6.1.1 | $V_{SUP} = 7V$ RX Load = 20pF                                          | Pass   | $t_{rx\_pd}$ is less than 6µs, $t_{rx\_sym}$ is in range +/- 2µs.                                                                                 |

| 2.6.1.2 | $V_{SUP} = 14V$ RX Load = 20pF                                         | Pass   | $t_{rx\_pd}$ is less than 6µs, $t_{rx\_sym}$ is in range +/- 2µs.                                                                                 |

| 2.6.1.3 | $V_{SUP} = 18V$ RX Load = 20pF                                         | Pass   | $t_{rx\_pd}$ is less than 6µs, $t_{rx\_sym}$ is in range +/- 2µs.                                                                                 |

| 2.7     | GND / VBAT Shift Test – Dynamic                                        |        |                                                                                                                                                   |

| 2.7.1   | GND Shift Test – Dynamic – IUT as Transceiver (Master)                 | Pass   | The duty cycle of RX is in range D1 – 2µs D2 + 2µs.                                                                                               |

| 2.7.2   | GND Shift Test – Dynamic – IUT as Transceiver (Slave)                  | Pass   | The duty cycle of RX is in range D1 – 2µs D2 + 2µs.                                                                                               |

| 2.7.3   | VBAT Shift Test – Dynamic – IUT as Transceiver (Master)                | Pass   | The duty cycle of RX is in range D1 – 2μs D2 + 2μs.                                                                                               |

| 2.7.4   | VBAT Shift Test – Dynamic – IUT as Transceiver (Slave)                 | Pass   | The duty cycle of RX is in range D1 – 2µs D2 + 2µs.                                                                                               |

| 2.8     | Failure                                                                |        |                                                                                                                                                   |

| 2.8.1   | Loss of Battery                                                        | Pass   | No parasitic current path is formed between the bus line and the DUT.                                                                             |

| 2.8.2   | Loss of GND                                                            | Pass   | No parasitic current path is formed between the bus line and the DUT.                                                                             |

| 2.9     | Verifying internal capacitance and dynamic interference – IUT as Slave |        |                                                                                                                                                   |

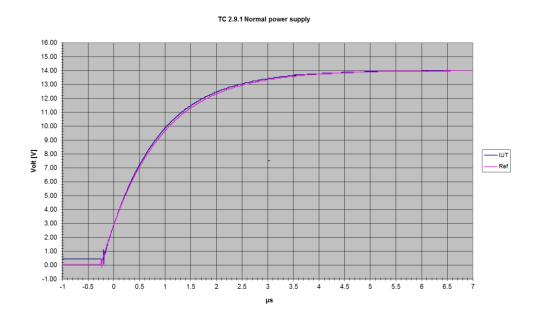

| 2.9.1   | Normal power supply                                                    | Pass   | C <sub>SLAVE</sub> is less or equal than 250pF:<br>T <sub>INT</sub> ≤ T <sub>REF</sub><br>The IUT does not interfere with the<br>dynamic stimulus |

| No.   | Description                  | Result | Comment                                                                                |

|-------|------------------------------|--------|----------------------------------------------------------------------------------------|

| 202   | ILIT loop of CNID            | Dana   | C <sub>SLAVE</sub> is less or equal than 250pF:<br>T <sub>INT</sub> ≤ T <sub>REF</sub> |

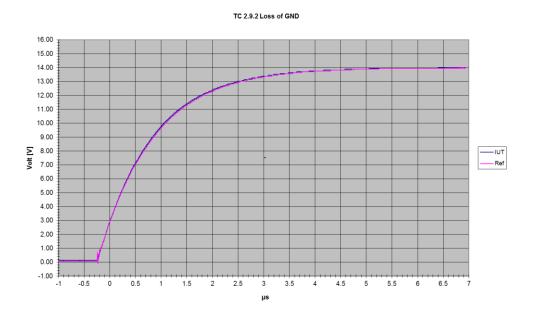

| 2.9.2 | IUT loss of GND              | Pass   | The IUT does not interfere with the dynamic stimulus                                   |

| 0.00  | IUT loss of V <sub>SUP</sub> | D      | C <sub>SLAVE</sub> is less or equal than 250pF:<br>T <sub>INT</sub> ≤ T <sub>REF</sub> |

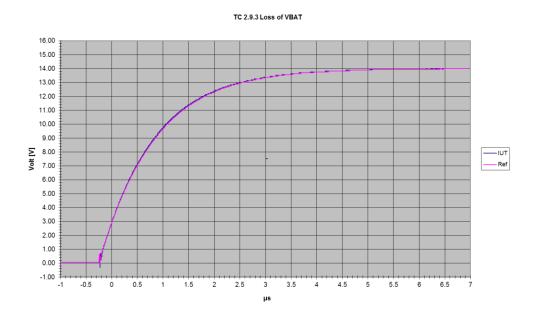

| 2.9.2 |                              | Pass   | The IUT does not interfere with the dynamic stimulus                                   |

#### 5.2 Static Tests

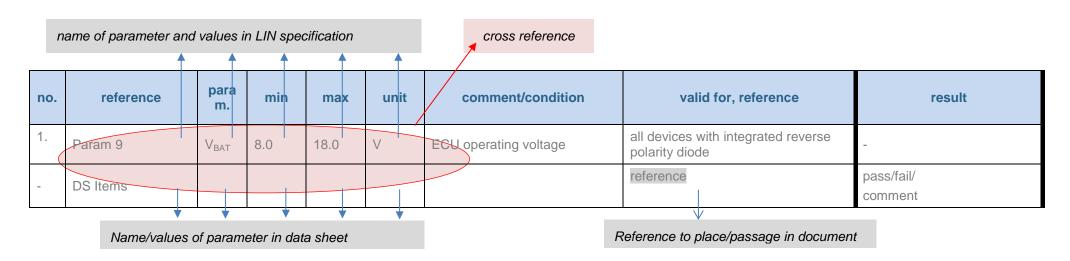

The motivation of static test cases is to check the availability and the boundaries in the data sheet of the IUT.

For all integrated circuits every related parameter in Table 4.1 must be part of the data sheet and fulfil the specified boundaries in terms of physical worst case condition. Data sheet parameter names may deviate from the names in Table 4.1, but in this case a cross-reference list (data sheet versus Table 4.1) shall be provided for this test. Parameter conditions may deviate from the conditions in Table 4.1, if the data sheet conditions are according to the physical worst case context in Table 4.1 at least.

If one parameter does not pass this test, the result of the whole conformance test is failed.

Reference LIN Physical Layer Spec Revision 2.2 December 31, 2010, section Line Driver/Receiver, 6.5.4 ELECTRICAL DC PA-RAMETERS, table 6.6 to 6.11

Used data sheets:

MC9S12ZVL\_Rev2.00\_Draft\_G.pdf (reference indicated with 'Ref 1')

Notes to the following table:

| no. | reference | param.                   | min  | max  | unit | comment/condition                                                                                                                       | valid for, reference                                   | result                   |

|-----|-----------|--------------------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------|

| 1.  | Param 9   | $V_{BAT}$                | 8.0  | 18.0 | V    | ECU operating voltage                                                                                                                   | all devices with integrated reverse polarity diode     | -                        |

| -   |           | -                        | -    | -    | 1    | -                                                                                                                                       | -                                                      | Not applicable, no diode |

| 2.  | Param 10  | $V_{	ext{SUP}}$          | 7.0  | 18.0 | V    | Supply voltage range                                                                                                                    | all devices without integrated reverse polarity diode  | -                        |

| -   |           | VLINSUP_LIN              | 5.5  | 18   | V    | VLINSUP operating range                                                                                                                 | Ref1 Page 710 Table D-2 Num 1                          | Pass                     |

| 3.  | Param 11  | $V_{SUP\_NON\_OP}$       | -0.3 | 40.0 | V    | voltage range within which the device is not destroyed                                                                                  | all devices                                            | -                        |

| -   |           | Vsup                     | -0.3 | 42   | V    | Voltage regulator and LINPHY supply voltage                                                                                             | Ref1 Page 684 Table A-3 Num 1                          | Pass                     |

| 4.  | Param 12  | I <sub>BUS_LIM</sub>     | 40   | 200  | mA   | Current Limitation for Driver dominant state driver on $V_{BUS} = V_{BAT\_max}$                                                         | all devices with integrated LIN transmitter            | -                        |

| -   |           | ILIN_LIM                 | 40   | 200  | mA   | Current limitation into the LIN pin in dominant state <sup>4</sup> VLIN = VLINSUP_LIN_MAX                                               | Ref1 Page 710 Table D-2 Num 2                          | Pass                     |

| 5.  | Param 13  | I <sub>BUS_PAS_dom</sub> | -1   |      | mA   | Input Leakage Current at the Receiver incl.  Slave Pull-Up Resistor as specified in Table 6.7 driver off $V_{BUS} = 0V$ $V_{BAT} = 12V$ | all devices with integrated slave pull-<br>up resistor | -                        |

| -   |           | ILIN_PAS_dom             | -1   |      | mA   | Input leakage current in dominant state, driver off, internal pull-up on VLIN = 0V, VLINSUP = 12V                                       | Ref1 Page 710 Table D-2 Num 3                          | Pass                     |

| no. | reference | param.                   | min | max | unit | comment/condition                                                                                                                                                                                             | valid for, reference          | result |

|-----|-----------|--------------------------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|

| 6.  | Param 14  | I <sub>BUS_PAS_rec</sub> |     | 20  | μA   | driver off<br>8V <v<sub>BAT&lt;18V<br/>8V<v<sub>BUS&lt;18V<br/>V<sub>BUS</sub> &gt; V<sub>BAT</sub></v<sub></v<sub>                                                                                           | all devices                   | -      |

| -   |           | ILIN_PAS_rec             |     | 20  | μA   | Input leakage current in recessive state, driver off 5.5V <vlinsup<18v, 5.5v<vlin<18v,="" vlin=""> VLINSUP</vlinsup<18v,>                                                                                     | Ref1 Page 710 Table D-2 Num 4 | Pass   |

| 7.  | Param 15  | I <sub>BUS_NO_GND</sub>  | -1  | 1   | mA   | Control unit disconnected from ground GND <sub>Device</sub> = V <sub>SUP</sub> 0V <v<sub>BUS&lt;18V V<sub>BAT</sub> = 12V Loss of local ground must not affect communication in the residual network.</v<sub> | all devices                   | -      |

| -   |           | ILIN_NO_GND              | -1  | 1   | mA   | Input leakage current when ground disconnected GNDDevice = VLINSUP, 0V <vlin<18v, vlinsup="12V&lt;/td"><td>Ref1 Page 710 Table D-2 Num 5</td><td>Pass</td></vlin<18v,>                                        | Ref1 Page 710 Table D-2 Num 5 | Pass   |

| 8.  | Param 16  | I <sub>BUS_NO_BAT</sub>  |     | 100 | μΑ   | V <sub>BAT</sub> disconnected V <sub>SUP_Device</sub> = GND 0 <v<sub>BUS&lt;18V Node has to sustain the current that can flow under this condition. Bus must remain operational under this condition.</v<sub> | all devices                   | -      |

| -   |           | ILIN_NO_BAT              |     | 30  | μΑ   | Input leakage current when battery disconnected  VLINSUP = GNDDevice, 0 <vlin<18v< td=""><td>Ref1 Page 710 Table D-2 Num 6</td><td>Pass</td></vlin<18v<>                                                      | Ref1 Page 710 Table D-2 Num 6 | Pass   |

| no. | reference | param.               | min   | max   | unit             | comment/condition                                                                                                                                                                                                              | valid for, reference                                             | result |

|-----|-----------|----------------------|-------|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------|

| 9.  | Param 17  | $V_{BUSdom}$         |       | 0.4   | V <sub>SUP</sub> | receiver dominant state                                                                                                                                                                                                        | all devices with integrated LIN receiver                         | -      |

| -   |           | VLINdom              |       | 0.4   | VLINSUP          | Receiver dominant state                                                                                                                                                                                                        | Ref1 Page 710 Table D-2 Num 7                                    | Pass   |

| 10. | Param 18  | $V_{BUSrec}$         | 0.6   |       | V <sub>SUP</sub> | receiver recessive state                                                                                                                                                                                                       | all devices with integrated LIN receiver                         | -      |

| -   |           | VLINrec              | 0.6   |       | VLINSUP          | Receiver recessive state                                                                                                                                                                                                       | Ref1 Page 710 Table D-2 Num 8                                    | Pass   |

| 11. | Param 19  | V <sub>BUS_CNT</sub> | 0.475 | 0.525 | V <sub>SUP</sub> | $V_{BUS\_CNT} = (V_{th\_dom} + V_{th\_rec})/2$                                                                                                                                                                                 | all devices with integrated LIN receiver                         | -      |

| -   |           | VLIN_CNT             | 0.475 | 0.525 | VLINSUP          | VLIN_CNT =(Vth_dom+ Vth_rec)/2                                                                                                                                                                                                 | Ref1 Page 710 Table D-2 Num 9                                    | Pass   |

| 12. | Param 20  | V <sub>HYS</sub>     |       | 0.175 | V <sub>SUP</sub> | $V_{HYS} = V_{th\_rec} - V_{th\_dom}$                                                                                                                                                                                          | all devices with integrated LIN receiver                         | -      |

| -   |           | VHYS                 |       | 0.175 | Vs               | VHYS = Vth_rec -Vth_dom                                                                                                                                                                                                        | Ref1 Page 710 Table D-2 Num 10                                   | Pass   |

| 13. | Param 27  | D1                   | 0.396 |       |                  | $\begin{split} T_{HRec(max)} &= 0.744 \text{ x V}_{SUP}; \\ T_{HDom(max)} &= 0.581 \text{ x V}_{SUP}; \\ V_{SUP} &= 7.0V18V; \ t_{Bit} = 50\mu s; \\ D1 &= t_{Bus\_rec(min)} / (2 \text{ x t}_{Bit}) \end{split}$              | all devices with integrated LIN transmitter D1 valid for 20kBaud | -      |

| -   |           | D1                   | 0.396 |       |                  | Duty cycle 1 THRec(max) = 0.744 x VLINSUP THDom(max) = 0.581 x VLINSUP VLINSUP = 5.5V18V tBit = 50us D1 = tBus_rec(min) / (2 x tBit)                                                                                           | Ref1 Page 711 Table D-3 Num 7                                    | Pass   |

| 14. | Param 28  | D2                   |       | 0.581 |                  | $\begin{split} T_{HRec(min)} &= 0.422 \text{ x V}_{SUP}; \\ T_{Hdom(min)} &= 0.284 \text{ x V}_{SUP}; \\ V_{SUP} &= 7.6 V \dots 18 V; \ t_{Bit} = 50 \mu s; \\ D2 &= t_{Bus\_rec(max)} / \ (2 \text{ x } t_{Bit}) \end{split}$ | all devices with integrated LIN transmitter D2 valid for 20kBaud | -      |

| no. | reference | param.             | min   | max   | unit | comment/condition                                                                                                                                                                                                                                     | valid for, reference                                                | result |

|-----|-----------|--------------------|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------|

| -   |           | D2                 |       | 0.581 |      | Duty cycle 2 THRec(min) = 0.422 x VLINSUP THDom(min) = 0.284 x VLINSUP VLINSUP = 5.5V18V tBit = 50us D2 = tBus_rec(max) / (2 x tBit)                                                                                                                  | Ref1 Page 711 Table D-3 Num 8                                       | Pass   |

| 15. | Param 29  | D3                 | 0.417 |       |      | $\begin{split} T_{HRec(max)} &= 0.778 \text{ x V}_{SUP}; \\ T_{HDom(max)} &= 0.616 \text{ x V}_{SUP}; \\ V_{SUP} &= 7.0V18V; \ t_{Bit} = 96\mu s; \\ D3 &= t_{Bus\_rec(min)} / (2 \text{ x t}_{Bit}) \end{split}$                                     | all devices with integrated LIN transmitter D3 valid for 10.4 kBaud | -      |

| -   |           | D3                 | 0.417 |       |      | Duty cycle 3 THRec(max) = 0.778 x VLINSUP THDom(max) = 0.616 x VLINSUP VLINSUP = 5.5V18V tBit = 96us D3 = tBus_rec(min) / (2 x tBit)                                                                                                                  | Ref1 Page 712 Table D-3 Num 11                                      | Pass   |

| 16. | Param 30  | D4                 |       | 0.590 |      | $\begin{split} T_{HRec(min)} &= 0.389 \text{ x V}_{SUP}; \\ T_{HDom(min)} &= 0.251 \text{ x V}_{SUP}; \\ V_{SUP} &= 7.6 \text{V}18 \text{V}; \ t_{Bit} = 96 \mu \text{s}; \\ D4 &= t_{Bus\_rec(max)} / \left(2 \text{ x } t_{Bit}\right) \end{split}$ | all devices with integrated LIN transmitter D4 valid for 10.4 kBaud | -      |

| -   |           | D4                 |       | 0.590 |      | Duty cycle 4 THRec(min) = 0.389 x VLINSUP THDom(min) = 0.251 x VLINSUP VLINSUP = 5.5V18V tBit = 96us D4 = tBus_rec(max) / (2 x tBit)                                                                                                                  | Ref1 Page 712 Table D-3 Num 12                                      | Pass   |

| 17. | Param 31  | t <sub>rx_pd</sub> |       | 6     | μs   | propagation delay of receiver                                                                                                                                                                                                                         | all devices with integrated LIN receiver                            | -      |

| -   |           | trx_pd             |       | 6     | μs   | Propagation delay of receiver                                                                                                                                                                                                                         | Ref1 Page 711 Table D-3 Num 3                                       | Pass   |

| no. | reference                                     | param.                          | min         | max         | unit       | comment/condition                                                                                                                | valid for, reference                                                                   | result                      |

|-----|-----------------------------------------------|---------------------------------|-------------|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------|

| 18. | Param 32                                      | t <sub>rx_sym</sub>             | -2          | 2           | μs         | symmetry of receiver propagation delay rising edge w.r.t. falling edge                                                           | all devices with integrated LIN receiver                                               | -                           |

| -   |                                               | trx_sym                         | -2          | 2           | μs         | Symmetry of receiver propagation delay rising edge w.r.t. falling edge                                                           | Ref1 Page 711 Table D-3 Num 4                                                          | Pass                        |

| 19. | Param 26                                      | $R_{SLAVE}$                     | 20          | 60          | kΩ         |                                                                                                                                  | all devices with integrated slave pull-<br>up resistor                                 | -                           |

| -   |                                               | Rslave                          | 27          | 40          | kΩ         | Internal pull-up (slave)                                                                                                         | Ref1 Page 711 Table D-2 Num 13                                                         | Pass                        |

| 20. | Param 25                                      | R <sub>MASTER</sub>             | 900         | 1100        | Ω          | The serial diode is mandatory. Only for valid for Transceiver with integrated Master pull up resistor                            | all devices with integrated master pull-up resistor                                    | -                           |

| -   |                                               | -                               | -           | -           | -          | -                                                                                                                                | -                                                                                      | Not applicable<br>No Master |

| 21. | Param 37                                      | C <sub>SLAVE</sub>              |             | 250         | pF         | Capacitance of slave node                                                                                                        | all LIN slave devices                                                                  | -                           |

| -   |                                               | Cslave                          | 220         | 250         | pF         | Maximum capacitance allowed on slave node including external components                                                          | Ref1 Page 710 Table D-2 Num 11                                                         | Pass                        |

| 22. | LIN 2.2<br>Specificatio<br>n Chapter<br>6.5.7 | LIN device<br>states<br>changes | -           | -           | -          | All LIN device state changes on conditional events (e.g. temperature shut-down) shall be specified in the LIN device data sheet. | all devices                                                                            | -                           |

| -   |                                               | tOCLIM<br>tDTLIM                | 15<br>16388 | 16<br>16389 | μs<br>tirc | Automatic transmitter shutdown in case of an over-current or TxD-dominant timeout                                                | Ref1 Page 32 1.4.1.8<br>Ref1 Page 711 Table D-3 Num 6<br>Ref1 Page 711 Table D-3 Num 2 | Pass                        |

| no. | reference | param.                                     | min | max | unit | comment/condition                                                                                                                                                                                       | valid for, reference            | result |

|-----|-----------|--------------------------------------------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------|

| 23. |           | LIN<br>transceiver<br>input<br>capacitance | -   | -   |      | A maximum LIN transceiver input capacitance shall be specified in the LIN device data sheet. Please consider the data sheet limits (e.g. voltage, temperature). The value should be as low as possible. | All devices                     | -      |

| -   |           | CLIN                                       |     | 45  | pF   | Capacitance of the LIN pin,<br>Recessive state                                                                                                                                                          | Ref1 Page 711 Table D-2 Num 12b | Pass   |

## 6 Test Protocol Dynamic Tests

Following test case numeration and cross references relates on the corresponding test specification.

## TC 2.1 Operating Voltage Range

This test shall ensure the correct operation in the valid supply voltage ranges, by correct reception of dominant bits. The IUT is therefore supplied with an increasing / decreasing voltage ramp.

#### TC 2.1.1 Voltage Ramp [7.0V...18V], 0.1V/s [up]

| Comment                                                                                                  | Test Result |

|----------------------------------------------------------------------------------------------------------|-------------|

| The RX pin of the IUT shows the 10kHz signal with a maximum deviation of 10% (time, voltage) is allowed. | Pass        |

#### TC 2.1.2 Voltage Ramp [18V...7.0V], 0.1V/s [down]

| Comment                                                                                                  | Test Result |

|----------------------------------------------------------------------------------------------------------|-------------|

| The RX pin of the IUT shows the 10kHz signal with a maximum deviation of 10% (time, voltage) is allowed. | Pass        |

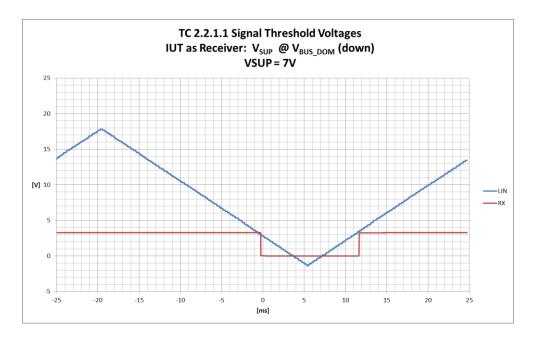

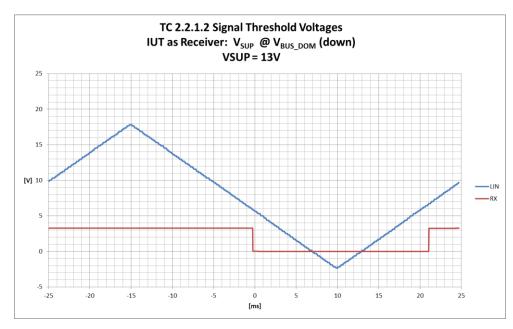

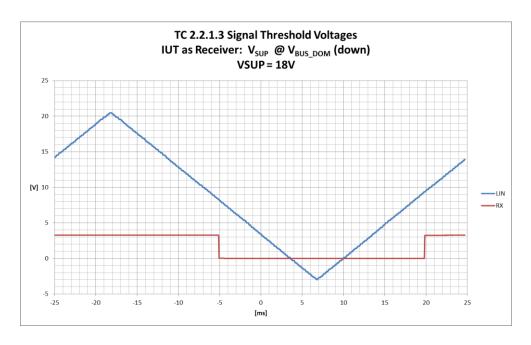

#### TC 2.2 Threshold Voltages

This group of tests checks whether the receiver threshold voltage of the IUT are implemented correctly within the entire specified operating supply voltage range. The LIN Bus voltage is driven with a voltage ramp checking the entire dominant and recessive signal area with respect to the applied supply voltage. In TC 2.2.1 and 2.2.2 the signal has to stay continuously on recessive or dominant level depending on the test case. In TC 2.2.3 the RX output transition is detected.

TC 2.2.1 IUT as Receiver: V<sub>SUP</sub> @ V<sub>BUS DOM</sub> (down)

TC 2.2.1.1  $V_{SUP} = 7V$  Signal Range [18V...4.2V], Expected RX Signal recessive  $V_{SUP} = 7V$  Signal Range [2.8V...-1.05V], Expected RX Signal dominant

TC 2.2.1.2  $V_{SUP} = 13V$ , Signal Range [18V...7.8V], Expected RX Signal recessive  $V_{SUP} = 13V$ , Signal Range [5.2 V...-2.1V], Expected RX Signal dominant

TC 2.2.1.3  $V_{SUP} = 18V$ , Signal Range [20.7 V...10.8V], Expected RX Signal recessive  $V_{SUP} = 18V$ , Signal Range [7.2 V...-2.7V], Expected RX Signal dominant

| # test  | V <sub>SUP</sub> | Signal Range | Expected RX Signal | Measured<br>RX Signal |

|---------|------------------|--------------|--------------------|-----------------------|

| 2.2.1.1 | 7V               | [18V4.2V]    | recessive          | recessive             |

|         |                  | [2.8V1.05V]  | dominant           | dominant              |

| 2.2.1.2 | 13V              | [18V7.8V]    | recessive          | recessive             |

|         |                  | [5.22.1V]    | dominant           | dominant              |

| 2.2.1.3 | 18V              | [20.7V10.8V] | recessive          | recessive             |

| 2.2.1.3 |                  | [7.2V2.7V]   | dominant           | dominant              |

| Comment                                                               | Test Result |

|-----------------------------------------------------------------------|-------------|

| The IUT must generate a dominant or recessive value on RX as defined. | Pass        |

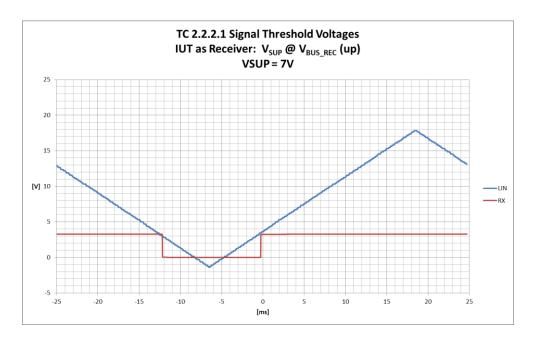

#### TC 2.2.2 IUT as Receiver: V<sub>SUP</sub> @ V<sub>BUS\_REC</sub> (up)

TC 2.2.2.1  $V_{SUP} = 7V$ , Signal Range [-1.05V...2.8V], Expected RX Signal dominant  $V_{SUP} = 7V$ , Signal Range [4.2V...18V], Expected RX Signal recessive

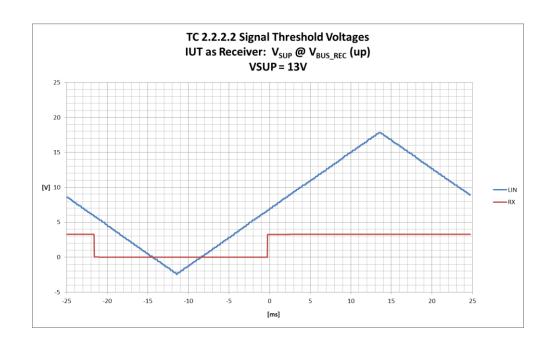

TC 2.2.2.2  $V_{SUP} = 13V$ , Signal Range [-2.1V...5.2V], Expected RX Signal dominant  $V_{SUP} = 13V$ , Signal Range [7.8V...18V], Expected RX Signal recessive

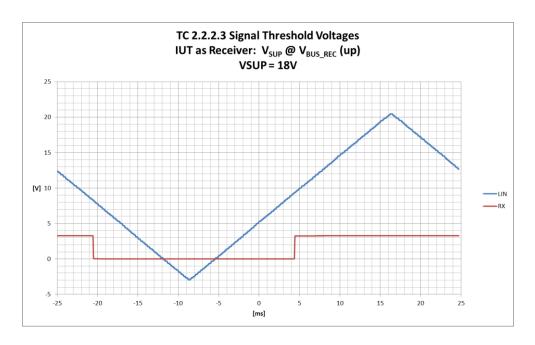

TC 2.2.2.3  $V_{SUP} = 18V$ , Signal Range [-2.7V...7.2V], Expected RX Signal dominant  $V_{SUP} = 18V$ , Signal Range [10.8V...20.7V], Expected RX Signal recessive

| # test  | V <sub>SUP</sub> | Signal Range | Expected RX Signal | Measured<br>RX Signal |

|---------|------------------|--------------|--------------------|-----------------------|

| 2.2.2.1 | 7V               | [-1.05V2.8V] | dominant           | dominant              |

|         |                  | [4.2V18V]    | recessive          | recessive             |

| 2.2.2.2 | 13V              | [-2.1V5.2V]  | dominant           | dominant              |

|         |                  | [7.818V]     | recessive          | recessive             |

| 2.2.2.3 | 18V              | [-2.7V7.2V]  | dominant           | dominant              |

| 2.2.2.3 |                  | [10.8V20.7V] | recessive          | recessive             |

| Comment                                                               | Test Result |

|-----------------------------------------------------------------------|-------------|

| The IUT must generate a dominant or recessive value on RX as defined. | Pass        |

#### TC 2.2.3 IUT as Receiver: VSUP @ V<sub>BUS</sub>

This test shall verify the symmetry of the receiver thresholds. For this purpose a voltage ramp on  $V_{\text{BUS}}$  shows the required threshold values.

TC 2.2.3.1  $V_{SUP} = 7V$ , Signal Range [-1.05V...8.05V] up [8.05V...-1.05V] down

| Vsup      | 7 V     |

|-----------|---------|

| V_th_dom  | 3.250 V |

| V_th_rec  | 3.656 V |

| V_hys     | 0.406 V |

| V_bus_cnt | 3.453 V |

| Comment                                                      | Test Result |

|--------------------------------------------------------------|-------------|

| The RX output transition must meet the following conditions: |             |

| VBUS_CNT = (Vth_dom+Vth_rec)/2 in range of [0.4750.525]*VSUP | Pass        |

| VHYS = Vth_rec - Vth_dom must be less than 0.175*VSUP        |             |

#### TC 2.2.3.2 $V_{SUP} = 14V$ , Signal Range [-2.1V...16.1V] up [16.1V...-2.1V] down

| Vsup      | 14V     |

|-----------|---------|

| V_th_dom  | 6.500 V |

| V_th_rec  | 7.375 V |

| V_hys     | 0.875 V |

| V_bus_cnt | 6.938 V |

| Comment                                                      | Test Result |

|--------------------------------------------------------------|-------------|

| The RX output transition must meet the following conditions: | _           |

| VBUS_CNT = (Vth_dom+Vth_rec)/2 in range of [0.4750.525]*VSUP | Pass        |

| VHYS = Vth_rec - Vth_dom must be less than 0.175*VSUP        |             |

#### TC 2.2.3.3 $V_{SUP} = 18V$ , Signal Range [-2.7V...20.7V] up [20.7V...-2.7V] down

| Vsup      | 18V     |

|-----------|---------|

| V_th_dom  | 8.375 V |

| V_th_rec  | 9.500 V |

| V_hys     | 1.125 V |

| V_bus_cnt | 8.938 V |

| Comment                                                                                                                    | Test Result |

|----------------------------------------------------------------------------------------------------------------------------|-------------|

| The RX output transition must meet the following conditions:  VBUS_CNT = (Vth_dom+Vth_rec)/2 in range of [0.4750.525]*VSUP | Pass        |

| VHYS = Vth_rec - Vth_dom must be less than 0.175*VSUP                                                                      |             |

#### TC 2.3 *Variation of V*<sub>SUP\_NON\_OP</sub> ∈ [- 0.3V...7V], [18V...40V]

Within this test it should be checked, whether the IUT influences the bus during under and over voltage conditions.

#### TC 2.3.3 **IUT** as Transceiver $1.1k\Omega$ + diode to $V_{LIN}$ = 18 V

20.00

TC 2.3.3 Variation of VSUP\_NON\_OP e [40V ... 18V, 8V ... -0.3V, -0.3V ... 8V, 18V ... 40V] Bus Load = 1.1k $\Omega$  + diode

| Comment                                                                                                                                                                                          | Test Result |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| No dominant state on LIN shall occur. The IUT must not be destroyed during the test. The afterwards recessive voltage shall have a maximum deviation of +/-5% from the before recessive voltage. | Pass        |

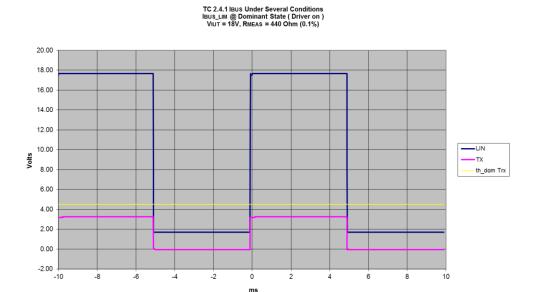

#### TC 2.4 I<sub>BUS</sub> Under Several Conditions

#### TC 2.4.1 I<sub>BUS LIM</sub> @ Dominant State (Driver On)

This test checks the drive capability of the output stage. A LIN driver has to pull the LIN bus below a certain voltage according to the LIN standard. The current limitation is measured indirectly.

| Comment                                                                                                                   | Test Result |

|---------------------------------------------------------------------------------------------------------------------------|-------------|

| LIN has to show the rectangular signal. The dominant state bus level has to be lower than th_dom= 4.518V for transceiver. | Pass        |

### TC 2.4.2 $I_{BUS\_PAS\_dom}$ : IUT in Recessive State: $V_{BUS} = 0V$

This test case is intended to test the input leakage current  $I_{\text{BUS\_PAS\_dom}}$  into a node during dominant state of the LIN bus.

| measured Voltage |

|------------------|

|------------------|

| Comment                                                        | Test Result |

|----------------------------------------------------------------|-------------|

| The maximum value of voltage drop shall be higher than -500mV. | Pass        |

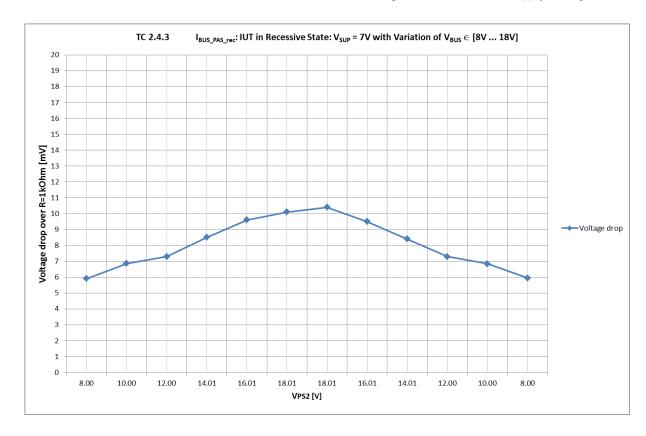

# TC 2.4.3 $I_{BUS\_PAS\_rec}$ : IUT in Recessive State: $V_{SUP}$ = 7V with Variation of $V_{BUS}$ $\in$ [8V ... 18V]

This test case is checking, whether there is a diode implementation within the termination path of the IUT. The reverse currents should be limited to  $I_{BUS\_PAS\_rec}$  (Max) from the LIN wire into the IUT even if  $V_{BUS}$  is higher than the IUT's supply voltage  $V_{IUT.}$

| Comment                                                        | Test Result |

|----------------------------------------------------------------|-------------|

| The maximum value of voltage drop shall be less or equal 20mV. | Pass        |

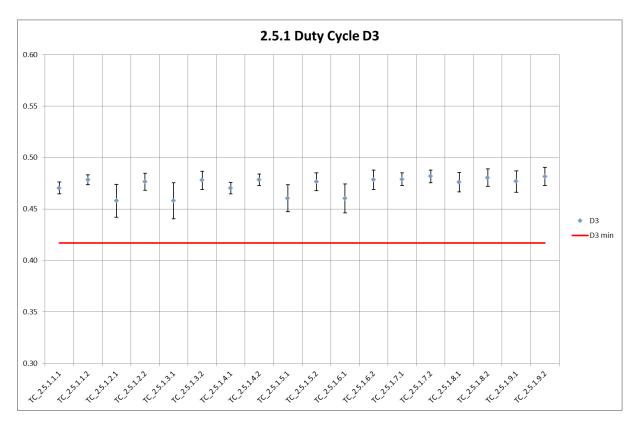

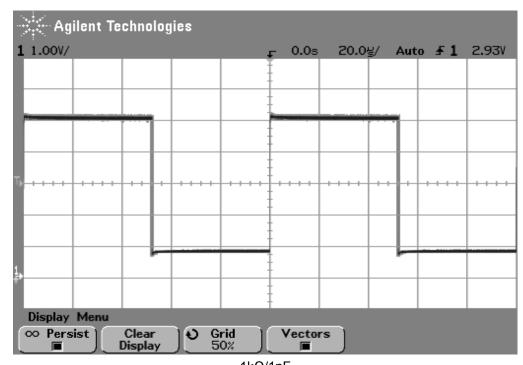

#### TC 2.5 Slope Control

Sense of this test is checking the slope control function of the driver stage.

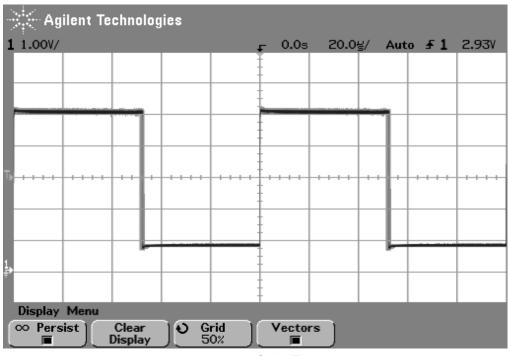

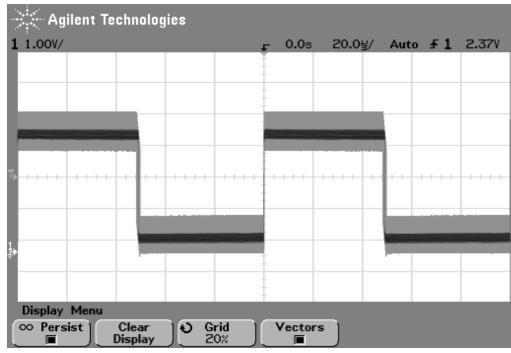

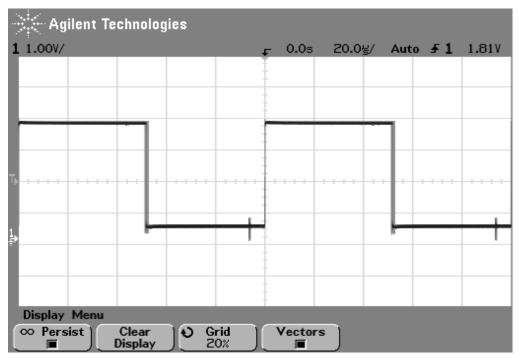

#### TC 2.5.1 Measuring the Duty Cycle @ 10.4 kBit/sec – IUT as Transmitter

| Test      | V <sub>SUP</sub> / V <sub>BAT</sub> | V <sub>PS2</sub> | Bus loads                   | Duty cycle         |                    |        |

|-----------|-------------------------------------|------------------|-----------------------------|--------------------|--------------------|--------|

| case #    | (PS 1)                              | (PS 2)           | (C; R)                      | D3 ±U <sup>*</sup> | D4 ±U <sup>*</sup> | Result |

| 2.5.1.1.1 | 7.0V / 8.0V                         | 6.0V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.470 ±0.006       | -                  | Pass   |

| 2.5.1.1.2 | 7.0V / 8.0V                         | 6.6V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.478 ±0.005       | -                  | Pass   |

| 2.5.1.2.1 | 7.0V / 8.0V                         | 6.0V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.458 ±0.016       | -                  | Pass   |

| 2.5.1.2.2 | 7.0V / 8.0V                         | 6.6V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.476 ±0.008       | _                  | Pass   |

| 2.5.1.3.1 | 7.0V / 8.0V                         | 6.0V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.458 ±0.018       | -                  | Pass   |

| 2.5.1.3.2 | 7.0V / 8.0V                         | 6.6V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.478 ±0.009       | -                  | Pass   |

| 2.5.1.4.1 | 7.6V / 8.6V                         | 6.6V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.470 ±0.006       | 0.527 ±0.005       | Pass   |

| 2.5.1.4.2 | 7.6V / 8.6V                         | 7.2V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.478 ±0.006       | 0.533 ±0.005       | Pass   |

| 2.5.1.5.1 | 7.6V / 8.6V                         | 6.6V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.460 ±0.013       | 0.531 ±0.005       | Pass   |

| 2.5.1.5.2 | 7.6V / 8.6V                         | 7.2V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.476 ±0.009       | 0.538 ±0.006       | Pass   |

| 2.5.1.6.1 | 7.6V / 8.6V                         | 6.6V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.460 ±0.014       | 0.535 ±0.005       | Pass   |

| 2.5.1.6.2 | 7.6V / 8.6V                         | 7.2V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.478 ±0.009       | 0.542 ±0.006       | Pass   |

| 2.5.1.7.1 | 18V / 18.6V                         | 17.0V            | 1nF (1%);<br>1kΩ (0.1%)     | 0.479 ±0.006       | 0.531 ±0.006       | Pass   |

| 2.5.1.7.2 | 18V / 18.6V                         | 17.6V            | 1nF (1%);<br>1kΩ (0.1%)     | 0.482 ±0.006       | 0.533 ±0.006       | Pass   |

| 2.5.1.8.1 | 18V / 18.6V                         | 17.0V            | 6.8nF (1%);<br>660 Ω (0.1%) | 0.476 ±0.009       | 0.534 ±0.006       | Pass   |

| 2.5.1.8.2 | 18V / 18.6V                         | 17.6V            | 6.8nF (1%);<br>660 Ω (0.1%) | 0.480 ±0.008       | 0.537 ±0.006       | Pass   |

| 2.5.1.9.1 | 18V / 18.6V                         | 17.0V            | 10nF (1%);<br>500 Ω (0.1%)  | 0.477 ±0.010       | 0.537 ±0.006       | Pass   |

| 2.5.1.9.2 | 18V / 18.6V                         | 17.6V            | 10nF (1%);<br>500 Ω (0.1%)  | 0.482 ±0.009       | 0.540 ±0.006       | Pass   |

<sup>\*</sup>The measurement uncertainty analysis based on the type B evaluation according to the "Guide to the Expression of Uncertainty in Measurement" (European Committee for Standardization, ENV 13005, 1999).

The steps involved are as follows:

- 1. Evaluation of the relationship between input quantities xi and the output quantity  $y = f(x_1, x_2, ..., x_n)$

- 2. Identification of the standard uncertainty  $u(x_i)$  for each input estimate  $x_i$

- 3. Identification of the combined standard uncertainty  $u_c\left(x_i\right)$  for the output quantity y

- 4. Calculation of the expanded uncertainty  $U = k \cdot u_c(x_i)$ , with coverage factor k=2. The coverage probability is approximately 95%.

| Comment                                                                                                                                                                                 | Test Result |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| The measured duty cycle D3 must be greater or equal than 0.417 for $V_{SUP}$ = [7.0V 18V], the measured duty cycle D4 must also be less or equal than 0.590 for $V_{SUP}$ = [7.6V 18V]. | Pass        |

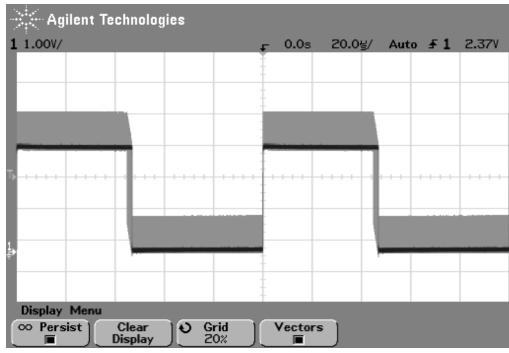

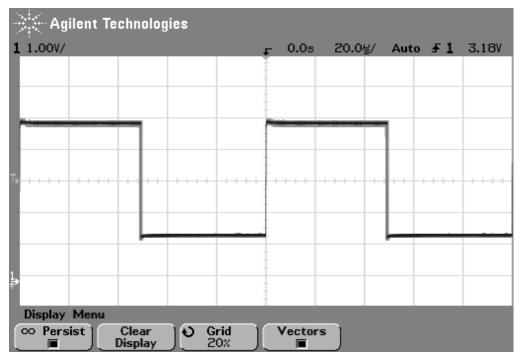

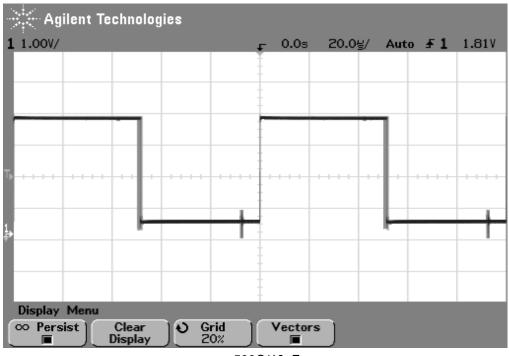

TC 2.5.2 Measuring the Duty Cycle @ 20 kBit/sec – IUT as Transmitter

| Test      | V <sub>SUP</sub> / V <sub>BAT</sub> | V <sub>PS2</sub> | Bus loads                   | Duty cycle        |                   |        |

|-----------|-------------------------------------|------------------|-----------------------------|-------------------|-------------------|--------|

| case #    | (PS 1)                              | (PS 2)           | (C; R)                      | D1±U <sup>*</sup> | D2±U <sup>*</sup> | Result |

| 2.5.2.1.1 | 7.0V / 8.0V                         | 6.0V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.475 ±0.006      | -                 | Pass   |

| 2.5.2.1.2 | 7.0V / 8.0V                         | 6.6V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.484 ±0.005      | -                 | Pass   |

| 2.5.2.2.1 | 7.0V / 8.0V                         | 6.0V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.439 ±0.019      | -                 | Pass   |

| 2.5.2.2.2 | 7.0V / 8.0V                         | 6.6V             | 6.8nF (1%);<br>660 Ω (0.1%) | 0.464 ±0.012      | _                 | Pass   |

| 2.5.2.3.1 | 7.0V / 8.0V                         | 6.0V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.436 ±0.021      | _                 | Pass   |

| 2.5.2.3.2 | 7.0V / 8.0V                         | 6.6V             | 10nF (1%);<br>500 Ω (0.1%)  | 0.464 ±0.013      | -                 | Pass   |

| 2.5.2.4.1 | 7.6V / 8.6V                         | 6.6V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.476 ±0.006      | 0.521 ±0.004      | Pass   |

| 2.5.2.4.2 | 7.6V / 8.6V                         | 7.2V             | 1nF (1%);<br>1kΩ (0.1%)     | 0.484 ±0.006      | 0.528 ±0.005      | Pass   |