## Hardware Design Guidelines for S12 MagniV Mixed-Signal Microcontroller FTF-ACC-F1213

Juan Romero | Automotive Global Applications Engineering Jesus Sanchez | Automotive Global Applications Engineering

SEPTEMBER.2015

External Use

## Agenda

- Introduction to MagniV

- Power Supply Pins

- Programming Interface

- External and internal RC Oscillator

- Programming Circuit

- CAN Physical Layer

- LIN Physical Layer

- High Current / High Voltage Pins

- MagniV in 24V Applications

- Summary

# Introduction to MagniM MCUs

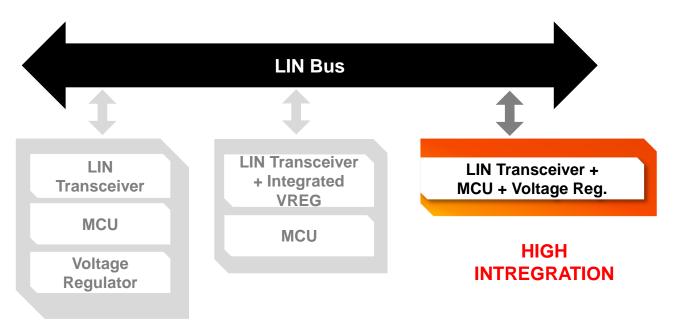

## S12 MagniV: Integration Beyond the MCU

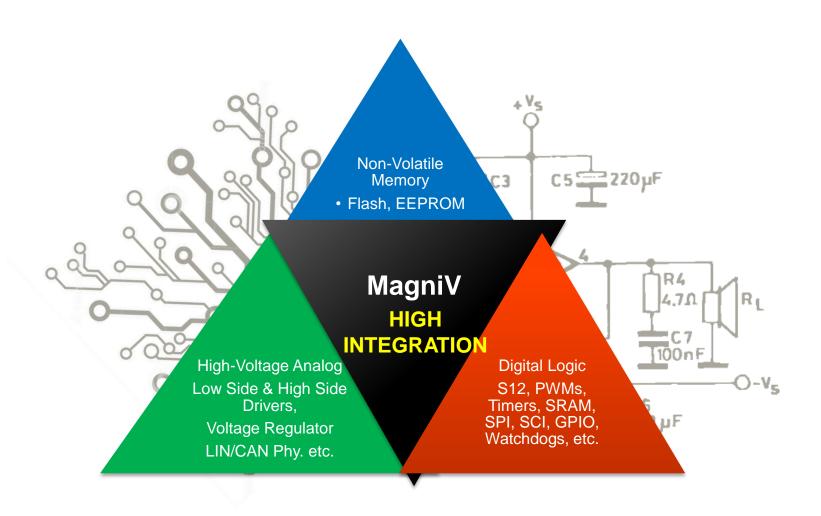

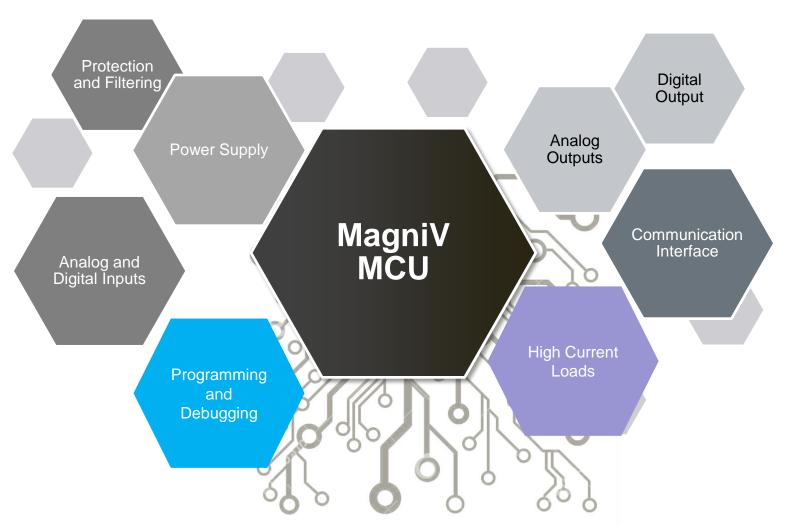

Our \$12 MagniV portfolio simplifies system design with the integration on High-Voltage (HV) analog features onto MCUs for automotive applications

S12VR Relay based DC **Motors**

S12ZVM **BLDC Motor** Control

S12ZVC **Small CAN** nodes

S12ZVL **LIN Nodes**

S12ZVH Cluster **Solutions**

## A Technology Sweet-spot for Sensor and Actuators

# S12 MagniV Benefits

\$12 MagniV solutions deliver optimal system cost and physical footprint for sensor and actuator applications.

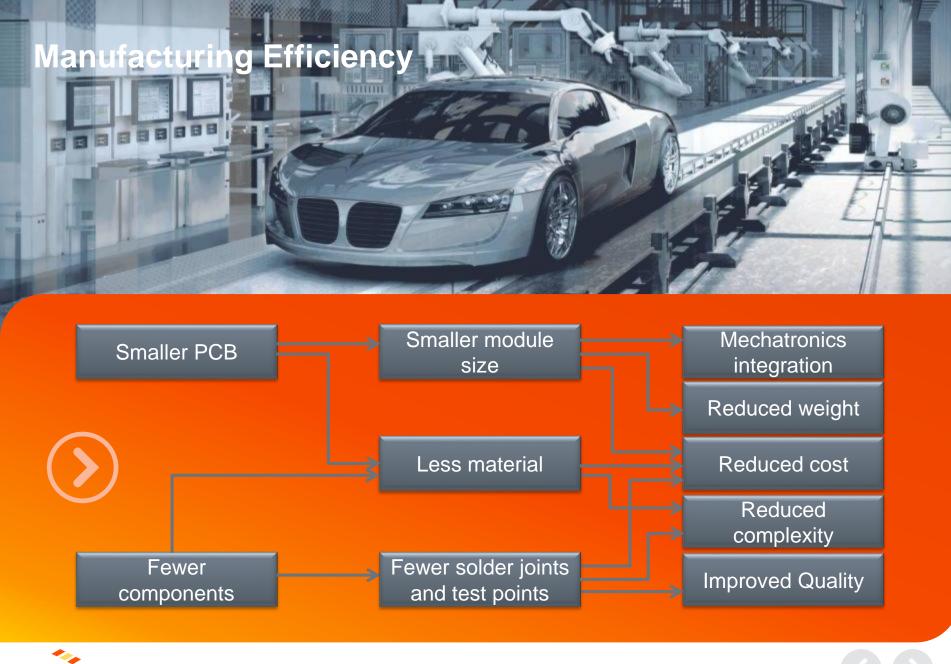

Improved manufacturing efficiency Replacing typically 3 IC by 1 MagniV reduces assembly and test cost while quality improves

Reduced Bill Of Material (BOM) Fewer components to purchase, handle, store and qualify

Simplified motor control that speeds up time-to-market Save up to 6 months on development, validation and ISO26262 implementation Abstract the complexity of 3-phase motor control software development

- Production ready Automotive quality SW and Tools

- SafeAssure program

## **High Level Functional Application**

# Power Supply Pins

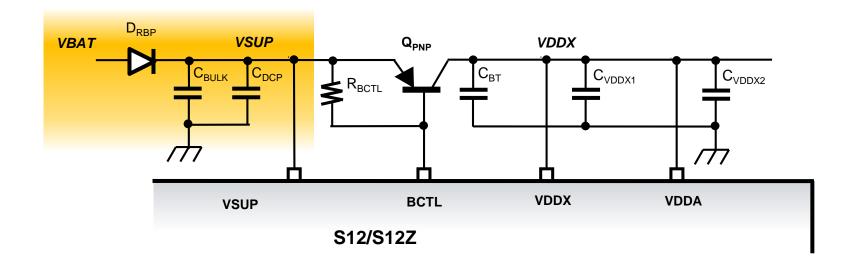

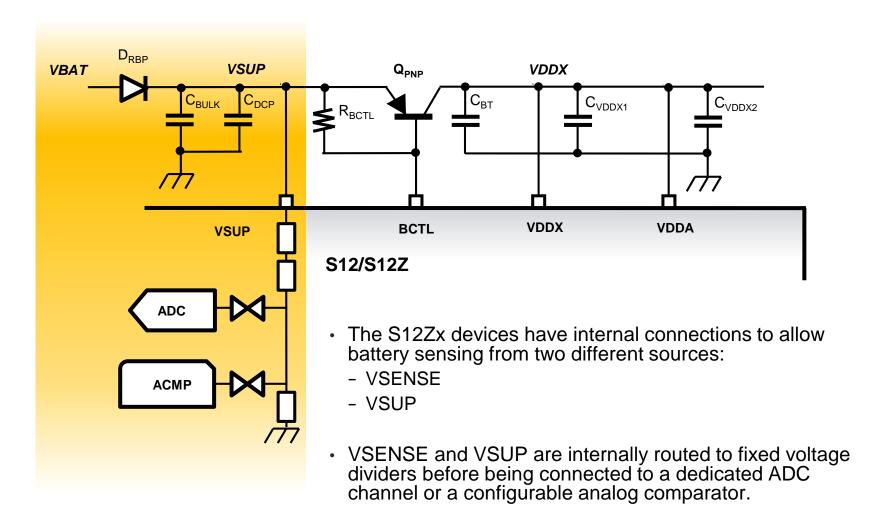

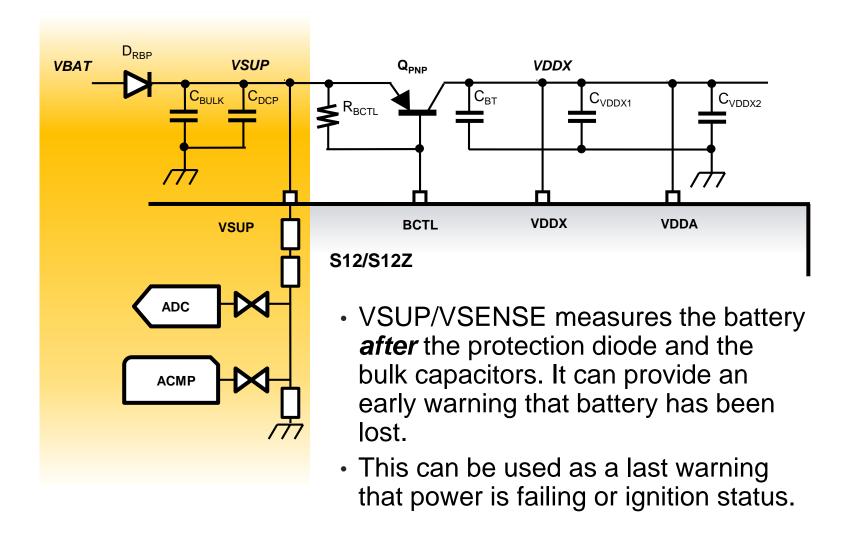

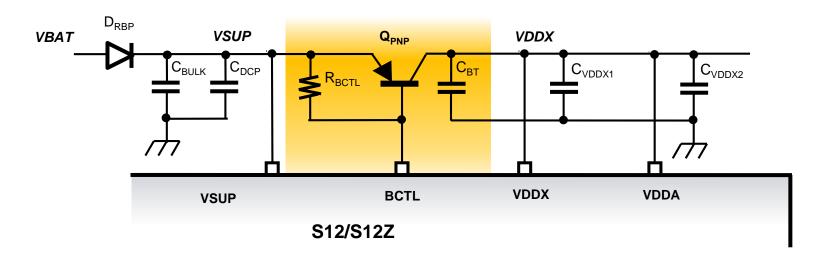

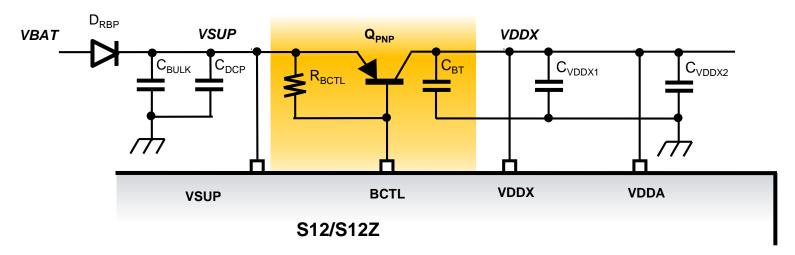

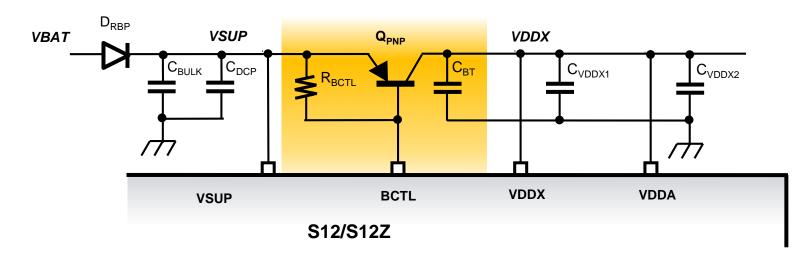

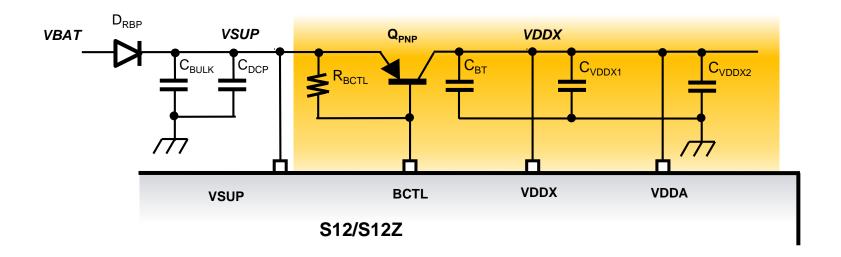

Battery sensing **PNP Ballast Transistor Decoupling Capacitors**

- VSUP is the 12V supply voltage pin for the on chip voltage regulator. This is the voltage supply input from which the voltage regulator generates the on chip voltage supplies.

- It must be protected externally against a reverse battery connection. The simplest protection against reverse battery protection is a diode in series with the battery.

## **Battery sensing**

## **Battery sensing**

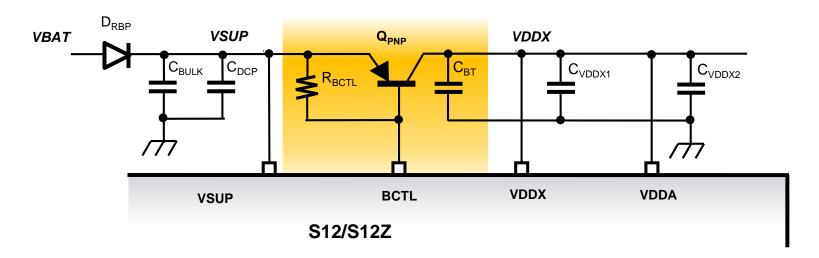

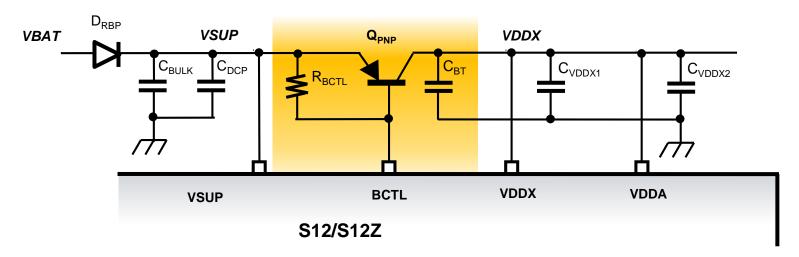

## **VDDX Ballast transistor**

- The external ballast device function extends current capability and reduces internal power dissipation.

- **BCTL** Base Control Pin for external PNP: BCTL is the ballast connection for the on chip voltage regulator. It provides the base current of an external BJT (PNP) of the VDDX and VDDA supplies. An additional 1 K $\Omega$  resistor between emitter and base of the BJT is required

## **VDDX Ballast transistor**

- The maximum output current capability  $[I_{VDDX}]$  using a PNP External Ballast transistor  $[Q_{PNP}]$ , must be determined by the allowed maximum power of the device. The designer should to consider that the maximum power dissipation of the transistor will depend mainly on the following factors:

- Package type

- Dissipation mounting pad area on the PCB

- Maximum Ambient temperature (Application)

**NXP Semiconductors**

#### BCP53; BCX53; BC53PA

80 V, 1 A PNP medium power transistors

#### 6. Thermal characteristics

| Table 7.      | Thermal characteristics                     |             |       |     |     |      |

|---------------|---------------------------------------------|-------------|-------|-----|-----|------|

| Symbol        | Parameter                                   | Conditions  | Min   | Тур | Max | Unit |

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air |       |     |     |      |

|               | BCP53                                       |             | [1] _ | -   | 192 | K/W  |

|               |                                             |             | [2] _ | -   | 125 | K/W  |

|               |                                             |             | [3] - | -   | 93  | K/W  |

|               | BCY53                                       |             | [1] _ | _   | 250 | KΛM  |

- Device mounted on an FR4 PCB, single-sided copper, tin-plated and standard footprint.

- [2] Device mounted on an FR4 PCB, single-sided copper, tin-plated, mounting pad for collector 1 cm<sup>2</sup>.

- [3] Device mounted on an FR4 PCB, single-sided copper, tin-plated, mounting pad for collector 6 cm<sup>2</sup>.

- [4] Device mounted on an FR4 PCB, 4-layer copper, tin-plated and standard footprint.

- 151 Device mounted on an ERA PCR Allover conner tin-plated mounting and for collector 1 cm<sup>2</sup>

$$PWR_{MAX} = \frac{TJ_{MAX} - T_{AMB}}{Rth_{JA}}$$

PWR<sub>MAX</sub> - Maximum power dissipation allowed.

TJMAX - Maximum junction temperatura

T<sub>AMB</sub> – Ambient Temperature

Rth<sub>JA</sub> – Thermal Resistance Junction to ambient

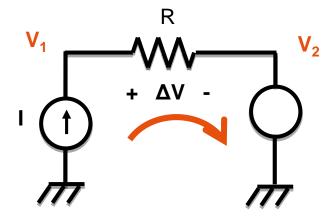

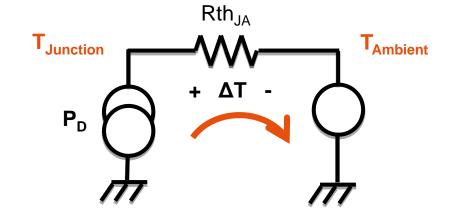

## **Electrical vs. Thermal DC Parameters**

$$\Delta V = (V_1 - V_2) = I * R$$

$R = Electrical Resistance (\Omega)$

V = Potential Difference (V)

I = Current (A)

$$\Delta T = (T_J - T_{AMB}) = P_D * R_{TH}$$

$R_{th}$  = Thermal Resistance (C/W)

$\Delta T$  = Temperature Difference (C)

P<sub>D</sub> = Power Dissipated (W)

$$PWR_{MAX} = \frac{TJ_{MAX} - T_{AMB}}{Rth_{IA}}$$

- VBAT = 12V

- **VFWD** = 0.7V

- VSUP = VBAT VFWD = 11.3V

- **VDDX** = 5V

- $TJ = +150 \, ^{\circ}C$

- TAMB =  $+25^{\circ}$ C

- RthJA = 125 K/W

$$PWR_{PNP} = \frac{TJ_{MAX} - T_{AMB}}{Rth_{JA}} = \frac{(+150^{\circ}C) - (+25^{\circ}C)}{125 K/_{W}}$$

$$PWR_{PNP} = 1W$$

$$I_{VREG_{OUT}} = \frac{PWR_{PNP}}{VSUP - VDDX} = \frac{1W}{12V - 5V} = 142.85mA$$

$$I_{VREG_{OUT}} = 142.85mA$$

http://www.endmemo.com/convert/thermal%20resistance.php

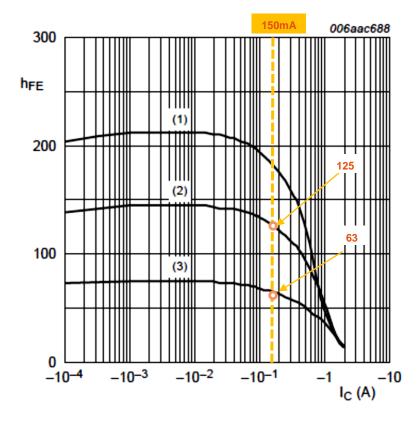

- Transistor specifications give the minimum and maximum gain.

- The worst case is usually significantly lower than the nominal figure on the transistor datasheet cover page. Furthermore, the datasheet values are usually given at room temperature (+25 °C).

- The required gain should be calculated at cold temperature, because a PNP/NPN transistor has minimum gain at low temperature.

- The worst case gain at cold temperature can be obtained from the transistor supplier or can be estimated using the graphs given in the transistor datasheet.

| Outlok | reference of | data a | antinuad |

|--------|--------------|--------|----------|

| Guick  | reference (  | Jala C | ommnuea  |

| Parameter                     | Conditions                                         | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------------------|-----|-----|-----|------|

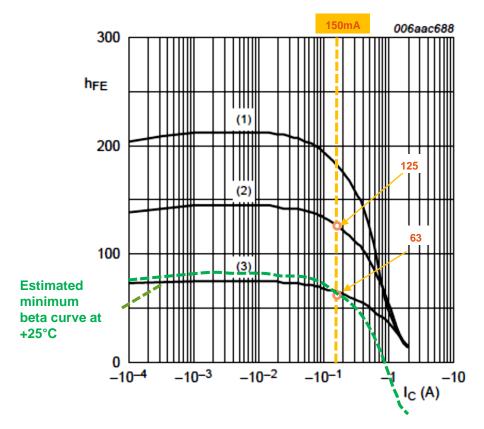

| DC current gain               | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 250 |      |

| h <sub>FE</sub> selection -10 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 160 |      |

| h <sub>FE</sub> selection -16 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 100 | -   | 250 |      |

#### Step1:

Estimate the minimum beta curve at 150mA +25C

Minimum beta is 63 at 150mA, 25C

$$V_{CE} = -2 V$$

(3)

$$T_{amb} = -55 \, ^{\circ}C$$

$$V_{CE} = -2 V$$

(3)

$$T_{amb} = -55 \, ^{\circ}C$$

#### Quick reference data ...continued

| Parameter                     | Conditions                                         | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------------------|-----|-----|-----|------|

| DC current gain               | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 250 |      |

| h <sub>FE</sub> selection -10 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 160 |      |

| h <sub>FE</sub> selection -16 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 100 | -   | 250 |      |

#### Step1:

Estimate the minimum beta curve at 150mA +25C

Minimum beta is 63 at 150mA, 25C

$$V_{CE} = -2 V$$

- (1)  $T_{amb} = 100 \, ^{\circ}C$

- (2) T<sub>amb</sub> = 25 °C

- (3)  $T_{amb} = -55 \, ^{\circ}C$

#### Quick reference data ...continued

| Parameter                     | Conditions                                         | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------------------|-----|-----|-----|------|

| DC current gain               | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 250 |      |

| h <sub>FE</sub> selection -10 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 160 |      |

| h <sub>FE</sub> selection -16 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 100 | -   | 250 |      |

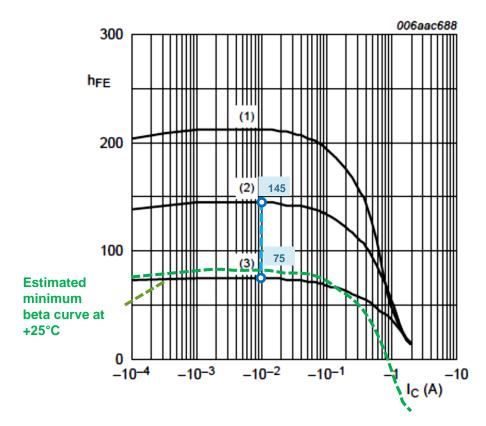

#### Step1:

Estimate the minimum beta curve at 150mA +25C

Minimum beta is 63 at 150mA, 25C

#### Step 2:

Determine temperature coefficient of beta at 10mA from data sheet.

$$= \frac{100\% \times \frac{(145 - 75)}{145}}{+25^{\circ}C - (-55^{\circ}C)} = \frac{48.275}{80} = 0.60^{\%}/_{\circ}C$$

$$V_{CE} = -2 V$$

(1)

$$T_{amb} = 100 \, ^{\circ}C$$

(3)

$$T_{amb} = -55 \, ^{\circ}C$$

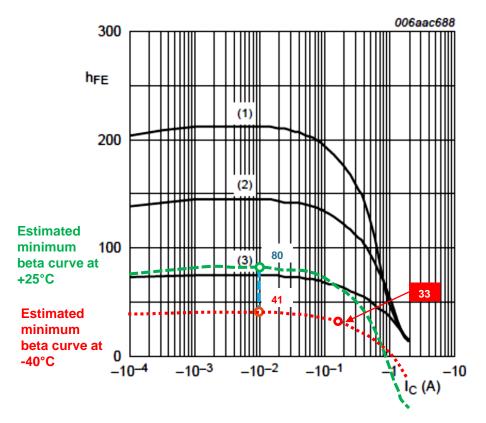

#### Quick reference data ...continued

| Parameter                     | Conditions                                         | Min | Тур | Max | Unit |

|-------------------------------|----------------------------------------------------|-----|-----|-----|------|

| DC current gain               | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 250 |      |

| h <sub>FE</sub> selection -10 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 63  | -   | 160 |      |

| h <sub>FE</sub> selection -16 | $V_{CE} = -2 \text{ V};$ $I_{C} = -150 \text{ mA}$ | 100 | -   | 250 |      |

#### Minimum Beta at -40°C @ 10mA

$$= 80 - (0.60 \%/_{\circ C} * (+25 °C - (-40 °C)))$$

$$= 80 - (0.60 \%/_{\circ C} * (+60 °C) = 41$$

Then we can estimate the minimum beta @150mA, ~33

| Part Number       | Package Type | Manufacturer |

|-------------------|--------------|--------------|

| BCP53             | SOT- 223     | NXP          |

|                   |              | FAIRCHILD    |

| 2SB1260 / 2SB1181 | SOT-89       | ROHM         |

|                   | DPAK         |              |

| 2SA1952           | DPAK         | ROHM         |

| 2SB1181           | SOT-89       | ROHM         |

| TBV               | DPAK         |              |

- Develop a Static Thermal Analysis, and select the appropriate package.

- VCEO parameter acording to the customer requirments.

- Avoid transistors with super betas or >500.

- Make sure worst case hFE at low temperature remains above 30 to avoid the quasi-saturation or saturation condition.

| Symbol             | Characteristic          | Value  |

|--------------------|-------------------------|--------|

| R <sub>BCTL</sub>  | Metal Film resistor     | 1 kΩ   |

| C <sub>BCTL</sub>  | X7R Ceramic or Tantalum | 10 uF  |

| C <sub>VDDX1</sub> | X7R Ceramic             | 220 nF |

| C <sub>VDDX2</sub> | X7R Ceramic             | 220 nF |

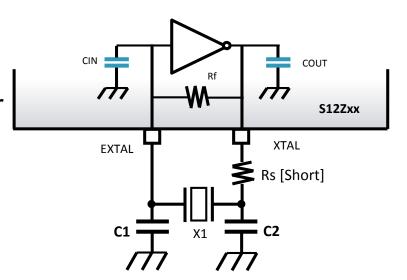

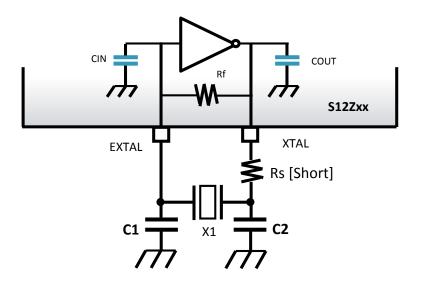

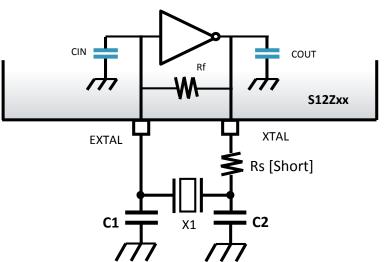

- The S12Z devices have an internal 1 MHz internal RC oscillator with +/-1.3% accuracy over rated temperature range.

- There is an alternative to add an external resonator or crystal, for higher and tighter tolerance frequencies.

- Oscillator pins shared with GPIO functionality

- The oscillation mode is selectable by software.

- The effective load capacitance, CLOAD, appears to the crystal circuit as the series combination of C1 and C2. Correct CLOAD is important for proper operating frequency. Crystals are available with a variety of CLÓAD values.

- It is recommended to select a fundamental mode parallel resonant type crystal having a  $C_{LOAD}$  of around 12 pF and ESR of 30 to 60  $\Omega$ .

- The actual discrete values required for C1 and C2 are generally up to 12 pf below the calculated load capacitance due to PCB traces and the input pin's stray capacitances; the board layout is quite important.

The following formula may be used to calculate a parallel resonant crystal's external load capacitors:

$$C_{LOAD} = ((C_1 \times C_2) / (C_1 + C_2)) + C_{STRAY}$$

Where:

CL = the crystal load capacitance Cstray = the stray capacitance in the oscillator circuit,

Which will normally be in the 2pF to 5pF range. Assuming that  $C_1 = C_2$  then the equation becomes:

$$C_{LOAD} = ((C_1 \times C_1) / (2 \times C_1)) + C_{STRAY}$$

$C_{LOAD} = (C_1 / 2) + C_{STRAY}$

Rearranging the equation, we can find the external load capacitor value:

$$C_{1,2} = 2(C_{LOAD} - Cstray)$$

For example, if the crystal load capacitance is 8pF, and assuming Cstray=3pF, then:

$$C1 = C2 = 2(8pF - 3pF) = 10pF$$

It is difficult to know exactly what the stray capacitance is, but if you find the oscillation frequency is too high, the load capacitor values can be increased. If the frequency is too low, the load capacitors can be decreased.

- Resistance Rs is necessary for the prevention of abnormal oscillation.

- Install Resistance Rs on to the output side after checking the IC terminal function.

- Use the shortest distance for lines connecting parts, including ground lines, in order to prevent the inclusion of unnecessary stray capacitance.

- Do not allow any part of the oscillation circuit to cross over a signal line of any other circuit on the same circuit board.

- Normally, C1 and C2 should be C0G / NP0 type ceramic capacitors for the best tolerance and temperature stability.

- NOTE: All quartz crystal oscillator and ceramic resonator circuits should be characterized by the supplier to make sure the oscillator/resonator is optimized to the particular IC, and that the required accuracy is achieved.

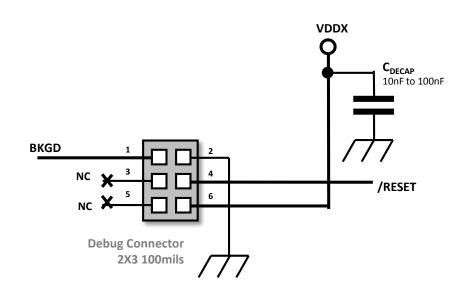

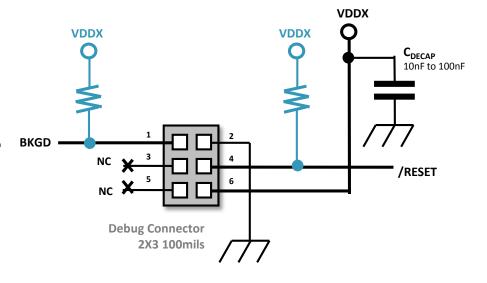

# Programming Interface

BKGD pin Reset pin

## **Programming Circuit**

- □The S12/S12Z family is programmed via the BDM protocol.

- □The BDM protocol is a serial communication that is transmitted through the BKGD line.

- □The standard BDM connector is a 2 by 3 pin header with 100 mil pitch.

- □The BDM connector requires connection to the

- BKGD pin

- RESET pin

- VDDX Voltage

- GND.

## **Programming Circuit**

- □ It is recommended to add a ceramic capacitor to VDDX near the connector to reduce noise that could be injected by the programming circuitry to the power supply.

- □The BKGD signal is used as a pseudo-open-drain signal for the background debug communication. The BKGD pin has an internal pullup device.

- □The RESET signal is an active low bidirectional control signal. It acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset. The RESET pin has an internal pull-up device.

## **CAN Interface**

Hardware Design Guidelines for MagniV Mixed-Signal MCUs

## **CAN Physical Layer**

**Discrete CAN Controller Solution**

- Freescale offers a complete line of products to meet the needs of highperformance CAN embedded applications.

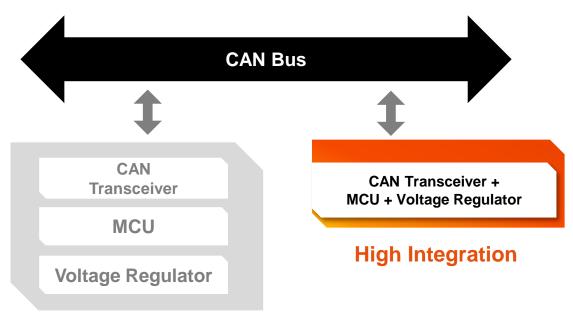

- MagniV MCUs as S12ZVC has an on-chip CAN physical transceiver and a dedicated power supply using an external ballast transistor for its. Having these modules on-chip helps reduce the total amount of components required to implement CAN communication.

## **CAN Physical Layer**

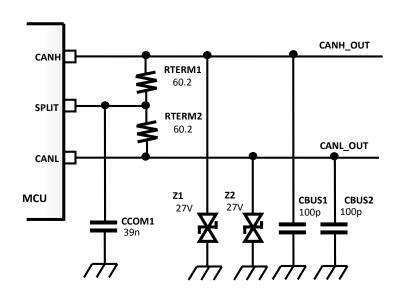

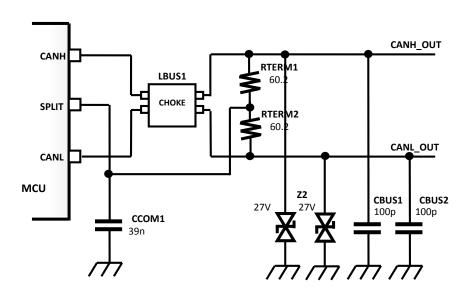

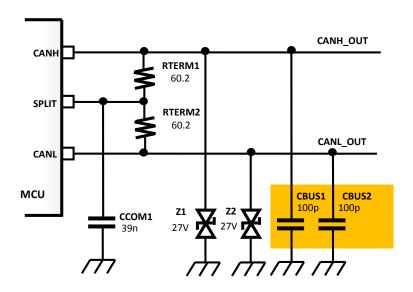

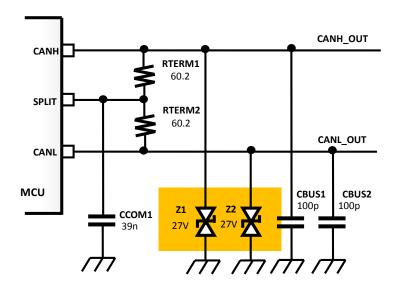

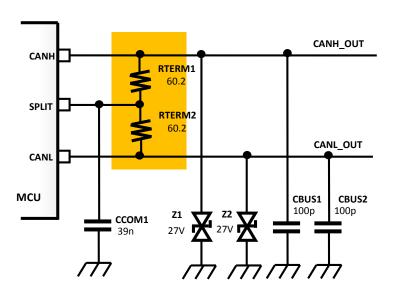

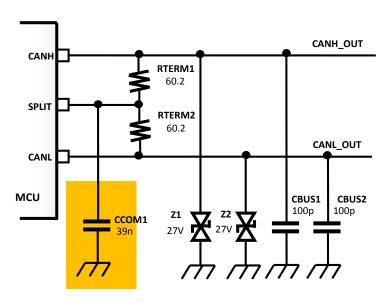

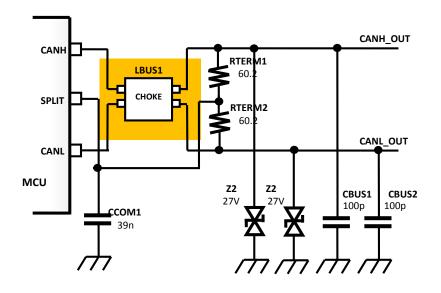

- As any other CAN physical transceiver, the CANH, CANL and SPLIT pins are available for the designer to terminate bus depending on the application. The next figures show examples of CAN node termination:

- CAN Physical transceiver circuit.

- CAN Physical transceiver circuit with common mode choke.

**CAN Physical transceiver circuit.**

CAN Physical transceiver circuit with common mode choke.

## **CAN Physical Layer**

**CAN Physical transceiver circuit.**

| Reference       | Description                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBUS1 and CBUS2 | The Capacitors CBUS1 and CBUS2 are not specifically required. They may be added for EMC reasons, in which case the maximum capacitance from either bus wire to ground must not exceed 300pF total. If zener stacks are also needed, the parasitic capacitance of the zener stacks must also be included in the total capacitance budget. |

| Z1 and Z2       | The zener stacks Z1 and Z2 could be required to satisfy Automotive EMC requirements (ESD in particular). These devices should be placed close to the connector.                                                                                                                                                                          |

**CAN Physical transceiver circuit.**

| Reference          | Description                                                                                                                                                                                                                                                                                                                              |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CBUS1 and<br>CBUS2 | The Capacitors CBUS1 and CBUS2 are not specifically required. They may be added for EMC reasons, in which case the maximum capacitance from either bus wire to ground must not exceed 300pF total. If zener stacks are also needed, the parasitic capacitance of the zener stacks must also be included in the total capacitance budget. |  |  |

| Z1 and Z2          | The zener stacks Z1 and Z2 could be required to satisfy Automotive EMC requirements (ESD in particular). These devices should be placed close to the connector.                                                                                                                                                                          |  |  |

**CAN Physical transceiver circuit.**

| Reference               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTERM1<br>and<br>RTERM2 | Depending on the position of the node within the CAN network it might need a specific termination. R <sub>TERM1</sub> , R <sub>TERM2</sub> and C <sub>COM1</sub> must be that they assist in having an overall cable impedance. On a bus implementation of a CAN network only the two nodes on the two ends of the bus have terminator resistors. The nodes not placed on the end of the CAN bus do not have termination. A thorough analysis is required to maintain this requirement of the CAN networks. |

| CCOM1                   | The SPLIT pin on the transceiver is optional and the designer might choose not to use it. This pin helps stabilize the recessive state of the CAN bus and can be enabled or disabled by software when required.                                                                                                                                                                                                                                                                                             |

**CAN Physical transceiver circuit.**

| Reference               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTERM1<br>and<br>RTERM2 | Depending on the position of the node within the CAN network it might need a specific termination. $R_{TERM1}$ , $R_{TERM2}$ and $C_{COM1}$ must be that they assist in having an overall cable impedance. On a bus implementation of a CAN network only the two nodes on the two ends of the bus have terminator resistors. The nodes not placed on the end of the CAN bus do not have termination. A thorough analysis is required to maintain this requirement of the CAN networks. |

| CCOM1                   | The SPLIT pin on the transceiver is optional and the designer might choose not to use it. This pin helps stabilize the recessive state of the CAN bus and can be enabled or disabled by software when required.                                                                                                                                                                                                                                                                        |

| <b>CAN Physical transceiver circui</b> | t |

|----------------------------------------|---|

| with common mode choke.                |   |

| Reference  | Description                                     |  |  |  |  |

|------------|-------------------------------------------------|--|--|--|--|

| LBUS1      | A common node choke on the CANH and             |  |  |  |  |

| Common     | CANL lines can help reduce coupled              |  |  |  |  |

| mode choke | electromagnetic interference and needed to      |  |  |  |  |

|            | satisfy Automotive EMC requirements. This       |  |  |  |  |

|            | choke, together with transient suppressors on   |  |  |  |  |

|            | the transceiver pins can greatly reduce coupled |  |  |  |  |

|            | electromagnetic noise, and high-frequency       |  |  |  |  |

|            | transients.                                     |  |  |  |  |

|            |                                                 |  |  |  |  |

Hardware Design Guidelines for MagniV Mixed-Signal MCUs

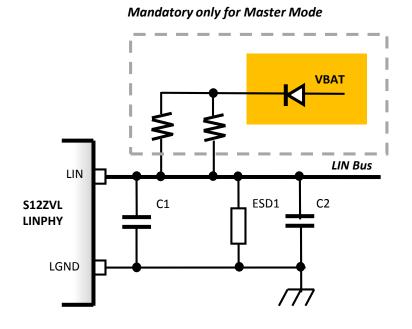

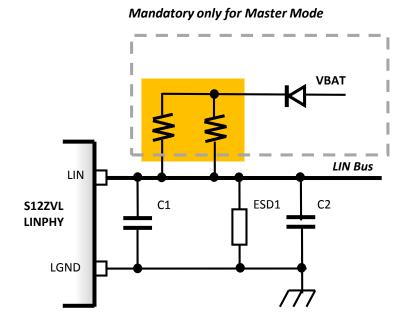

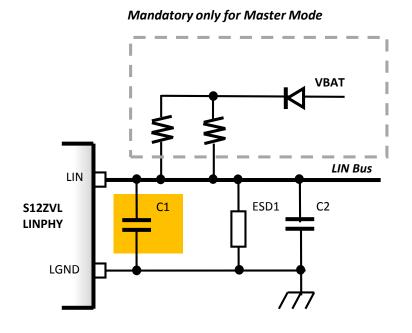

## **LIN Physical Layer**

- Freescale offers a complete line of products to meet the needs of highperformance CAN embedded applications.

- MagniV MCUs as S12ZVL has an on-chip LIN physical transceiver and a dedicated power supply using an external ballast transistor for its. Having these modules on-chip helps reduce the total amount of components required to implement LIN communication.

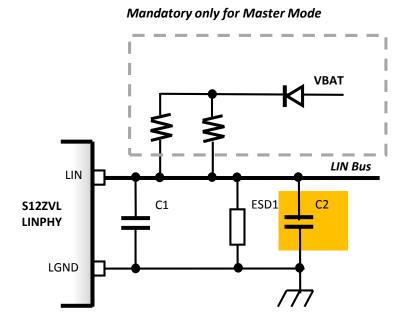

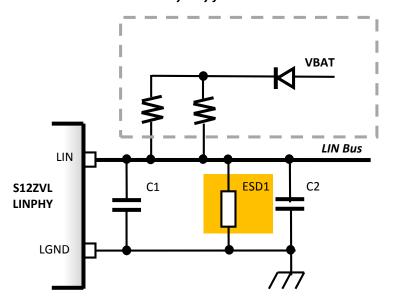

| Reference     | Part                                  | Mounting                                | Remark                                                                                   |

|---------------|---------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------|

| DMLIN         | Diode                                 | Mandator<br>y only for<br>master<br>ECU | Reverse Polarity protection from LIN to VSUP.                                            |

| RMLIN1        | Resistor: 2kΩ                         | Mandator                                | For Master ECU                                                                           |

| and<br>RMLIN2 | Power Loss:<br>250mW                  | y only for<br>Master<br>ECU             | If more than 2 resistors are used in parallel, the values                                |

|               | Tolerance: 1%                         |                                         | have to be chosen in a way that the overall resistance                                   |

|               | Package Size:<br>1206                 |                                         | RM of $1k\Omega$ and the minimum power loss of the complete master termination has to be |

|               | Requirement:                          |                                         |                                                                                          |

|               | Min Power loss of the complete master | fulfilled.                              |                                                                                          |

|               |                                       |                                         | For Slave ECU                                                                            |

|               | termination has<br>to be ≥ 500mW      |                                         | RMLIN1 and RMLIN2 are not needed on the PCB layout                                       |

| Reference               | Part                                                                                                                                                   | Mounting                                | Remark                                                                                                                                                                                                                                                                                           |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMLIN                   | Diode                                                                                                                                                  | Mandator<br>y only for<br>master<br>ECU | Reverse Polarity protection from LIN to VSUP.                                                                                                                                                                                                                                                    |

| RMLIN1<br>and<br>RMLIN2 | Resistor: 2kΩ  Power Loss: 250mW  Tolerance: 1%  Package Size: 1206  Requirement:  Min Power loss of the complete master termination has to be ≥ 500mW | Mandator<br>y only for<br>Master<br>ECU | For Master ECU  If more than 2 resistors are used in parallel, the values have to be chosen in a way that the overall resistance RM of 1kΩ and the minimum power loss of the complete master termination has to be fulfilled.  For Slave ECU  RMLIN1 and RMLIN2 are not needed on the PCB layout |

| Reference | Part                                                                                                | Mounting      | Remark                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1        | Capacitor:  Master ECU: ≥560pF  Slave ECU: 220pF  Tolerance: 10%  Package Size: 0805  Voltage: ≥50V | Mandator<br>y | The value of the master node has to be chosen in a way that the LIN specification is fulfilled.                                                       |

| C2        | Capacitor: Package Size: 0805                                                                       | Optional      | Mounting of the optional part only allowed if there is an explicit written permission of the respective OEM available. Placed close to the connector. |

| Reference | Part                  | Mounting | Remark                                                                                                                                      |

|-----------|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| C1        | Capacitor:            | Mandator | The value of the master node has to be chosen in a way that the LIN specification is fulfilled.                                             |

|           | Master ECU:<br>≥560pF | У        |                                                                                                                                             |

|           | Slave ECU:<br>220pF   |          |                                                                                                                                             |

|           | Tolerance: 10%        |          |                                                                                                                                             |

|           | Package Size: 0805    |          |                                                                                                                                             |

|           | Voltage: ≥50V         |          |                                                                                                                                             |

| C2        | Capacitor:            | Optional | Mounting of the optional                                                                                                                    |

|           | Package Size:<br>0805 |          | part only allowed if there is<br>an explicit written<br>permission of the<br>respective OEM available.<br>Placed close to the<br>connector. |

#### Mandatory only for Master Mode

| Reference | Part                                                                   | Mounting | Remark                                                                                                                                                                                                  |

|-----------|------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESD       | <ul><li>ESD Protection</li><li>Zener</li><li>MOV</li><li>TVS</li></ul> | Optional | Layout pad for an additional ESD protection part.  Mounting of the optional part only allowed if there is an explicit written permission of the respective OEM available. Place close to the connector. |

## High Current / High Voltage Pins

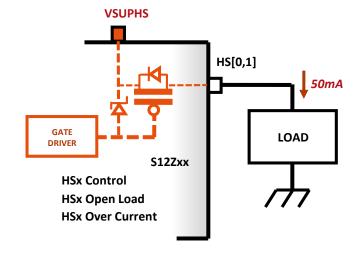

## **High Side Drivers - HSDRV**

- The HSDRV module provides two high-side drivers.

The nominal current for continuous operation to 50mA.

This value is valid for each HS-driver output.

- Both high-side drivers have a common high power supply VSUPHS. VSUPHS can support up to 18V.

- VSUP VSUP VSUPHS

- Selectable gate control of high-side switches:

- HSDR[1:0] register bits,

- PWM channel.

- Timer channel.

- High-load resistance open-load detection when driver enabled and turned off.

- Over-current protection for the drivers, while they are enabled, including:

- Interrupt flag generation.

- Driver shutdown.

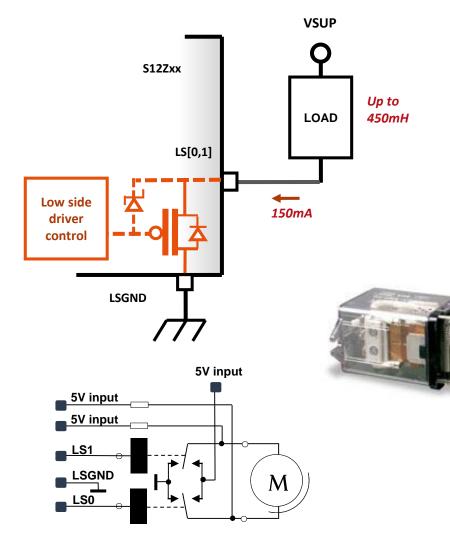

#### Low Side Drivers - LSDRV

- The LSDRV module provides two low-side drivers typically used to drive inductive loads (relays). As inductive load up to 450mH.

- The LSDRV module includes two independent low side drivers with common current sink.

- Selectable gate control of low-side switches:

- LSDRx register bits,

- PWM channel

- Timer channel.

- Open-load detection while enabled

- While driver off:

- selectable high-load resistance

- open-load detection

- Over-current protection with shutdown and interrupt while enabled.

- Active clamp to protect the device against overvoltage when the power transistor that is driving an inductive load (relay) is turned off.

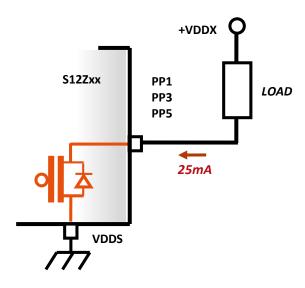

## **High Currents GPIOs**

High-current capable highside output with overcurrent interrupt

+VDDX PP7 20mA **SENSOR** S12Zxx

High-current capable lowside output with overcurrent interrupt

**Enabling MagniV for Truck Applications**

- This section introduces some considerations on how to enable MagniV family devices for 24V applications.

- In particular cases, the common PCB design can be used for both 12V and 24V applications (e.g. cars and trucks).

- The key approach is to add selected external components that extend the device's operational voltage range.

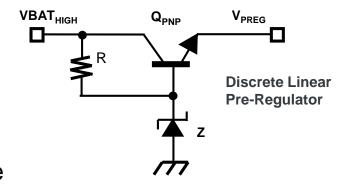

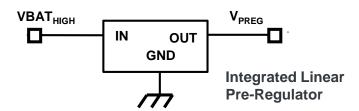

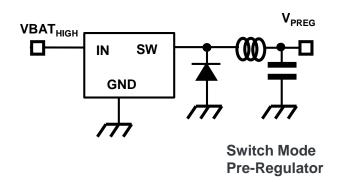

- The MagniV devices can operate from 5.5V to 18V. The MagniV devices include a +5V regulator, so there is no need to regulate the voltage precisely.

- Considering the minimal operating voltage of 10V (ISO16750-2 Norm), and keeping the pre-regulator and MagniV on-chip regulator power dissipation at a reasonable level, the pre-regulator output voltage is regulated to 8V.

- The discrete or integrated linear preregulator is recommended to use for power supply currents below 50mA. The higher currents are managed by a switching power supply as pre-regulator interface.

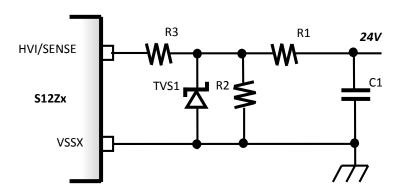

- The HVI and VSENSE pins are designed for operation in a 12V system. Additional external circuitry is needed when the requested operation as in the 24V system.

- The 24V HVI/VSENSE and 24V GND pins interface to the 24V network. The HVI/VSENSE and GND pins are connected to the MagniV device.

- The capacitor C1 suppresses the 24V network's shortest pulses. The C1 value equals units of nF. The resistor divider R1 and R2 divides the 24V HVI/VSENSE input voltage by two to fit the HVI/VSENSE pin voltage range.

- The TVS1 limits the pulses voltage. The TVS1 reverse stand-off voltage equals 20V. The resistor R3, value 10kOhm, protects the HVI/VSENSE pin.

# Summary

## MagniV building blocks

**High-Voltage** Components

**Digital** Components

**MCU Core** and Memories **5V Analogue** Components

**Packaging**

**VREG** for tot. supply: •70mA w/o ext comp. or •170mA with ext. ballast

LIN-

**PHY**

CAN-**PHY**

**V-SUP V-BAT SENSE SENSE**

1-4ch HVI (12V-input with wake-up and ADC)

LS-HSdrivers drivers

**Charge Pump**

4-6ch Gate Drive Unit for FET Qg=50-150nC **MSCAN**

SCI

**GPIO**

Sent

SPI

**PGPIO NGPIO**

25mA

IIC

**BDM/BDC**

20mA

Key **Wakeups**

Win Wdog

**RTC**

Timer 16Bit (25-64MHz)

**PWM** 8/16Bit (25-64MHz)

**Motorcontrol PWM** With Fault protection

> **Programmable Trigger Unit**

**Sound Generator**

Segment LCD (4x40)

**Stepper Motor Driver with SSD**  S12- or S12Z-CPU 25/32/50MHz bus

> Flash (ECC) 8kB - 192kB

**EEPROM (ECC)** 128B - 4kB

> RAM (ECC) 512B - 8kB

**List Based ADC**

10-12Bit resolution 1-2 S/H-units Up to 16ch total

> **Temp** Sense

**Current Sense** (2 x Op-Amp)

**PGA**

Up to 80x

2ch ACMP With 1x6-Bit-DAC

Pierce Osc.

32kHz low power Osc

RCosc. +/-1.3%

**PLL**

LQFP: 32/48/64/100/144-pin

> 150°C LQFP-EP: 48/64-pin

QFN: 32-pin (5x5mm)

www.Freescale.com