- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- imx7d ENET1 not working with DP83825

imx7d ENET1 not working with DP83825

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

imx7d ENET1 not working with DP83825

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Everyone,

I am working on enet1 on imx7d, interfacing it with DP83825. I have made the changes for PIN's as suggested in my last post. Here are my device tree changes

&fec1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet1>;clocks = <&clks IMX7D_ENET_AXI_ROOT_CLK>,

<&clks IMX7D_ENET_AXI_ROOT_CLK>,

<&clks IMX7D_ENET1_TIME_ROOT_CLK>,

<&clks IMX7D_PLL_ENET_MAIN_50M_CLK>;

clock-names = "ipg", "ahb", "ptp", "enet_clk_ref";

assigned-clocks = <&clks IMX7D_ENET1_TIME_ROOT_SRC>,

<&clks IMX7D_ENET1_TIME_ROOT_CLK>;

assigned-clock-parents = <&clks IMX7D_PLL_ENET_MAIN_50M_CLK>;

assigned-clock-rates = <0>, <100000000>;

phy-mode = "rmii";

phy-handle = <ðphy0>;

phy-supply = <&enet3v3>; /*Ethernet power enable*/

/delete-property/ fsl,magic-packet;

phy-reset-gpios = <&gpio3 26 GPIO_ACTIVE_HIGH>;

phy-reset-duration = <2>;

phy-reset-post-delay = <50>;

pinctrl-assert-gpios = <&gpio3 24 GPIO_ACTIVE_HIGH>;

status = "okay";mdio {

#address-cells = <1>;

#size-cells = <0>;ethphy0: ethernet-phy@0 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0>;

//clock-names = "rmii-ref";

device-type = "ethernet-phy";

};

};

};pinctrl_enet1: enet1grp {

fsl,pins = <

MX7D_PAD_ENET1_RGMII_TD0__ENET1_RGMII_TD0 0x73

MX7D_PAD_ENET1_RGMII_TD1__ENET1_RGMII_TD1 0x73

MX7D_PAD_ENET1_RGMII_TX_CTL__ENET1_RGMII_TX_CTL 0x73MX7D_PAD_ENET1_RGMII_RD0__ENET1_RGMII_RD0 0x73

MX7D_PAD_ENET1_RGMII_RD1__ENET1_RGMII_RD1 0x73

MX7D_PAD_ENET1_RGMII_RXC__ENET1_RX_ER 0x73MX7D_PAD_ENET1_TX_CLK__CCM_ENET_REF_CLK1 0x73

MX7D_PAD_EPDC_BDR0__CCM_ENET_REF_CLK2 (MX7D_PAD_SION | MX7D_PAD_CTL_DSE_X2)MX7D_PAD_SD2_WP__ENET1_MDC 0x3

MX7D_PAD_SD2_CD_B__ENET1_MDIO 0x3MX7D_PAD_ENET1_RGMII_RX_CTL__ENET1_RGMII_RX_CTL 0x73

MX7D_PAD_LCD_DATA21__GPIO3_IO26 (MX7D_PAD_CTL_PUS_100K_DOWN | MX7D_PAD_CTL_PUE | MX7D_PAD_CTL_SRE_SLOW | MX7D_PAD_CTL_DSE_X1) /* n_ENET_RST */

MX7D_PAD_LCD_DATA19__GPIO3_IO24 (MX7D_PAD_CTL_PUS_100K_DOWN | MX7D_PAD_CTL_PUE | MX7D_PAD_CTL_SRE_SLOW | MX7D_PAD_CTL_DSE_X1) /* n_ENET_PWDN */

>;

};

I am using an external clock from DP83825, the clock seems to be ok from DP83825. I have made the changes accordingly in mach-imx7d.c as follows:-

I went through this thread i.MX7 RMII 50MHz clock and found that for me as well ENET1_REF_CLK_ROOT is 0. Shall this bit be set or not, if using the external clock to ENET1? Could you please provide some info on this, I am not clear after reading imx7d reference manual.

./memtool CCM.TARGET_ROOT78

SOC: i.MX7D

CCM Addr:0x30380000

CCM.TARGET_ROOT78 Addr:0x3038A700 Value:0x00000000 - See Target Interface for more information.

If it needs to be set while using the external clock as well, please suggest me how can I do it?

Other than this, am I missing anything to implement for ethernet?

Regards,

Asma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Asma

what bsp used in the case, referenced thread issue should be fixed in last bsps.

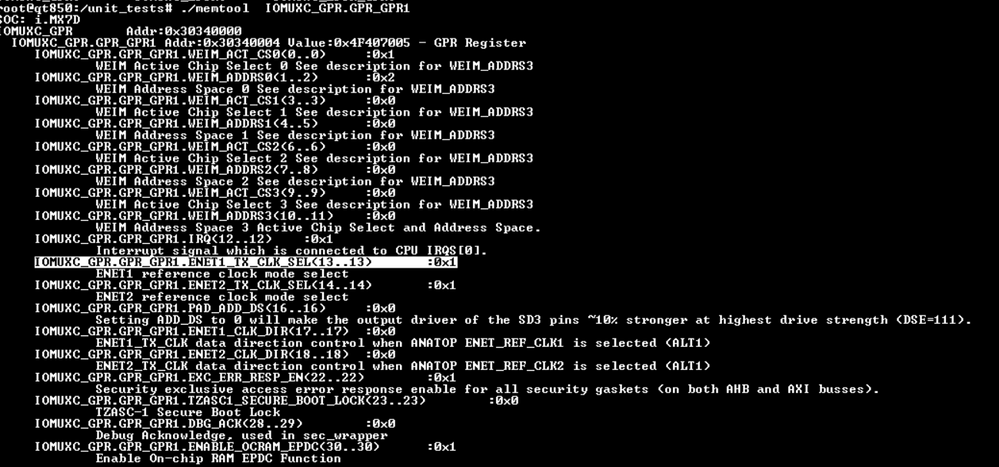

Reference clock direction is defined by bit ENET1_TX_CLK_SEL,

register IOMUXC_GPR_GPR1 described in sect.8.2.4.2 GPR1 General

Purpose Register (IOMUXC_GPR_GPR1)

i.MX 7Dual Applications Processor Reference Manual

In NXP i.MX7D Sabre uboot it is configured in function setup_fec()

mx7dsabresd.c\mx7dsabresd\freescale\board - uboot-imx - i.MX U-Boot

RMII example can be found in imx7 colibri board

uboot-imx/colibri_imx7.h at imx_v2018.03_4.14.98_2.0.0_ga_var01 · varigit/uboot-imx · GitHub

uboot-imx/colibri_imx7.c at imx_v2018.03_4.14.98_2.0.0_ga_var01 · varigit/uboot-imx · GitHub

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using 4.19.35.

I checked IOMUXC.GPR_GPR1 register for ENET1_TX_CLK_SEL. It is set to 1. I think this is right.