- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MQX Software Solutions

- :

- MQX Software Solutions

- :

- K70 DDR2 temperature affect read data

K70 DDR2 temperature affect read data

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

K70 DDR2 temperature affect read data

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Default DDR2 configuration of ddr data error of high temperature exists.

By modifying the :

sim->MCR &= 0xFFFFFF00;

sim->MCR |= 0xC4;

This modified can solve the problem of high temperature DDR data error, but cause low temperature (10 - c) read DDR data error

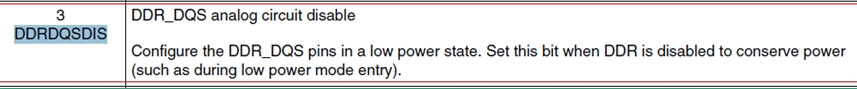

I found MCR -> DDRDQSDIS = 1 high temperature ddr data error, MCR -> DDRDQSDIS = 0 low temperature(-10C) error

Finally, I by single chip microcomputer internal ADC temperature sensor, automatic adjustment, but long run time is still likely to collapse(Not ideal)

Is there a better solution?

the same problem:

K70 and DDR2 SDRAM unstable work

K70 DDR2 read failure with increasing temperature

My DDR configuration code:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you please confirm your device mask? There is an errata in which the DDR controller read logic can get out of synchronization. For the small subset of devices that exhibit the issue, the problem occurs within a narrow temperature window.

I recommend you to check the errata document below to see more information and workaround.

https://www.nxp.com/docs/en/errata/KINETIS_4N96B.pdf

Best regards,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored.

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------