- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- QorIQ

- :

- LS1046A DDR4 interface : VTT island and ECC doubts

LS1046A DDR4 interface : VTT island and ECC doubts

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LS1046A DDR4 interface : VTT island and ECC doubts

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm developing a board with LS1046A. I would like to use LS1046A DDR controller using x72 data bus: x64-bit data and x8-bit ECC. As a guide, I've seen the scheme of DDR4 in FRWYLS1046A-PA, so 4 DDR4 devices are used for data and one DDR4 device is used for ECC.

In our case, we are considering the use of DDR4 MT40A256M16LY-062 IT from Micron.

Regarding the design of FRWYLS1046A-PA and the use of MT40A256M16LY-062, I have certain doubts after reading AN5097 application note:

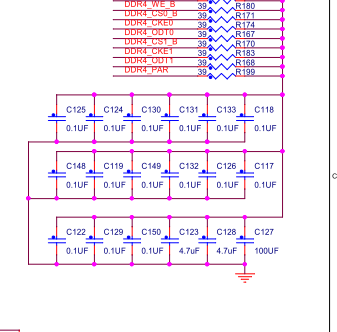

1) Item no. 8 and 9: in the VTT island it is recommended the use of one low ESL capacitor for each group of four termination resistors, at least one 4.7uF cap and a bulk capacitor (47 - 220 uF) at each end of the VTT island.

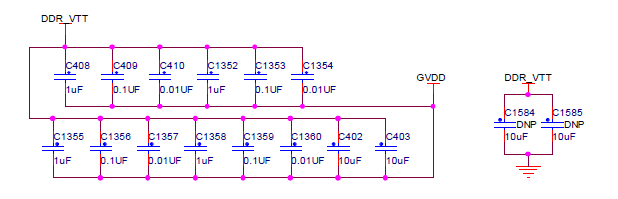

However, in FRWYLS1046A-PA I only see two capacitors of 10 uF connected to DDR_VTT (VTT Power supply). Additionally, there is a capacitor network used to decouple DDR_VTT( VTT Power supply) from GVDD (LS1046A DDR controller and DDR4 VDD power supplies). (Figure below)

So, which is the best way for decoupling the VTT island? Only acccording to AN5097 recommendations or including both methods?

Is it necessary to decouple DDR_VTT from GVDD? I don't find anything about this in NXP or Micron datasheets.

2) Item no. 60: it is stated to pull-up the eight unused DQ pins when 16-bit DRAM is used for ECC. On the other hand, TN4041 application note from Micron recommends to leave those pins unconnected. This last case is implemented in FRWYLS1046A-PA. Are both type of connections valid? Which is the best solution?

Thank you in advance for your help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I progress in our design, new doubts about DDR4 appears. This is not related with my previous question, but I need clarification about one issue:

LS1046 DDR Controller provides a clock signal DDRCLK (pin J20) . According to LS1046ARM, this signal is the reference clock to the DDR PLL and the configuration of the DDR PLL is done with Clocking_PLLDGSR register (DDR PLL general status register). In this register, it is necessary to set KILL bit = 0 to enable PLL performance and configure CFG field to fix the PLL multiplier where CFG field reflects the values programmed in RCW[MEM_PLL_RAT].

But according to Table 4-14 of LS1046ARM, MEM_PLL_RAT of RCW register configures the DDR PLL : SYSCLK ratio.

I understand that DDRCLK and SYSCLK are different clock signals. So , is DDR PLL obtained from DDRCLK or from SYSCLK?

Thank you in advance

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Method described in the AN5097 is preferable.

2) Both variants are possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

Could you please tell me, Is the below VTT termination(LS1043ARDB) abiding to AN5097?

Thanks & Regards

Urmila P

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for your response ufedor.

As per your response, it is better to decouple VTT according to AN5097 application note. Regarding the recomentation of the use of one low ESL capacitor for each group of four termination resistors, which value of capacitor is better to use? Or is it better to include two caps for each x4 resistor array (For example: 100nF and 10 nF per group)?

Regarding termination of ECC DDR4, if unused DQ pins are left unconnected, would DDR4 device suffer from integrity issues?

Thank you in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

100nF and 1uF per group.

> would DDR4 device suffer from integrity issues?

You wrote:

>> On the other hand, TN4041 application note from Micron recommends to leave those pins unconnected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you very much for all your help.