- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX8QM SCU WatchDog

iMX8QM SCU WatchDog

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX8QM SCU WatchDog

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm trying to enable the Watchdog timer on the SCU of a custom iMX8QM design.

The iMX8QM Reference Manual (rev F) states that:

13.9.3 Application Information

The watchdog is enabled by default after reset. [...]

By printing the Watchdog Control and Status Register (CS) in the SCU board_init() I get the value:

WDOG_SC->CS = 0x25E2

That means WDOG is enabled with interrupts, clock source is LPO_clk, configuration successfull, locked.

However, if I print several times with delays the WD Counter Register (WDOG_SC->CNT), the value is always 0x0, like if the clock it is not running. This configuration, which is the default one as in WDOG32_GetDefaultConfig(), can be applied with success to the WDOG of the Cortex-M4 0. In this case everything runs as expected, the LPO clock correctly increments the CNT register. (The only weird thing is that the Reference Manual states that the CM40 is enabled by default, which is not true: it has to be enabled explicitly).

If I reconfigure the SCU WDOG to use the Internal Clock instead of the LPO one, the CNT register runs and the WDOG triggers.

However, no one will refresh the SCU WDOG, and the SCU gets rebooted.

Questions:

- The SCU lpo_clk seems not working, while Cortex-M4-0 lpo_clk works. Is that expected?

- Is it true that the SCU WDOG is automatically started after a reset? (That's not true for C-M4-0)

- Who kicks the SCU WDOG and at which frequency? That's in the prebuilt SCU part?

Tested SCU versions: 1.2.x, 1.5.0 (with the same outcome)

Thank you,

Francesco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the RM I have found this information:

5.7.3.2 Watchdog

By default, ROM will disable the SCU Watchdog (WDOG) unless the fuse

WDOG_ENABLE is blown. The timeout can be selected by using the fuse

WDOG_TIMEOUT_SELECT. [...]

I did not blown the WDOG_ENABLE fuse, is that the reason the SCU WDOG does not count?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Francesco

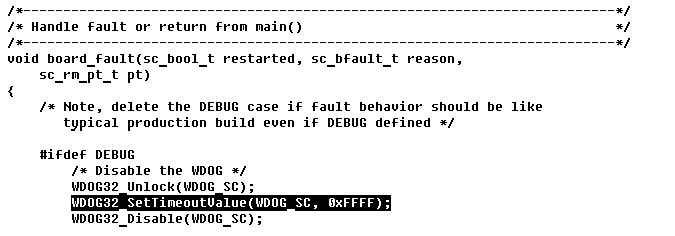

one can look at wdog functions in scfw :

../platformboard/mx8qm_mek/board.c

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

that looks like it is used to disable the watchdog in case of fault, to investigate issues in debug builds. Isn't it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Francesco

I am afraid it is not possible to reconfigure SCU wdog as SCU manages all functions of processor,

it is designed exclusevly for internal purposes

System Controller Unit (SCU) Introduction for i.MX 8QXP MEK - i.MXDev Blog

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor, thank you for your answer.

I know the SCU FW has an internal scope. I just would like to know if the SCU Watchdog is correctly enabled (and refreshed) by the SCU FW. By reading the internal registers it looks something is wrong.

Thank you!

Francesco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

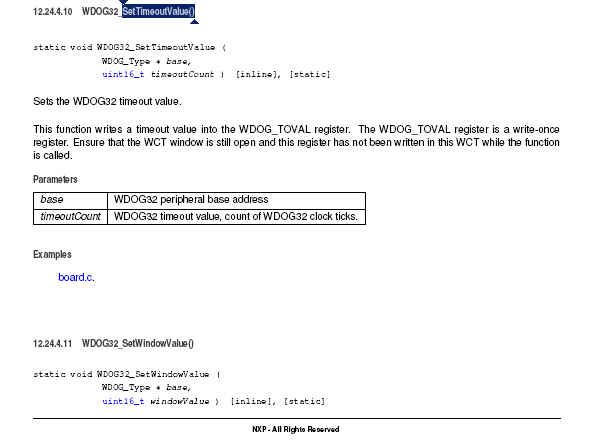

Hi Francesco

SCU wdog has some write-once bits and since it is used at early boot time

by ROM and SECO seems it is not possible to fully reprogram it for own needs.

In general one can look at wdog driver sources:

imx8_wdt.c\watchdog\drivers - linux-imx - i.MX Linux kernel

sect.13.7 (SVC) Timer Service sc_fw_api_qm_b0.pdf document included in

Pay attention to next description:

"The following pads are part of the SCU and the application will not be able to access them:

- SC_P_SCU_PMIC_MEMC_ON

- SC_P_SCU_WDOG_OUT"

System Controller Firmware 101 - Getting started

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

I do not want to reprogram the SCU WDOG for my needs, I just would like it to be working so in case the SCU FW gets stuck it will reboot the board (or the M4 core).

So that's clear that an application has no access to SC_P_SCU_WDOG_OUT, and that's not what I want to do. I just would like that the SCU FW will correctly configure, start and refresh the SCU WD. That's not the case, and you can verify it by dumping the WDOG_SC->CS and WDOG_SC->CNT registers in the SCU board.c.

Thank you!

Francesco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Francesco

one can look at

https://community.nxp.com/message/1268824?commentID=1268824#comment-1268824

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor

the link points to a private git server. Assuming the code is the same on CodeAurora, that directory contains only the Linux watchdog module test (which tests the partition watchdog, which is software according to the SCU porting guide, and not related to the WDOG_SC).

Thank you,

Francesco