- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5744P CTU-ADC issue

MPC5744P CTU-ADC issue

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5744P CTU-ADC issue

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My application is using FLEXPWM_MRS as reload signal for CTU_0 to trigger 8 channels of ADC1 in trigger mode.

below are the configuration of CTU and ADC module:

CTU_0.TGSISR.R = 1; /* Input 0 Rising edge Enable -- FlexPWM_0_MRS */

CTU_0.TGSCR.R = 0; /* Prescaler is 1, trigger mode */

CTU_0.TGSCRR.R = 0;

CTU_0.TGSCCR.R = 8000; /* 20KHz by default */

CTU_0.TCR[0].R = 4000; /* center point trigger sample */

CTU_0.CLCR1.B.T0_INDEX = 0; /* Trigger 0 command list 1st command address */

CTU_0.THCR1.R = 0x41; /* Trigger 0 enable, ADC command output enable */

CTU_0.CLR[0].A.R = 0x0020; /* single conversion, result to FIFO0, ADC1-CH0 */

CTU_0.CLR[1].A.R = 0x0021; /* single conversion, result to FIFO0, ADC1-CH1 */

CTU_0.CLR[2].A.R = 0x0022; /* single conversion, result to FIFO0, ADC1-CH2 */

CTU_0.CLR[3].A.R = 0x0024; /* single conversion, result to FIFO0, ADC1-CH4 */

CTU_0.CLR[4].A.R = 0x0025; /* single conversion, result to FIFO0, ADC1-CH5 */

CTU_0.CLR[5].A.R = 0x0026; /* single conversion, result to FIFO0, ADC1-CH6 */

CTU_0.CLR[6].A.R = 0x0027; /* single conversion, result to FIFO0, ADC1-CH7 */

CTU_0.CLR[7].A.R = 0x0028; /* single conversion, result to FIFO0, ADC1-CH8 */

CTU_0.CLR[8].A.R = 0x4000; /* last command */

CTU_0.FTH.R = 7; /* FIFO 0 threshold is 7 to accept 8 ADC results */

CTU_0.FCR.R = 4; /* FIFO 0 threshold overflow interrupt enable */

INTC_0.PSR[709].R = 0x800E;

// CTU_0.EFR.R = 0xFFFF;

CTU_0.CR.R = 0x3; /* General reload and TGS input selection reload enable */

ADC_1.MCR.R = 0x80020000; /* Enable overwriting older conversion results, ADC clock = half of bus clock (80MHz) */

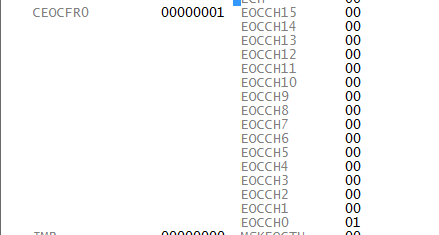

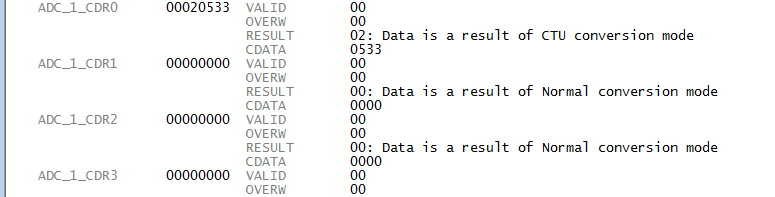

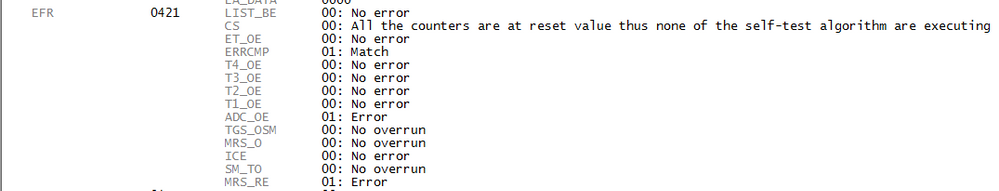

But I observe that ADC_OE bit and ERRCMP bit in EFR register is set, EOCCH0 of ADC1 is set, conversion result is stored in ADC_1_CDR0, but consecutive channels not triggered.

I parse the CTU chapter and demo for several times and still cannot find the root cause.

please help check what is wrong in my code. what cause the ADC_OE ERROR?

thanks in advance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

you have a MRS_RE error too, means MRS appears while double buffered registers are written but before GRE is set. So no update is done.

Do you do any changes of double buffered registers while running? Or you did just the init. For the latter one do you init CTU and ADC first then start FlexPWM?

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Petr, thanks for your quick response.

I do not change any of double buffered registers while running, only reading FIFO0 when FIFO0 overflow interrupt occurs and set GRE. But the overflow never happen as only the first ADC channel conversion executed and errors set in EFR register. I also checked the sequence of initialize and its correct.

Please help check what's wrong in it.

Thanks a lot!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

CTU code looks normal. Can you share ADC and PWM code too, or register value.

What is ADC_CLK and MOTC_CLK.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Petr, thanks for your quick response.

below are clock settings:

/* PBRIDGEx_CLK Divide */

MC_CGM.SC_DC0.B.DIV = 3; /* Freq = sysclk / (3+1) */

/* PBRIDGE_0, PBRIDGE_1 clock: 160/4 = 40MHz */

MC_CGM.SC_DC0.B.DE = 1; /* Enable divided clock */

PLL_160MHz();

MC_CGM.AC0_SC.B.SELCTL = 0b10; //Select PLL0_PHI as source of ADC analog clock

MC_CGM.AC0_DC0.R = 0x80000000; //Enable MOTC clock and divide PLL0 by 1

MC_CGM.AC0_DC2.R = 0x80030000; //Enable ADC_CLK and divide PLL0_PHI source by 4

MC_ME.PCTL237.B.RUN_CFG = 0b001; /* Adc0 : select peripheral configure RUN_PC[1] */

MC_ME.PCTL126.B.RUN_CFG = 0b001; /* Adc1 : select peripheral configure RUN_PC[1] */

MC_ME.PCTL235.B.RUN_CFG = 0b001; /* Adc2 : select peripheral configure RUN_PC[1] */

MC_ME.PCTL124.B.RUN_CFG = 0b001; /* Adc3 : select peripheral configure RUN_PC[1] */

MC_ME.PCTL251.B.RUN_CFG = 0b001; /* CTU 0 : select peripheral configure RUN_PC[1]*/

MC_ME.PCTL255.B.RUN_CFG = 0b001; /* FlexPWM 0: select peripheral configure RUN_PC[1] */

FlexPWM works fine. and there is no issue for ADC1 when works in normal mode.

I also attach the FIFO0 overflow interrupt service function.

uint32_t TEMP[9];

void CTU_FIFO_0_ISR(void)

{

FIFO_0_Status = CTU_0.FST.R & 0x0F;

if(FIFO_0_Status == 4) /* if FIFO 0 overflow */

{

Counter_CTU_0_TR0++;

TEMP[0] = (uint32_t)CTU_0.FR[0].R;

TEMP[1] = (uint32_t)CTU_0.FR[0].R;

TEMP[2] = (uint32_t)CTU_0.FR[0].R;

TEMP[4] = (uint32_t)CTU_0.FR[0].R;

TEMP[5] = (uint32_t)CTU_0.FR[0].R;

TEMP[6] = (uint32_t)CTU_0.FR[0].R;

TEMP[7] = (uint32_t)CTU_0.FR[0].R;

TEMP[8] = (uint32_t)CTU_0.FR[0].R;

CTU_0.CR.B.GRE = 1; /* General reload enable */

}

if(FIFO_0_Status == 8)

{

CTU_0.FST.R = 8; /* Clear overrun flag */

}

}

can you please try from your side if it works?

thanks for your support.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

per the RM "The CTU MOTC_CLK must be two times of ADC_CLK or equal to ADC_CLK."

You have CTU running on 160MHz and ADC clock on 20MHz.

Try to set MC_CGM.AC0_DC2.R = 0x80000000; to have ADC clocked by 80MHz, which is max clock for module.

Also there are few examples you can refer to

Example MPC5744P FlexPWM CTU ADC synchronization GHS614

https://community.nxp.com/docs/DOC-104627

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Petr

it works after I change the ADC clock as your comment. thanks a lot.

best Regards,

Zhiming