- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- I.MX8MM RMII MODE UBOOT-CONFIGURATION

I.MX8MM RMII MODE UBOOT-CONFIGURATION

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I.MX8MM RMII MODE UBOOT-CONFIGURATION

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI,

I am facing an issue , Not able to see any data on the TXD pin of the processor line during ping command from Uboot and I am getting below message

____________________________________

ARP Retry count exceeded; starting again

ping failed; host 192.168.36.136 is not alive

_________________________________________

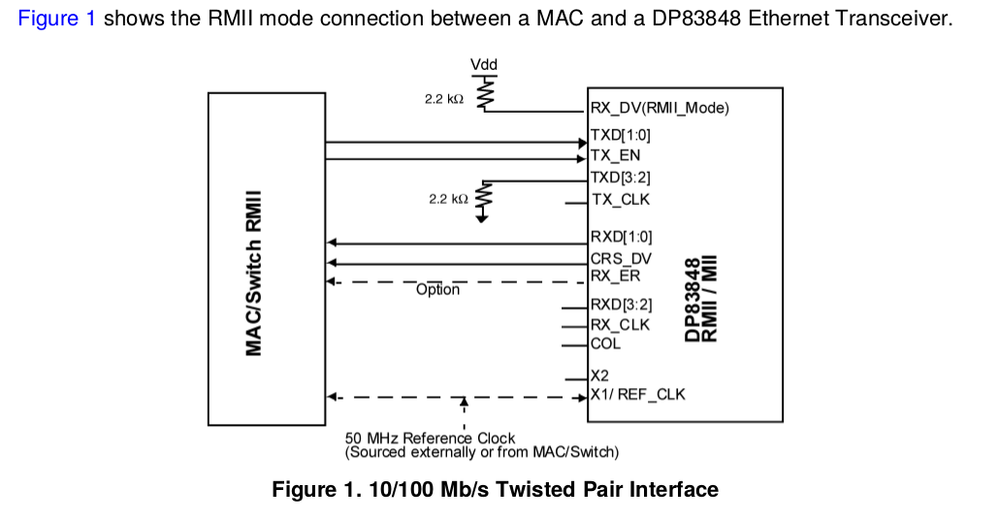

I am using DP83848 PHY IC in I.MX8MM custom board, Following are my configuration for RMII Mode. Do let me know the correct configuration to solve my issue

1. In fsl-imx8mm-evk.dts

--------------------------------------------------------------------------------------------------------------------------

pinctrl_fec1: fec1grp {

fsl,pins = <

MX8MM_IOMUXC_ENET_MDC_ENET1_MDC 0x3

MX8MM_IOMUXC_ENET_MDIO_ENET1_MDIO 0x3

MX8MM_IOMUXC_ENET_TD3_ENET1_RGMII_TD3 0x1f

MX8MM_IOMUXC_ENET_TD2_ENET1_RGMII_TD2 0x1f /*ENET_TD2 OR REF_CLK Ref 1489 softwaredatasheet*/

MX8MM_IOMUXC_ENET_TD1_ENET1_RGMII_TD1 0x1f

MX8MM_IOMUXC_ENET_TD0_ENET1_RGMII_TD0 0x1f

MX8MM_IOMUXC_ENET_RD3_ENET1_RGMII_RD3 0x91

MX8MM_IOMUXC_ENET_RD2_ENET1_RGMII_RD2 0x91

MX8MM_IOMUXC_ENET_RD1_ENET1_RGMII_RD1 0x91

MX8MM_IOMUXC_ENET_RD0_ENET1_RGMII_RD0 0x91

MX8MM_IOMUXC_ENET_TXC_ENET1_RGMII_TXC 0x1f

MX8MM_IOMUXC_ENET_RXC_ENET1_RGMII_RXC 0x91

MX8MM_IOMUXC_ENET_RX_CTL_ENET1_RGMII_RX_CTL 0x91

MX8MM_IOMUXC_ENET_TX_CTL_ENET1_RGMII_TX_CTL 0x1f

/*MX8MM_IOMUXC_SAI2_RXC_GPIO4_IO22 0x19*/ /*Use this for NXP EVK - Commented by santhosh */

MX8MM_IOMUXC_GPIO1_IO08_GPIO1_IO8 0x19 /*LVDS board RESET_ETH*/

>;

};

--------------------------------------------------------------------------------------------------------------------------

2. in imx8mm_evk.h the changes is as below

--------------------------------------------------------------------------------------------------------------------------

#define CONFIG_ETHPRIME "FEC"

/* Configuration for RMII*/

#define CONFIG_FEC_MXC

#define FEC_QUIRK_ENET_MAC

#define IMX_FEC_BASE 0x30BE0000

#define CONFIG_PHYLIB

#define CONFIG_FEC_XCV_TYPE RMII

/*#define CONFIG_PHY_REALTEK*/

#define CONFIG_PHY_NATSEMI

#define CONFIG_FEC_MXC_PHYADDR 0//3

#define CONFIG_NET_RANDOM_ETHADDR

#if 0

#define CONFIG_FEC_MXC

#define CONFIG_FEC_XCV_TYPE RGMII

#define CONFIG_FEC_MXC_PHYADDR 0

#define FEC_QUIRK_ENET_MAC

#define CONFIG_PHY_GIGE

#define IMX_FEC_BASE 0x30BE0000

#define CONFIG_PHYLIB

#define CONFIG_PHY_ATHEROS

#endif

#endif

--------------------------------------------------------------------------------------------------------------------------

3. In imx8mm_evk.c made the chage as below

--------------------------------------------------------------------------------------------------------------------------

static int setup_fec(void)

{

debug("LVDS:setup_fec\n");

struct iomuxc_gpr_base_regs *const iomuxc_gpr_regs

= (struct iomuxc_gpr_base_regs *) IOMUXC_GPR_BASE_ADDR;

/*

* GPR1 bit 13:

* 1:enet1 rmii clock comes from ccm->pad->loopback, SION bit for the pad (iomuxc_sw_input_on_pad_enet_td2) should be set also;

* 0:enet1 rmii clock comes from external phy or osc

*/

// added by santhosh for RMII mode for LVDS hardware board

#if 1

debug("setup_fec\n");

setbits_le32(&iomuxc_gpr_regs->gpr[1],

//IOMUXC_GPR_GPR1_GPR_ENET1_TX_CLK_SEL_SHIFT); //working

IOMUXC_GPR_GPR1_GPR_ENET1_TX_CLK_SEL_MASK); //working

return set_clk_enet(ENET_50MHZ); //

#endif

// RGMII mode Commented by santhosh

#if 0

setup_iomux_fec();

/* Use 125M anatop REF_CLK1 for ENET1, not from external */

clrsetbits_le32(&iomuxc_gpr_regs->gpr[1],

IOMUXC_GPR_GPR1_GPR_ENET1_TX_CLK_SEL_SHIFT, 0);

return set_clk_enet(ENET_125MHZ);

#endif

}

--------------------------------------------------------------------------------------------------------------------------

This are the changes done and in uboot i am doing

setenv ipaddr 192.168.36.126

setenv serverip 192.168.36.101

setenv netmask 255.255.255.0

setenv gatewayip 192.168.36.1

setenv ethaddr 10:7d:1a:43:21:0c

setenv ethact ethernet@30be0000

setenv ethprime FEC

saveenv

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Adding Still More details

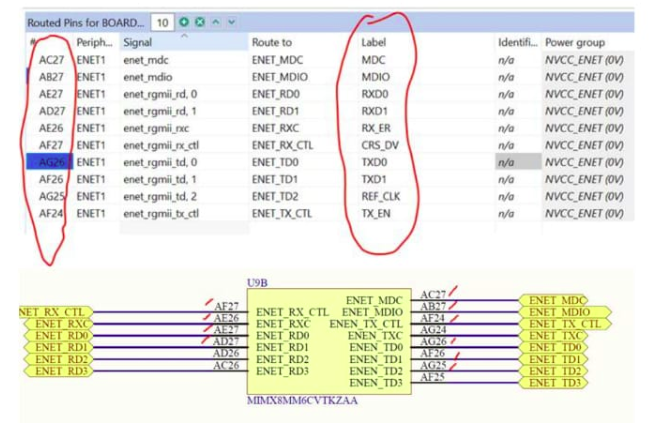

This the Pin configuration used for RMII Mode and

Is the ENET_TD2 - REF_CLK the connection is required or should it be a No connection

Connection of DP83848 with IMX8MM processor and We have used 50 MHz external osc clock for DP83848

Why is the Processor not putting the data on the TXD Line. The Auto negotiate is getting completed and able to read the PHY IC register

u-boot=> mii read 0 0-1d

addr=00 reg=00 data=3100

addr=00 reg=01 data=786D

addr=00 reg=02 data=2000

addr=00 reg=03 data=5C90

addr=00 reg=04 data=01E1

addr=00 reg=05 data=CDE1

addr=00 reg=06 data=000D

addr=00 reg=07 data=2801

addr=00 reg=08 data=0000

addr=00 reg=09 data=0000

addr=00 reg=0a data=0000

addr=00 reg=0b data=0000

addr=00 reg=0c data=0000

addr=00 reg=0d data=0000

addr=00 reg=0e data=0000

addr=00 reg=0f data=0000

addr=00 reg=10 data=0615

addr=00 reg=11 data=0000

addr=00 reg=12 data=0000

addr=00 reg=13 data=0000

addr=00 reg=14 data=0000

addr=00 reg=15 data=0000

addr=00 reg=16 data=0100

addr=00 reg=17 data=0021

addr=00 reg=18 data=0000

addr=00 reg=19 data=8020

addr=00 reg=1a data=0904

addr=00 reg=1b data=0000

addr=00 reg=1c data=0000

addr=00 reg=1d data=6011

Do advice any further test or experiment you want us to do

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

what is the fec1 setting on your dts file?