- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- SDK - how to config ADC input pin/channel ?

SDK - how to config ADC input pin/channel ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SDK - how to config ADC input pin/channel ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am looking for an example to proper initialize an input channel for the ADC (LPC54628).

The usual way is to enable the appropriate GPIO pin, and assign the proper function (analog mode).

All of the SDK examples use the internal temperature sensor - and cleverly circumvent a proper how-to.

Can any one show me the proper SDK calls, and sequence ?

I want to use ADC0 and ADC0IN4..6, but an example for one pin/channel would suffice.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello frank meyer,

Please refer to the below application, it use channel 4, download from:

https://www.nxp.com/docs/en/application-note/TN00017.zip

It includes application notes and source code, this project support MCUXpresso IDE, IAR and KEIL.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thinking about it, I finally came to realize the SDK is not a library designed as such to work with a certain MCU.

Instead, it is auto-generated from a config tool, using a loose set of peripheral drivers (fsl_xxx.c/.h), device-specific files, and middleware utilitites.

I'm probably supposed to use the ConfigTool in the MCUXpresso IDE instead.

I'm going to look into it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Frank,

Yes, I also recommend you use MCUXpresso Config tool.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Since it belongs to the topic, I'd like to ask a follow-up question.

I have configured 3 channels with a sequenceA interrupt, which basically works.

However, my interrupt handler routine proved incorrect.

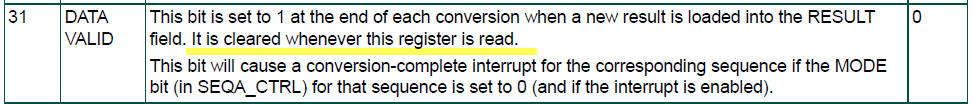

Section 44.6.5, table 1032 (page 1049) of UM10912 says:

SEQA_GDAT register, Bit 31: DATA VALID

This bit is set to 1 at the end of each conversion when a new result is loaded into the RESULT field. It is cleared whenever this register is read.

This bit will cause a conversion-complete interrupt for the corresponding sequence if the MODE bit (in SEQA_CTRL) for that sequence is set to 0 (and if the interrupt is enabled).

Thus, I checked for the DATA_VALID bit of said register, which was never set.

Consequently, the code never cleared any flags, and the interrupt fired continuously.

I then checked the SDK example code (from TN00017), and the ADC interrupt handler code there goes for the ADC.FLAGS register instead.

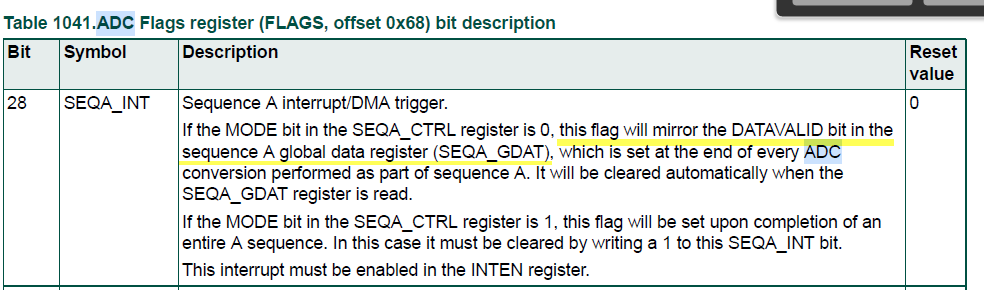

Again quoting the relevant part of the user manual,Section 44.6.11, table 1041 (page 1078):

Bit 28: SEQA_INT

Sequence A interrupt/DMA trigger.

If the MODE bit in the SEQA_CTRL register is 0, this flag will mirror the DATAVALID bit in the sequence A global data register (SEQA_GDAT), which is set at the end of every ADC conversion performed as part of sequence A. It will be cleared automatically when the SEQA_GDAT register is read.

If the MODE bit in the SEQA_CTRL register is 1, this flag will be set upon completion of an entire A sequence. In this case it must be cleared by writing a 1 to this SEQA_INT bit. This interrupt must be enabled in the INTEN register.

The MODE bit of SEQA_CTRL is set (as I configured).

I basically copied this code (check for FLAGS.SEQA_INT flag instead of SEQA_GDAT.DATA_VALID), which works as expected.

However, I cannot find any indication in the UM why the DATA_VALID bit in SEQA_GDAT is not set at the same time. Do I miss something ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello frank,

From the below information of UM, DATAVALID will be cleared whenever it is read, and the SEQA_INT

mirror the DATAVALID bit, meaning read it, so it is 0.

And in almost case, please use flags to check whether finish conversion.

BR

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From the below information of UM, DATAVALID will be cleared whenever it is read, and the SEQA_INT

mirror the DATAVALID bit, meaning read it, so it is 0.

I have read it, and understood (at least, I think). And I'm aware of debugger intrusiveness in this case.

My first line in the ADC interrupt handler translated to something like :

if (ADC0->SEQ_GDAT[0] & 0x80000000) { ...

This condition was never fulfilled. I didn't have a peripheral register debug view open at that time, and this was supposedly the first (read) access.

Anyway, the FLAG register based code works.

Not to be too nitpicking, but albeit the UM differs between SEQA_GDAT and SEQB_GDAT, the SDK code (fsl_adc.*) knows only SEQ_GDAT[2].

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello frank,

So the SDK code is an important supplement .:smileywink:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So the SDK code is an important supplement .

Understand and agree ... ;-)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, that should work for me.

Albeit it is a bit convoluted - I expected the GPIO configuration in the ADC init context, but instead it is "hidden" in the one-for-all pin_mux module.