- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- [iMX8MM] Change UART console

[iMX8MM] Change UART console

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

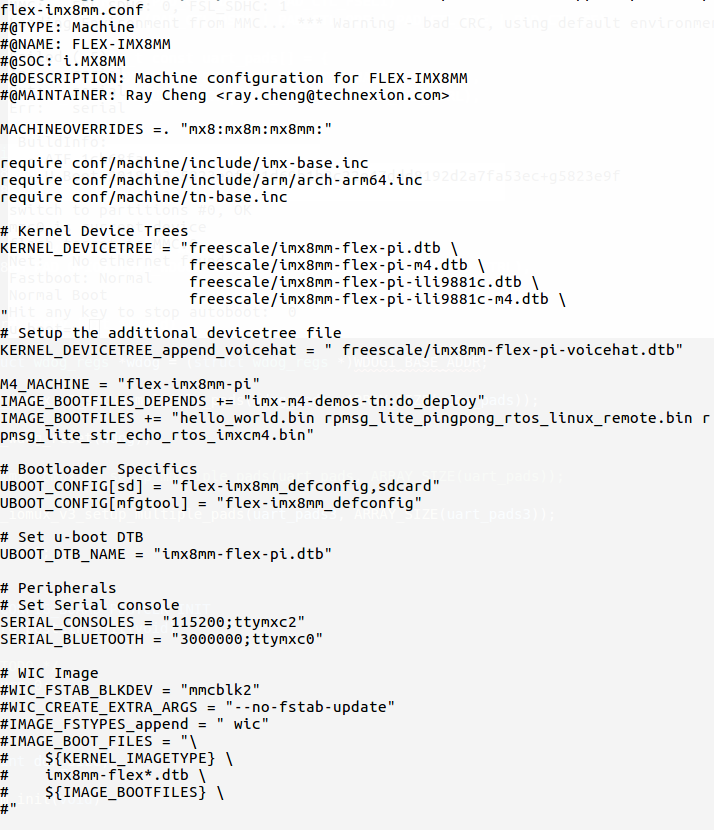

I'm using flex-imx8mm

I want to change console from UART 2 -> UART 3. I changed it in the u-boot, but I can't start kernel.

Please help me. Thanks you

[UPDATE]

Change 0x30890000 to 0x30880000

"console=ttymxc2,115200 earlycon=ec_imx6q,0x30880000,115200\0" \

u-Boot change:

- DTB

chosen {

bootargs = "console=ttymxc2,115200 earlycon=ec_imx6q,0x30890000,115200";

stdout-path = &uart3;

};

- include/configs

#define CONFIG_EXTRA_ENV_SETTINGS \

CONFIG_MFG_ENV_SETTINGS \

M4_BOOT_ENV \

JAILHOUSE_ENV \

"script=boot.scr\0" \

"image=Image\0" \

"console=ttymxc2,115200 earlycon=ec_imx6q,0x30890000,115200\0" \

"fdt_addr=0x43000000\0" \

"fdt_high=0xffffffffffffffff\0" \

"boot_fdt=try\0" \

"fdt_file=undefined\0" \

"initrd_addr=0x43800000\0" \

"initrd_high=0xffffffffffffffff\0" \....

#define CONFIG_MXC_UART

#define CONFIG_MXC_UART_BASE UART3_BASE_ADDR

Result:

U-Boot SPL 2018.03-g5823e9f-dirty (May 19 2020 - 14:45:59 +0700)

power_bd71837_init

dram_init: LPDDR4: 2GB

DDRINFO: start lpddr4 ddr init

DRAM PHY training for 3000MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 3000MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 400MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DRAM PHY training for 100MTS

check ddr4_pmu_train_imem code

check ddr4_pmu_train_imem code pass

check ddr4_pmu_train_dmem code

check ddr4_pmu_train_dmem code pass

Training PASS

DDRINFO:ddrphy calibration done

DDRINFO: ddrmix config done

Normal Boot

Trying to boot from MMC1

U-Boot 2018.03-g5823e9f-dirty (May 19 2020 - 14:45:59 +0700)CPU: Freescale i.MX8MMQ rev1.0 1800 MHz (running at 1200 MHz)

CPU: Commercial temperature grade (0C to 95C) at 51C

Reset cause: POR

Model: TechNexion FLEX-IMX8MM and FLEX-PI baseboard

DRAM: 2 GiB

MMC: FSL_SDHC: 0, FSL_SDHC: 1

Loading Environment from MMC... OK

In: serial

Out: serial

Err: serialBuildInfo:

- ATF 1cb68fa

- U-Boot 2018.03-g5823e9f-dirtyswitch to partitions #0, OK

mmc0 is current device

flash target is MMC:0

Net: No ethernet found.

Fastboot: Normal

Normal Boot

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0 is current device

** Unable to read file boot.scr **

** Unable to read file tnrescue.itb **

18108928 bytes read in 780 ms (22.1 MiB/s)

** Unable to read file m4.bin **

Booting from mmc ...

42993 bytes read in 17 ms (2.4 MiB/s)

## Flattened Device Tree blob at 43000000

Booting using the fdt blob at 0x43000000

Using Device Tree in place at 0000000043000000, end 000000004300d7f0Starting kernel ...

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I fixed

"console=ttymxc2,115200 earlycon=ec_imx6q,0x30880000,115200\0" \

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I fixed

"console=ttymxc2,115200 earlycon=ec_imx6q,0x30880000,115200\0" \

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi kat61545@eoopy.com,

Are you using the Yocto build system to generate the images?

If so then, you also need to change the value of the "SERIAL_CONSOLES" variable in the machine configuration file in yocto build. You need to assign ttymxc2 to the SERIAL_CONSOLES variable as well.

e.g. SERIAL_CONSOLES = "115200;ttymxc2"

Hope this will help you.

Regards,

Shivani

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Shivani Patel wrote:

Hi Oliver Vu,

Are you using the Yocto build system to generate the images?

If so then, you also need to change the value of the "SERIAL_CONSOLES" variable in the machine configuration file in yocto build. You need to assign ttymxc2 to the SERIAL_CONSOLES variable as well.

e.g. SERIAL_CONSOLES = "115200;ttymxc2"

Hope this will help you.

Regards,

Shivani

Thanks for response.

I tried it, but it didn't show in the uart3 (ttymxc2)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"

from dtb, uart3 should be tty2,

serial0 = &uart1;

serial1 = &uart2;

serial2 = &uart3;

serial3 = &uart4;

test /dev/ttymxc2 with cmd:

/unit_test/UART/mxc_uart_xmit_test.out /dev/ttymxc2 -B 9600

"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks, but I do not understand your answer

line 156: Modify

"console=ttymxc1,115200 earlycon=ec_imx6q,0x30890000,115200\0" \

->

"console=ttymxc2,115200 earlycon=ec_imx6q,0x30890000,115200\0" \

line 279: Modify

#define CONFIG_MXC_UART_BASE UART2_BASE_ADDR

->

#define CONFIG_MXC_UART_BASE UART3_BASE_ADDR

line 45: Add

static iomux_v3_cfg_t const uart_pads3[] = {

IMX8MM_PAD_ECSPI1_SCLK_UART3_RX | MUX_PAD_CTRL(UART_PAD_CTRL),

IMX8MM_PAD_ECSPI1_MOSI_UART3_TX | MUX_PAD_CTRL(UART_PAD_CTRL),

};

line 58: Modify

imx_iomux_v3_setup_multiple_pads(uart_pads, ARRAY_SIZE(uart_pads));

->

imx_iomux_v3_setup_multiple_pads(uart_pads3, ARRAY_SIZE(uart_pads3));

line 25: Modify

bootargs = "console=ttymxc1,115200 earlycon=ec_imx6q,0x30890000,115200";

stdout-path = &uart2;

->

bootargs = "console=ttymxc2,115200 earlycon=ec_imx6q,0x30890000,115200";

stdout-path = &uart3;

This is my change. I stuck at "Starting kernel ..."