- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- About the behavior when buffer underflow happen in LCDIF

About the behavior when buffer underflow happen in LCDIF

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

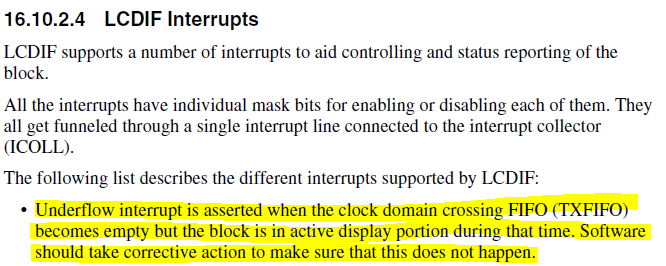

From IMX8DQXPRM.pdf (Rev.0):

We will use the LCDIF in DOTCLK mode for display output.

Please let me confirm the behavior when buffer underflow happened case.

Q1. When buffer underflow is happened, the underflow interrupt is asserted by LCDIF.

In this case, I will control following steps. Is it right?

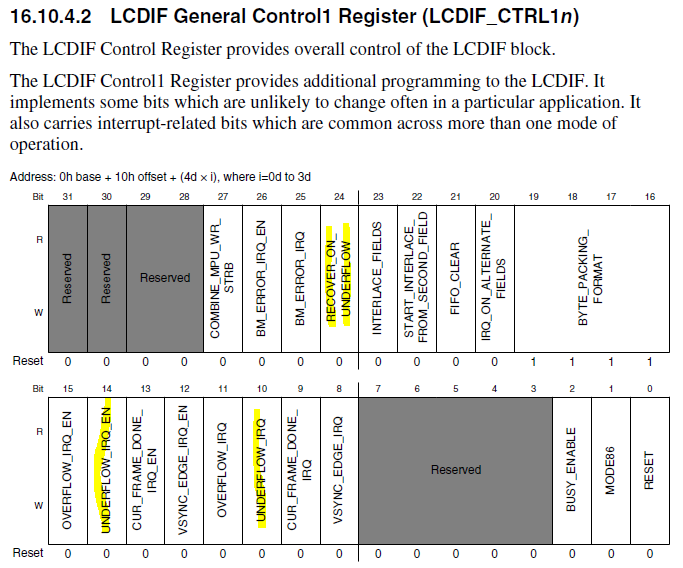

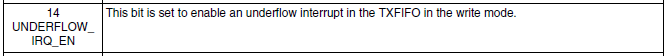

(1) LCDIF_CTRL1n[UNDERFLOW_IRQ_EN] set to 1b to enable underflow interrupt.

<buffer underflow happened>

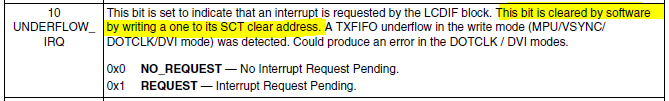

(2) Interrupt handler check LCDIF_CTRL1n[UNDERFLOW_IRQ] to confirm kind of interrupt.

(3) Interrupt handler set to 1b to SCT clear address to clear the underflow interrupt.

(4) Interrupt handler set to 1b to LCDIF_CTRL1n[RECOVER_ON_UNDERFLOW] to recover underflow condition.

Q2. SCT clear address is where? I could not find suitable register in RM. What does SCT mean?

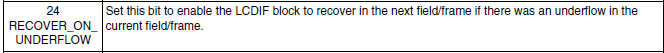

Q3. What is the feature of LCDIF_CTRL1n[RECOVER_ON_UNDERFLOW]?

Best Regards,

Kazuma Sasaki.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kazuma Sasaki,

Q1

I have reviewed your proposal with my colleagues. The steps seem right, but, our recommendation is that you include the enable of the RECOVER bit in the initialization because if an underflow state is detected and this bit is ON, the information will recover to the next frame.

Q2

As an extract from our Reference Manual, 14.11.4 Register Macro Usage, page 4321.

They are registers that can be used to either SET, CLEAR, or TOGGLE (SCT).

When writing to an SCT register, all bits set to 1 perform the associated operation on the primary register, while all bits set to 0 are not affected.

Related to LCDIF_CTRL1n[UNDERFLOW_IRQ] to clear the interrupt flag by writing a one to its SCT clear address, at page 7782 (LCDIF memory map) there are registers as LCDIF_CTRL1_SET, LCDIF_CTRL1_CLR and LCDIF_CTRL1_TOG corresponding to SCT (SET, CLEAR, TOGGLE).

Q3

Related to LCDIF_CTRL1n[RECOVER_ON_UNDERFLOW] .

This bit is related to FIFO of LCDIF. It means, if FIFO is full with the current field/frame (in underflow state) and if this bit is enabled, at the next frame the information of FIFO will load again.

Best regards,

Luis Perez.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Kazuma Sasaki,

Q1

I have reviewed your proposal with my colleagues. The steps seem right, but, our recommendation is that you include the enable of the RECOVER bit in the initialization because if an underflow state is detected and this bit is ON, the information will recover to the next frame.

Q2

As an extract from our Reference Manual, 14.11.4 Register Macro Usage, page 4321.

They are registers that can be used to either SET, CLEAR, or TOGGLE (SCT).

When writing to an SCT register, all bits set to 1 perform the associated operation on the primary register, while all bits set to 0 are not affected.

Related to LCDIF_CTRL1n[UNDERFLOW_IRQ] to clear the interrupt flag by writing a one to its SCT clear address, at page 7782 (LCDIF memory map) there are registers as LCDIF_CTRL1_SET, LCDIF_CTRL1_CLR and LCDIF_CTRL1_TOG corresponding to SCT (SET, CLEAR, TOGGLE).

Q3

Related to LCDIF_CTRL1n[RECOVER_ON_UNDERFLOW] .

This bit is related to FIFO of LCDIF. It means, if FIFO is full with the current field/frame (in underflow state) and if this bit is enabled, at the next frame the information of FIFO will load again.

Best regards,

Luis Perez.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Luis,

I appreciate your support. I got it.

Best Regards,

Kazuma Sasaki.