- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- The SJA1105 doesn`t woke well

The SJA1105 doesn`t woke well

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI

My SJA1105T can`t work normal,i need some help.

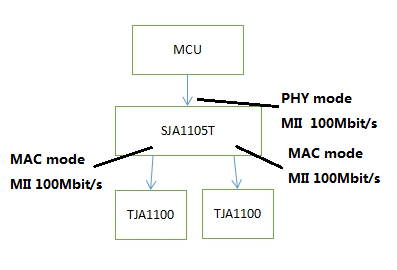

I had detect signals at TXD[0:3] from MCU to SWITCH, but i can`t detect signals at TXD[0:3] from SWITCH to PHY.

I had get some information from Software user manual for SJA1105TEL .

I read the Initial device configuration flag register ,it shows the configuration is valid.

I read the Ethernet high-level port status diagnostic counters part 1 ,the N_RXFRM \N_RXFRMSH \N_TXFRM\ N_TXFRMSH which show the tx/rx frames counter is always 0.

why?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If N_RXFRM doesn't change when you send traffic to the corresponding

port, it means the port is unable to detect a proper frame. This in

turn may happen due to wrong timing of the MII interface signals or

because the port is improperly or not fully configured. Suggestions:

1. Check error counters and flags described in UM10944, Section 5.1.4.1

2. Make sure CGU and ACU are properly configured for the used interface

type. Note that this configuration is not part of the static configuration

sequence. See AH1601 for more details, the document is available

on Docstore.

Have a great day,

Platon

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If N_RXFRM doesn't change when you send traffic to the corresponding

port, it means the port is unable to detect a proper frame. This in

turn may happen due to wrong timing of the MII interface signals or

because the port is improperly or not fully configured. Suggestions:

1. Check error counters and flags described in UM10944, Section 5.1.4.1

2. Make sure CGU and ACU are properly configured for the used interface

type. Note that this configuration is not part of the static configuration

sequence. See AH1601 for more details, the document is available

on Docstore.

Have a great day,

Platon

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- I read the Section 5.1.4.1, Ethernet port status - MAC-level diagnostic counters,the field N_SOFERR is0x04.

and the Ethernet port status - diagnostic flags is all 0, I don`t know what this means.

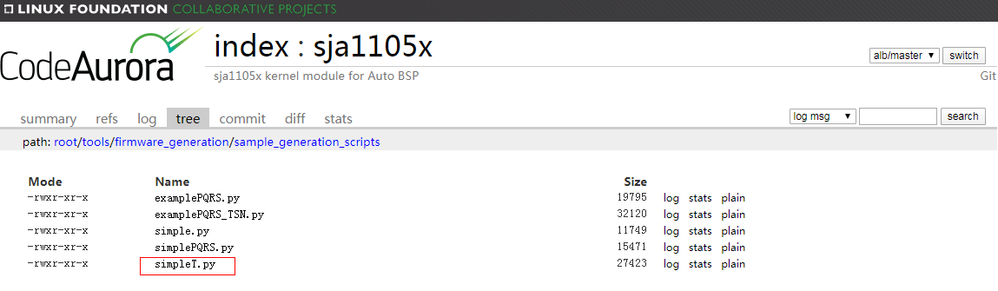

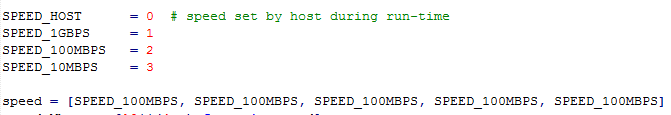

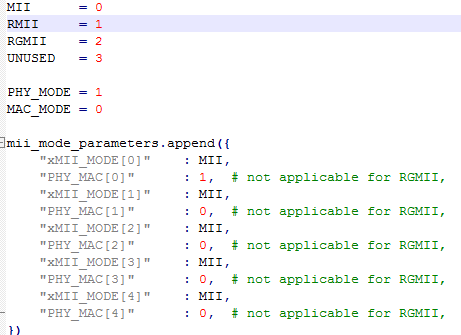

2.The static configuration sequence, I get from simpleT.py, and It's been modified a little bit to match my board

- the CGU is configured like this, I had compared it with the corresponding part in AH1601, I am sure it`s right.

//MII CLOCK FOR PORT0 (PHY)

static const uint8_t port0_idiv0[] = {0x01|0x80,0x00,0x00,0xb0,0x0a,0x00,0x00,0x00};

static const uint8_t port0_mii_tx_clk[] = {0x01|0x80,0x00,0x01,0x30,0x11,0x00,0x08,0x00};

static const uint8_t port0_mii_rx_clk[] = {0x01|0x80,0x00,0x01,0x40,0x01,0x00,0x08,0x00};

static const uint8_t port0_ext_tx_clk[] = {0x01|0x80,0x00,0x01,0x80,0x11,0x00,0x08,0x00};

static const uint8_t port0_ext_rx_clk[] = {0x01|0x80,0x00,0x01,0x90,0x11,0x00,0x08,0x00};

//MII CLOCK FOR PORT1 (MAC)

static const uint8_t port1_idiv1[] = {0x01|0x80,0x00,0x00,0xc0,0x0a,0x00,0x00,0x01};

static const uint8_t port1_mii_tx_clk[] = {0x01|0x80,0x00,0x01,0xa0,0x02,0x00,0x08,0x00};

static const uint8_t port1_mii_rx_clk[] = {0x01|0x80,0x00,0x01,0xb0,0x03,0x00,0x08,0x00};

//MII CLOCK FOR PORT2 (MAC)

static const uint8_t port2_idiv2[] = {0x01|0x80,0x00,0x00,0xd0,0x0a,0x00,0x00,0x01};

static const uint8_t port2_mii_tx_clk[] = {0x01|0x80,0x00,0x02,0x10,0x04,0x00,0x08,0x00};

static const uint8_t port2_mii_rx_clk[] = {0x01|0x80,0x00,0x02,0x20,0x05,0x00,0x08,0x00};

//MII CLOCK FOR PORT0 (MAC)

static const uint8_t port3_idiv3[] = {0x01|0x80,0x00,0x00,0xe0,0x0a,0x00,0x00,0x01};

static const uint8_t port3_mii_tx_clk[] = {0x01|0x80,0x00,0x02,0x80,0x06,0x00,0x08,0x00};

static const uint8_t port3_mii_rx_clk[] = {0x01|0x80,0x00,0x02,0x90,0x07,0x00,0x08,0x00};

//MII CLOCK FOR PORT0 (MAC)

static const uint8_t port4_idiv4[] = {0x01|0x80,0x00,0x00,0xf0,0x0a,0x00,0x00,0x01};

static const uint8_t port4_mii_tx_clk[] = {0x01|0x80,0x00,0x02,0xf0,0x08,0x00,0x08,0x00};

static const uint8_t port4_mii_rx_clk[] = {0x01|0x80,0x00,0x03,0x00,0x09,0x00,0x08,0x00};

4.The ACU part

/* Configure CFG_PAD_MII0_RX[CLK_IPUD], Pull down MII0_RX_ER */

static uint8_t tmp[8] = {0x01|0x80,0x00,0x80,0x10,0x02,0x02,0x03,0x12};

If you find any problems,i will really appreciate.