- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Assigning pins for DMIC2 on RT595

Assigning pins for DMIC2 on RT595

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Assigning pins for DMIC2 on RT595

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm trying to assign pins for two microphones on RT595.

One of them is using DMIC0, using function #4, on pins 5_4 (CLK01) and 5_8 (DATA01)

The other one, I'm having trouble with.

According to the pin function table that I have:

PDM_CLK23 is on 3_1 with function #1

PDM_DATA23 is also on 3_1 with function #2

Also, CLK and DATA are on 3_2 for DMIC45, and on 3_3 for DMIC67.

So, whatever the channel (2 to 7), CLK and DATA are on the same pin. I don't see how I can have separate pins.

Am I misunderstanding something? Or is my pin function table wrong? Is there an official table somewhere? the table that I got was passed along by a colleague.

Thank you.

d.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello damien saint macary,

After checking with our expert, they told me that : we do support 8 DMIC channels, but only one clock is required in order to accomplish this.

Just like the RM NOTE:In order to output 8 channels of PDM Data, PDM_CLK01 must be used.

You also can refer to our:

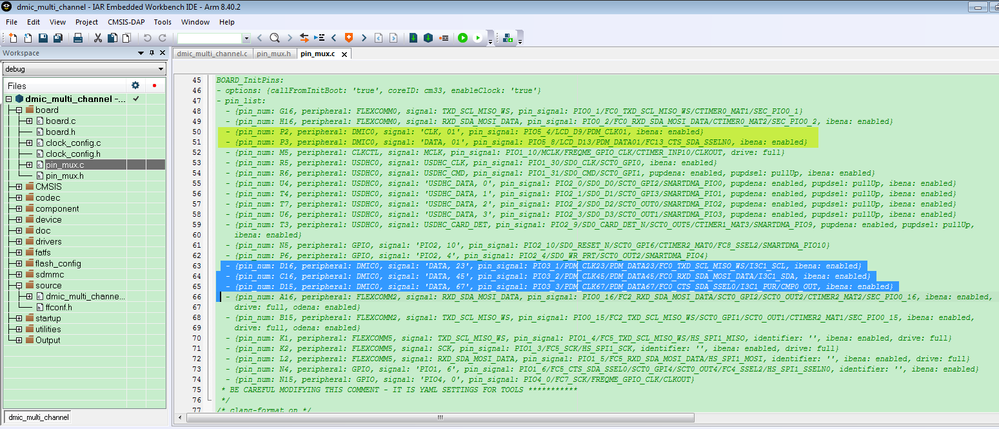

SDK_2.6.2_EVK-MIMXRT595\boards\evkmimxrt595\driver_examples\dmic\dmic_multi_channel

You can find in the pinmux.c

just configure CLK01, other is the DATA pins.

This project use the DMIC multi-channel to gathering audio data with DMA.

So you can refer to the SDK example find more details.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the information Kerry,

I was having issue with one of the microphones.

The right microphone was working fine (connected to PDM_CLK01 and PDM_DATA01).

The left microphone however was not working (connected to PDM_CLK23 and PDM_DATA45).

I was using DMIC channel 4. I finally managed to fix it today, but I wanted to doublecheck that I was doing the right thing.

I was calling DMIC_EnableChannel(DMIC0, 1 << 4)

I changed it to DMIC_EnableChannel(DMIC0, 1 << 2)

basically enabling channel 2 instead of 4, because my clock is on PDM_CLK23.

This has apparently fixed my microphone.

Is it the right approach? Is DMIC_EnableChannel() used to effectively select the pins that would carry the clock?

Also, is DMIC_EnableChannel() used to also disable the channel? I tried doing DMIC_EnableChannel(DMIC, 0), but I was still able to record audio after that.

Thank you.

d.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What's the board you are using? NXP official board MIMXRT685-EVK? Do you modify the hardware side from PDM_CLK01 and PDM_DATA01 to PDM_CLK23 and PDM_DATA45?

If you are using the NXP official board, please tell me your detail hardware modification points.

And also upload you modified project, I will help you to check more details.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using the RT595 chip directly, not the EVK.

Let me describe the setup:

The left microphone is connected to PIO3_1 for the clock and PIO3_2 for the data.

PIO3_1 is configured as function 1: PDM_CLK23

PIO3_2 is configured as function 2: PDM_DATA45

The right microphone is connected to PIO5_4 for the clock and PIO5_8 for the data.

PIO5_4 is configured as function 4: PDM_CLK01

PIO5_8 is configured as function 4: PDM_DATA01

Here's how I configure them both:

DMIC_Init(DMIC0);

DMIC_SetIOCFG(DMIC0, kDMIC_PdmDual);

DMIC_Use2fs(DMIC0, false);

DMA_Init(DMA0);

DMIC_EnableChannel(DMIC0, (1<<0) | (1 << 2)); // using channel 2 instead of 4 here

dmic_channel_config_t cfg;

cfg.divhfclk = kDMIC_PdmDiv1;

cfg.osr = 100;

cfg.gainshft = 0;

cfg.preac2coef = kDMIC_CompValueZero;

cfg.dc_cut_level = kDMIC_DcCut39;

cfg.post_dc_gain_reduce = 0;

cfg.saturate16bit = 1;

cfg.sample_rate = kDMIC_PhyFullSpeed;

// Left

DMIC_EnableChannelDma(DMIC0, 4, true);

DMIC_ConfigChannel(DMIC0, 4, kDMIC_Left, &cfg);

DMIC_FifoChannel(DMIC0, 4, 15, true, true);

DMA_EnableChannel(DMA0, 4);

DMA_CreateHandle(&handle_rx_left, DMA0, 4);

DMIC_TransferCreateHandleDMA(DMIC0, &handle_left, callback, NULL, &handle_rx_left);

// Right

DMIC_EnableChannelDma(DMIC0, 0, true);

DMIC_ConfigChannel(DMIC0, 0, kDMIC_Left, &cfg);

DMIC_FifoChannel(DMIC0, 0, 15, true, true);

DMA_EnableChannel(DMA0, 0);

DMA_CreateHandle(&handle_rx_right, DMA0, 0);

DMIC_TransferCreateHandleDMA(DMIC0, &handle_right, callback, NULL, &handle_rx_right);

Again, it's working for me now, just want to make sure I'm doing the right thing, especially w.r.t the call to DMIC_EnableChannel().

d.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

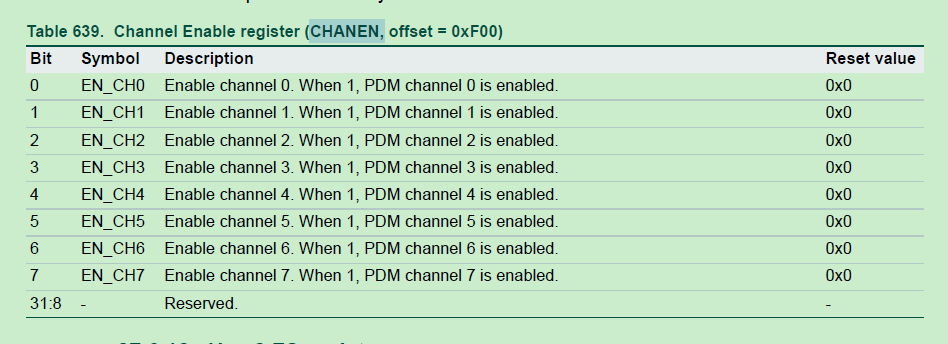

I checked the SDK code, the DMIC_EnableChannnel which you mentioned:

void DMIC_EnableChannnel(DMIC_Type *base, uint32_t channelmask)

{

base->CHANEN |= channelmask;

}

I think your configuration is correct.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Kerry.

Just to clarify then, I will summarize with this statement:

DMIC_EnableChannel() will enable the PDM clock pins for the corresponding channels, not to be confused with the channel the PDM data will be received from.

regards,

d.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are welcome!

If you have any questions in the future, welcome to create the new question post.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your interest in the NXP MIMXRT product, I would like to provide service for you.

RT595 is really very new, I still don't have the RM and DS on my side which isn't shared in the nxp website, so I need to find it internally.

Could you please tell me all the DMIC pins you want to use, then I will help you to check details after I get the related document.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Thank you for your reply.

I have been asking around and a colleague that had the same question explained to me.

On the RT595, the 8 DMIC channels share the same clock. Although they are labeled PDM_CLK01, CLK23, CLK45 and CLK67, it is irrelevant which one we use for any channel. So, for channel 2, we use PDM_DATA23 on 3_1 and PDM_CLK45 on 3_2 which is just next to it.

Let me know if my understanding is wrong.

d.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just got the internal RM today, sorry for the later reply.

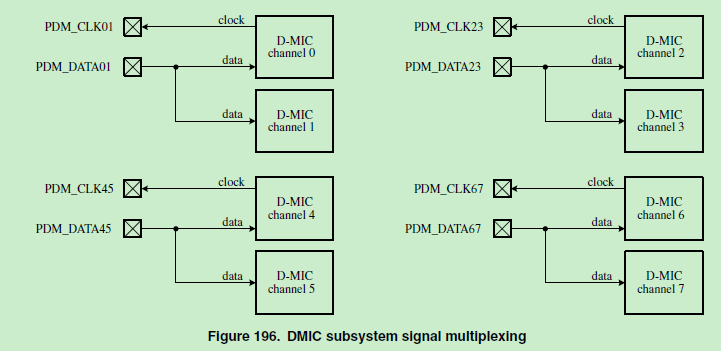

I don't think the 8 DMIC share the same clock, please check the RM picture:

The clock is still separated for the different paring channel.

Do you want to use all the 8 channels at the same time?

Anyway, I will help you double check with our internal side about the same pin question.

After I get the reply, I will let you know.

Please keep the patient, thanks.

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------