- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- S32K

- :

- S32K144 CAN Bus Masking And Filtering?

S32K144 CAN Bus Masking And Filtering?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I want to communicate with many S32K144EVB through FlexCAN. I found a main.c file in which they have done the same thing, but i am not able to understand why he took

/*-----------ID Filter table-----------------*/

flexcan_id_table_t filterTable[16]={};

uint16_t IDlist[16] = {0x402,0x403,0x404,0x408,0x410,0x420,0x430,0x440,0x448,0x449,0x44A,0x44B,0x44C,0x44F,0x450,0};

uint16_t IDmask[10] = {0x7FF,0x7FF,0x7FC,0x7F8,0x7F0,0x7F0,0x7F0,0x7F8,0x7FF,0x7FF};

means he took filter array having 16 filter id, but the masking array only RXIMR0-RXIMR9

please assist me.

we have RXIMR0-RXIMR63, so why should we didn`t use 16 for 16 filter id.

PS:- Also attaching main.c file for the reference.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

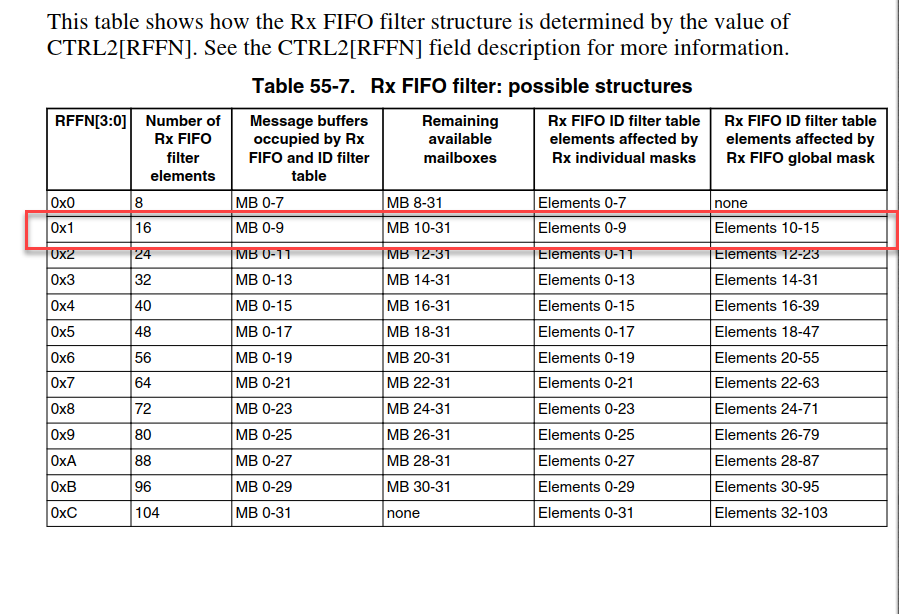

below table gives a summary how many ID filter Table elements are affected by RXIMR and RXFGMASK registers.

So if 16 filter elements are selected then first 10 are affected by individual mask registers RXIMR0-RXIMR9 and teh rest by RX|FIFO global mask RXFGMASK.

BB, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

below table gives a summary how many ID filter Table elements are affected by RXIMR and RXFGMASK registers.

So if 16 filter elements are selected then first 10 are affected by individual mask registers RXIMR0-RXIMR9 and teh rest by RX|FIFO global mask RXFGMASK.

BB, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

flexcan_id_table_t filterTable[16]={};

uint16_t IDlist[16] = {0x402,0x403,0x404,0x408,0x410,0x420,0x430,0x440,0x448,0x449,0x44A,0x44B,0x44C,0x44F,0x450,0};

uint16_t IDmask[10] = {0x7FF,0x7FF,0x7FC,0x7F8,0x7F0,0x7F0,0x7F0,0x7F8,0x7FF,0x7FF};

My another doubt is why we are taking 0x7FC,0x7F8,0x7F0,0x7F0,0x7F0,0x7F8 in IDmask we should take all with 0x7FF?

I am not getting this. PetrS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

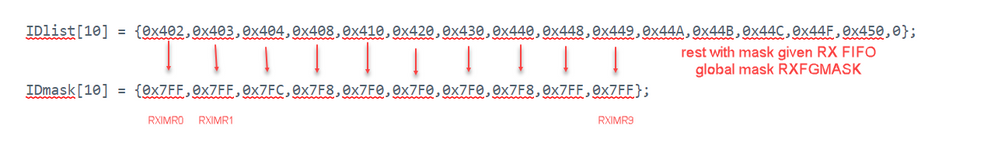

ID ranges are used, so less number of ID elements is needed. For example

0x404 is masked with 0x7FC thus lower 2 bits are don't care, so messages with ID 0x404-0x407 are received

0x420 is masked with 0x7F0 thus lower 4 bits are don't care, so messages with ID 0x420-0x42F are received

and so on

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for this detail, i understood this point but just a last query, how did you/ (or the MCU will know) find which ID is masked with whom?

like 0x404 is masked with 0x7FC and 0x420 is masked with 0x7F0 so, 0x450 is masked with whom?

PetrS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

from the chapter 55.4.2.18.2 of the RM

When the Rx FIFO is enabled (MCR[RFEN] bit is asserted), an individual mask is provided for each Rx FIFO ID filter table element on a one-to-one correspondence depending on the setting of CTRL2[RFFN] (see Rx FIFO).

RXIMR0 stores the individual mask associated with either MB0 or ID filter table element 0, RXIMR1 stores the individual mask associated with either MB1 or ID filter table element 1, and so on.

And in a code IDmask[x] is assigned to RXIMRx register,where x is integer in range 0 to 9.

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

so that means

0x402 0x7FF

0x403 0x7FF

0x404 0x7FC

0x408 0x7F8

0x410

0x420

0x430

0x440

0x448,

0x449, 0x7FF and so on till 0x449

so what about below ID.

0x44A,

0x44B,

0x44C,

0x44F,

0x450,

0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for this image, I completely understood this.

I just have one confusion,

Kindly take a reference of S32K-RM pdf

Page No- 1847

------------------------------------------------------------------------------------------------------------------

55.4.2.18.2 Function

The RX Individual Mask Registers are used to store the acceptance masks for ID filtering

in Rx MBs and the Rx FIFO.

When the Rx FIFO is disabled (MCR[RFEN] bit is negated), an individual mask is

provided for each available Rx mailbox on a one-to-one correspondence. When the Rx

FIFO is enabled (MCR[RFEN] bit is asserted), an individual mask is provided for each

Rx FIFO ID filter table element on a one-to-one correspondence depending on the setting

of CTRL2[RFFN] (see Rx FIFO).

-----------------------------------------------------------------------------------------------------------------------

If Rx FIFO is enabled with 10 filter elements, RXIMR0-9 will have one-to-one correspondence with RXFIFO filter elements. But, what about RXIMR10-31? Will RXIMR20 still correspond to MB20 when the RXFIFO is enabled? PetrS

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

yes, RXIMR20 still correspond to MB20.

BR, Petr