- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- confuse about QuadSPI ref clk

confuse about QuadSPI ref clk

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

confuse about QuadSPI ref clk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, all

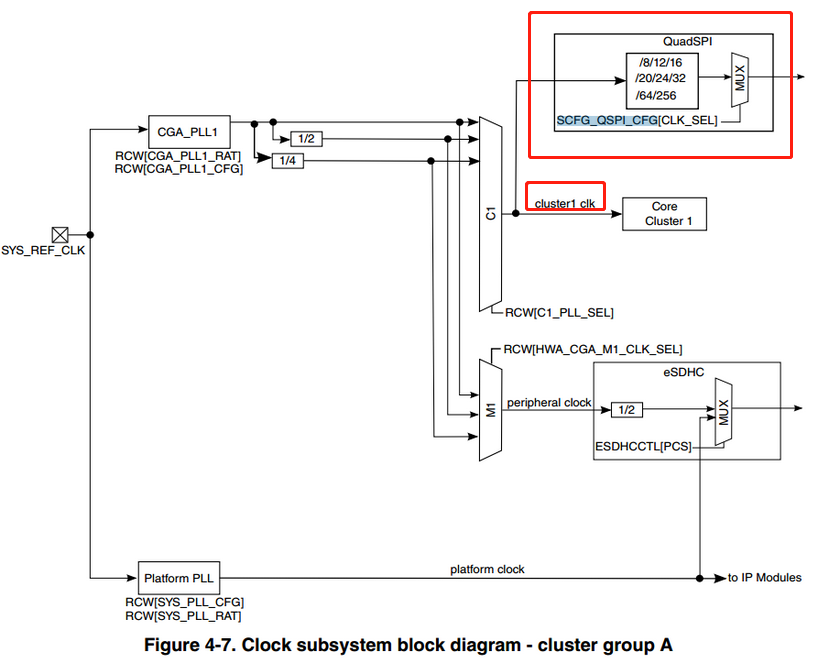

I notice there is a figure about QuadSPI, and it specify ref use "cluster1 clk". see below.

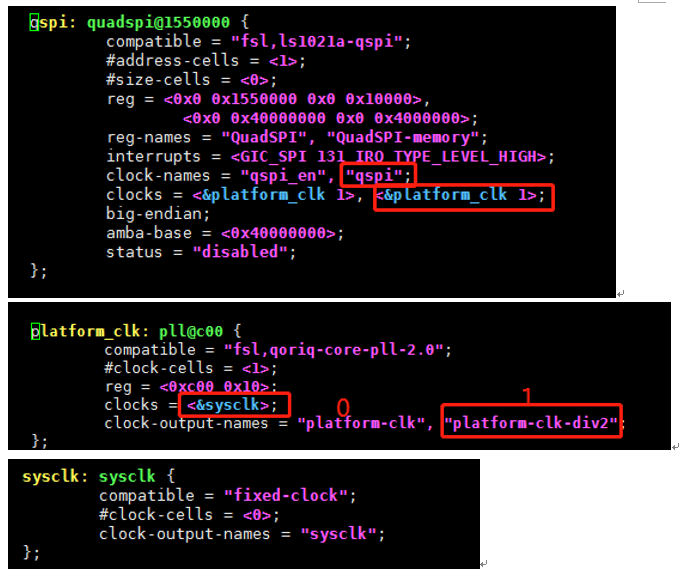

But at ls1021a dts, qspi clocks ref to platform_clk's "platform-clk-div2", and platform_clk ref to fixed-clock "sysclk" , as i know the sysclk is fixup to 100MHz at u-boot phare.

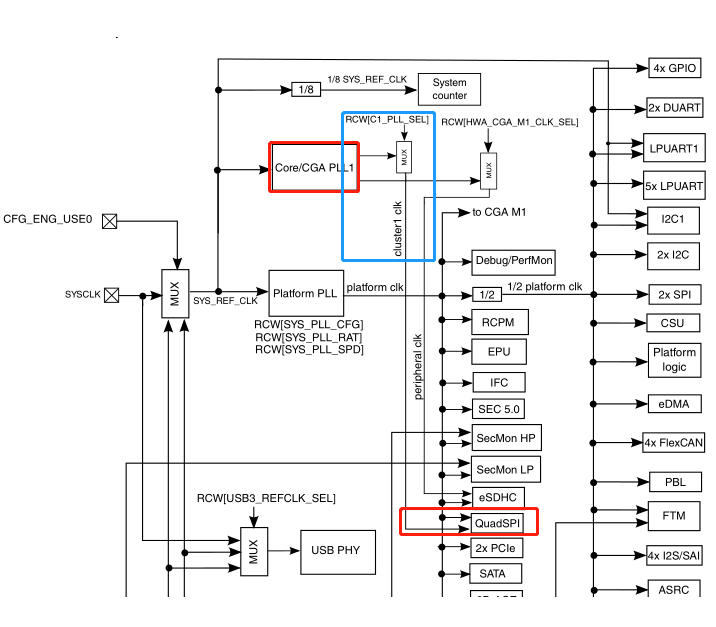

And there is another about QuadSPI, Is it says QuadSPI clk can be ref to "platform clk" or "cluster1 clk"? and how can we choice those ref clk?

and why ls1021a dts choice sysclk(100MHz) as qspi's the ref clk ?

(actually i find the QSPI_CLK is depend on CPU clock only, when i change the cpu freq by /sys/devices/system/cpu/cpu0/cpufreq/scaling_governor at run time )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to the LS1021A manual in the RCW phase QSPI gets sysclk and in the PBI Phase/Boot Phase it gets the core clock1. See 29.1.5 LS1021A QuadSPI module special consideration (LS1021ARM rev.3). It seems manuals Figure 4-8. “Clock subsystem block diagram - IP modules” reflects that.

If we look at

platform_clk: pll@c00 {

compatible = "fsl,core-pll-clock";

#clock-cells = <1>;

reg = <0xc00>;

clocks = <&sysclk>;

clock-output-names = "platform-clk", "platform-clk-div2";

we can find that "platform_clk" label actually points to the core pll clock. It also can confuse me. For device tree we should refer to corresponding binding documentation described which properties are accepted and its values. I have not checked but can suppose that "platform-clk", "platform-clk-div2"; corresponds to the Figure 4-7. “Clock subsystem block diagram - cluster group A” where C1_PLL_SEL selects direct and ½ options.