- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- LS1043A MDC/MDIO AC timing sequence

LS1043A MDC/MDIO AC timing sequence

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

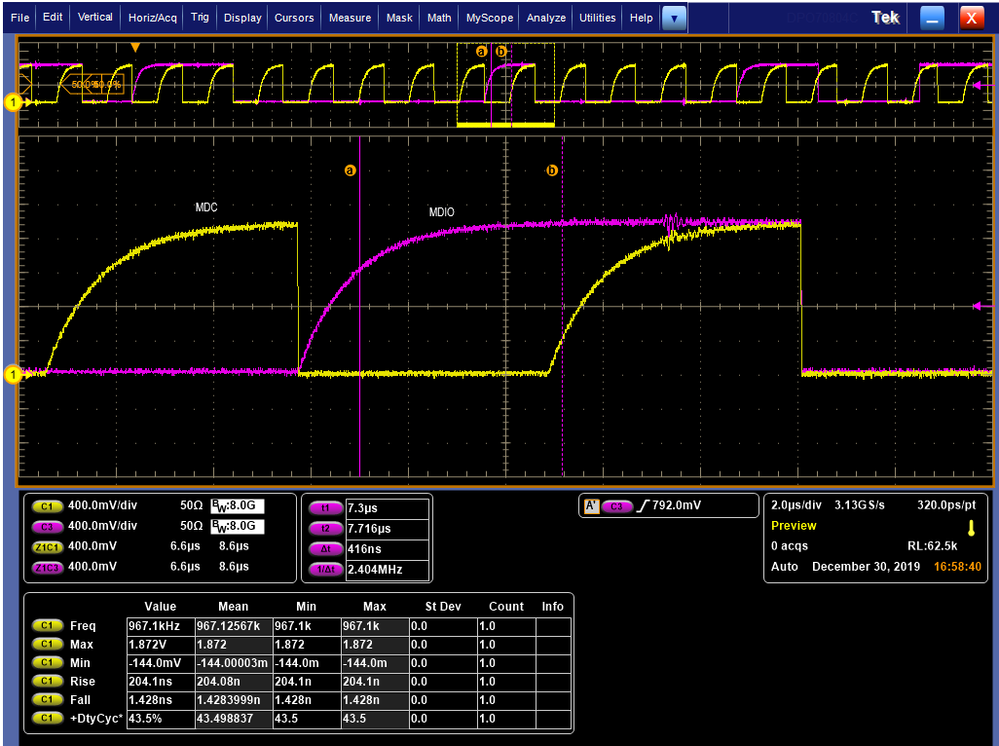

LS1043A 中EMI1_MDC/MDIO接口时序问题:

根据手册147页的示意图,写时序:EMI1在MDC上升沿延迟tMDKHDX后数据翻转,但是示波器实际测量MDC是在下降沿打出数据,如下图:这是手册描述问题还是有什么配置呢?

另外,读时序时:PHY在MDC的上升沿经过一段延迟后扇出数据,CPU也是利用这个上升沿采样吗?还是可以配置CPU使用下降沿采样?

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to the QorIQ LS1043A Data Path Acceleration Architecture (DPAA) Reference Manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

MDIO behaviour in the provided trace is valid.

Please check MDC to MDIO delay tMDKHDX controlled by the MDIO_CFG[MDIO_HOLD].

Please check whether MDIO_CFG[NEG]=1 then LS1043A will transmit data on falling edge of the clock.

This implies with MDIO_CFG[NEG]=1 the tMDKHDX should be measured with respect to the falling edge of clock.

> can I configure the CPU to use falling edge sampling?

No.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

where could I find these registers in the doc: QorIQ LS1043A Reference Manual Rev. 4, 6/2018.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Please refer to the QorIQ LS1043A Data Path Acceleration Architecture (DPAA) Reference Manual.