- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- iMX8M Mini Spread Spectrum

iMX8M Mini Spread Spectrum

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

iMX8M Mini Spread Spectrum

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone

I'm developing a product using an iMX8M mini running Linux, it's based on the NXP evaluation board.

I have built my Linux image using Yocto but I would like to enable spread spectrum on the CPU

Does anyone have and examples or documentation. I have tried Google but it hasn't turned up anything useful yet.

Regards

Mark Cullen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all!

After receiving the set of patches related to enabling the Spread Spectrum for i.MX 8M Mini from NXP, we at Toradex managed to help a customer enable the Spread Spectrum on the RAM clock for the Toradex module Verdin iMX8M Mini.

From that, we created a page to guide anyone who needs to use such a feature.

The page is now online: https://developer.toradex.com/software/linux-resources/linux-features/enabling-spread-spectrum-clock...

Hope this is helpful!

Best regards,

Henrique

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

did you have solved it ? I am also interested to enabling the spread spectrum for the MIPI DSI.

thanks Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We verified Spread Spectrum for the MIPI DSI on 8M Plus, it should apply in a similar way to 8MM and 8MN (not 8M).

Since BSP 5.10 the clock tree changed and the new DSI-PHY clock source (i.e. OSC_24) doesn't support SS. The Video PLL freq (1.0395GHz) showed some problems, normally the required clock for MIPI DSI-PHY couldn't be achieved due to missing fractional divider.

However, SS for DSI can be achieved by enabling spread spectrum of internal PLL of MIPI D-PHY and this is verified on iMX8MP EVK setup. Please try the attached patch to enable SS at MIPI D-PHY

=======================================================================

• sel_pf: 00-down spread, 01-up spread, 1x-center spread

• Modulation frequency (MF) = FFIN / p / mfr / (2^5) [Hz]

• Modulation rate (MR) = mfr × mrr / m / (2^6) × 100 [%]

• Where, 0 ≤ mfr ≤ 255, 1 ≤ mrr ≤ 63, 0 ≤ mrr × mfr ≤ 512

=======================================================================

Regards,

Bernhard.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i have tried your patch. As i am on the mainline kernel i have integrated your patch into the samsung-dsim.c.

But now my system hangs during boot after "initialized mxsfb-drm". Any idea what cause this boot stop?

[ 2.050882] sn65dsi83 2-002c: supply vcc not found, using dummy regulator

[ 2.059710] samsung-dsim 32e10000.dsi: Attached sn65dsi83 device (lanes:4 bpp:24 mode-flags:0x2e3)

[ 2.065902] mmc0: SDHCI controller on 30b40000.mmc [30b40000.mmc] using ADMA

[ 2.079673] mmc1: SDHCI controller on 30b50000.mmc [30b50000.mmc] using ADMA

[ 2.110563] [drm] Initialized mxsfb-drm 1.0.0 20160824 for 32e00000.lcdif on minor 1

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The i.MX8M Mini processor contains nine PLLs that allow to flexibly generate various clocks within the SoC. These PLLs are: ARM PLL, DRAM PLL, VPU PLL, GPU PLL, System PLL1, System PLL2, System PLL3, Audio PLL1, Audio PLL2, Video PLL1. Among these PLLs, DRAM PLL, Audio PLL1, Audio PLL2 and Video PLL1 have the spread spectrum function. For details about i.MX8M Mini SoC clock generation, please refer to the Section 5.1 "Clock Control Module (CCM)" of the i.MX8M Mini Reference Manual document, available on the processor's Documentation web page:

The spread spectrum mode parameters of all i.MX8M Mini PLLs that have this functionality can be calculated using the formulas below.

1. The modulation frequency can be calculated as:

MF = Fin / p / mfr / (2^5) [Hz]

where:

Fin - the input reference frequency (typically, 24MHz = 24 * (10^6)Hz);

p = CCM_ANALOG_XXX_YYY_FDIV_CTL0[PLL_PRE_DIV] - reference frequency pre-divider value;

mfr = CCM_ANALOG_XXX_YYY_SSCG_CTRL[PLL_MFREQ_CTL] - modulation frequency factor.

2. The modulation range can be calculated as:

MR = mfr * mrr / m / (2^6) * 100 [% percentage of the PLL output frequency]

where:

mfr = CCM_ANALOG_XXX_YYY_SSCG_CTRL[PLL_MFREQ_CTL] - modulation frequency factor;

mrr = CCM_ANALOG_XXX_YYY_SSCG_CTRL[PLL_MRAT_CTL] - modulation range factor;

m = CCM_ANALOG_XXX_YYY_FDIV_CTL0[PLL_MAIN_DIV] - PLL main divider value.

3. The CCM_ANALOG_XXX_YYY_SSCG_CTRL[SEL_PF] field controls the PLL output frequency sweep as follows.

00 - the main PLL output frequency is the upper sweep frequency;

01 - the main PLL output frequency is the lower sweep frequency;

1x - the main PLL output frequency is the center sweep frequency.

4. CCM_ANALOG_XXX_YYY_SSCG_CTRL[SSCG_EN] is the spread spectrum mode enable bit.

For PLL control register details, please refer to the Section 5.1.8 "CCM Analog Memory Map/Register Definition" of the document above.

The clock control driver of the Linux BSP does not support the spread spectrum mode, so, it should be modified appropriately according to the description above.

Best Regards,

Artur

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @art !

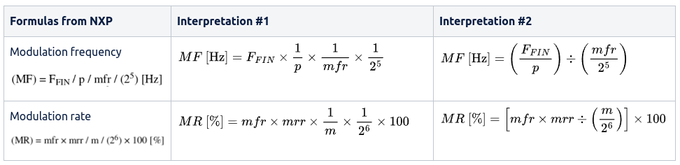

The way the formulas are written in the Reference Manual is a bit ambiguous.

Could you please confirm which of the interpretations below are correct for the spread spectrum formula?

Or, if none of the interpretations are correct, please let me know the correct interpretation.

Also, could you please point out the recommended "place" to enable the spread spectrum?

Maybe inside fracpll_configure?

Best regards,

Henrique