- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- How to get discrete DDR4 parameters for custom LS1046A board

How to get discrete DDR4 parameters for custom LS1046A board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to get discrete DDR4 parameters for custom LS1046A board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Hi all,

We designed a custom LS1046A board with 4GB DDR4,which use 4 NT5AD512M16A4-HRI(512MBx16).

The data bus is 64bits. And we use layerscape SDK 19.09, so we need modify the DDR initialization code in ATF component。

We defined CONFIG_STATIC_DDR, and try to figure out the struct ddr_cfg_regs from CodeWarrior DDR configuration tool.

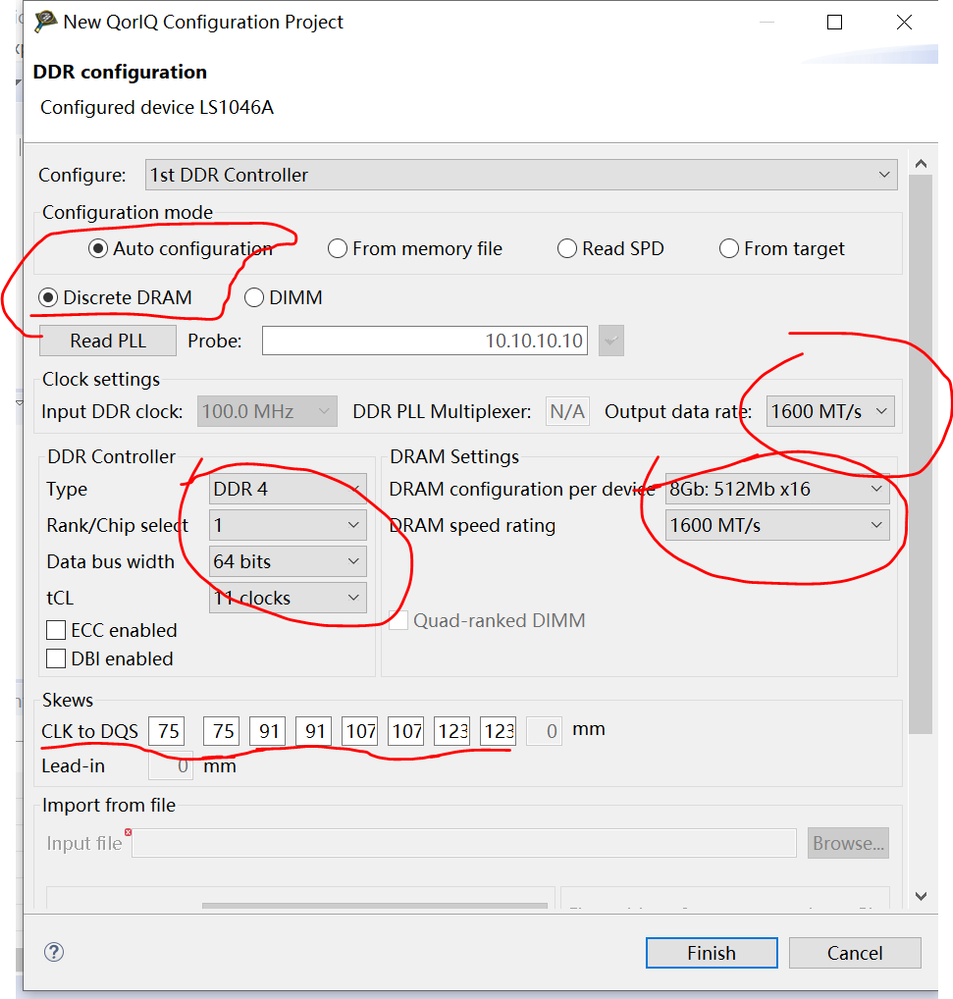

When creating the project, we chose Auto configuration mode, Discrete DRAM, and slect 1600MT/s for test, the skews between CKL and DQS is got from PCB tool.

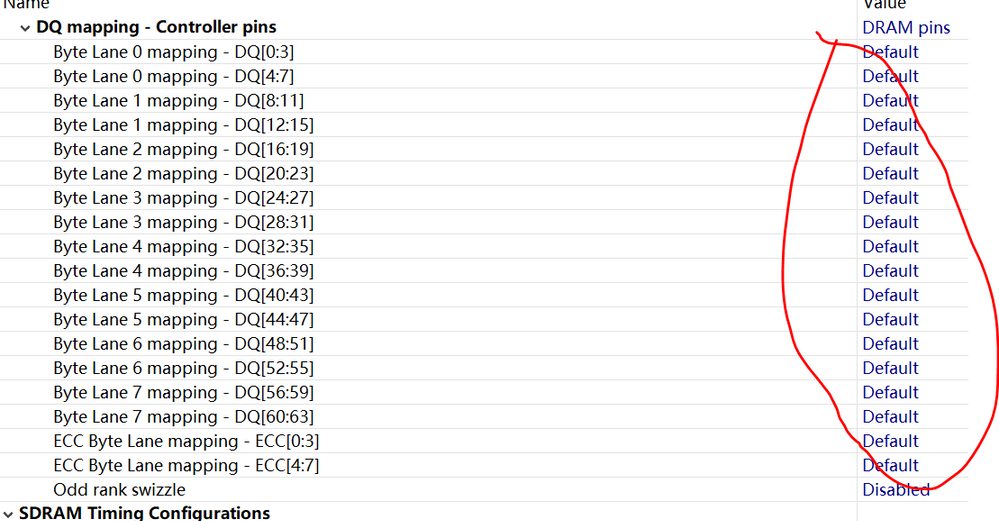

After enter Component Inspector page, we change the DQ mapping with Default,according with the schematic. The DQ pins didn't swap.

Keeping other parameters with the tools giving.

The following log is SD boot log.

There are 2 error:

1. DDR registers wirte error with Waiting for D_INIT timeout.

2. SD read error - DMA error = 10000000 in bl2 phase.

We dosen't have the hardware tools for DDR validation.

So how can we get the right DDR controller registers value without DDR validation? Anyone have some idea?

<QCVS DDR Tool User Guide> mentioned "Timing Configuration 1: Set four basic DDR timings: tCL, tRCD, tRP, tRAS specified usually as tCL-tRCD-tRP-

tRAS. Set rest of the parameters as per the datasheet of the DDR device." There are so many parameters in CodeWarrior, which are the important?

And in Error 2, the SD read error, what's the error code meaing?

By the way, we use custom RCW from CodeWarrior PLB configuration tool.

ATF LOG:

plat/nxp/soc-ls1046/soc.c get_boot_dev:374 INFO: RCW BOOT SRC is SD/EMMC

plat/nxp/soc-ls1046/soc.c get_boot_dev:374 INFO: RCW BOOT SRC is SD/EMMC

plat/nxp/drivers/sd/sd_mmc.c sd_mmc_init:1168 INFO: esdhc_emmc_init

plat/nxp/drivers/sd/sd_mmc.c esdhc_init:155 INFO: Card detected successfully

plat/nxp/drivers/sd/sd_mmc.c esdhc_emmc_init:1135 INFO: init done:

plat/nxp/soc-ls1046/ls1046ahtgw/ddr_init.c _init_ddr:390 INFO: platform clock 600000000

plat/nxp/soc-ls1046/ls1046ahtgw/ddr_init.c _init_ddr:391 INFO: DDR PLL1 2100000000

plat/nxp/soc-ls1046/ls1046ahtgw/ddr_init.c _init_ddr:392 INFO: DDR PLL2 0

plat/nxp/drivers/ddr/nxp-ddr/ddr.c dram_init:888 INFO: Time before programming controller 0 ms

plat/nxp/drivers/ddr/nxp-ddr/ddr.c dram_init:889 INFO: Program controller registers

plat/nxp/drivers/ddr/nxp-ddr/ddrc.c ddrc_set_regs:364 WARNING: Warning: Optimal CPO value not set.

plat/nxp/drivers/ddr/nxp-ddr/ddrc.c ddrc_set_regs:455 INFO: total size 4 GB

plat/nxp/drivers/ddr/nxp-ddr/ddrc.c ddrc_set_regs:456 INFO: Need to wait up to 1000 ms

plat/nxp/drivers/ddr/nxp-ddr/ddrc.c ddrc_set_regs:468 ERROR: Error: Waiting for D_INIT timeout.

plat/nxp/drivers/ddr/nxp-ddr/ddr.c write_ddrc_regs:817 ERROR: Writing DDR register(s) failed

plat/nxp/drivers/ddr/nxp-ddr/ddr.c dram_init:892 ERROR: Programing DDRC error

plat/nxp/soc-ls1046/ls1046ahtgw/ddr_init.c _init_ddr:404 ERROR: DDR init failed.

plat/nxp/common/ls_bl2_el3_setup.c populate_dram_regions_info:58 NOTICE: Incorrect DRAM0 size is defined in platfor_def.h

lib/xlat_tables_v2/xlat_tables_internal.c mmap_add_region_ctx:752 ERROR: mmap_add_region_check() failed. error -22

lib/xlat_tables_v2/xlat_tables_internal.c mmap_add_region_ctx:752 ERROR: mmap_add_region_check() failed. error -22

bl2/bl2_main.c bl2_main:32 WARNING: test

bl2/bl2_main.c bl2_main:32 INFO: test

bl2/bl2_main.c bl2_main:33 NOTICE: BL2: v1.5(release):LSDK-19.09-dirty

bl2/bl2_main.c bl2_main:34 NOTICE: BL2: Built : 16:53:17, Feb 14 2020

bl2/bl2_main.c bl2_main:38 NOTICE: BL2: bl2_arch_setup

plat/nxp/soc-ls1046/soc.c mem_access_setup:232 INFO: Configuring TrustZone Controller

drivers/arm/tzc/tzc400.c tzc400_configure_region:189 INFO: Value of region base = 7fdffffb

drivers/arm/tzc/tzc400.c tzc400_configure_region:189 INFO: Value of region base = 7ffffffb

drivers/arm/tzc/tzc400.c tzc400_configure_region:189 INFO: Value of region base = fbdffffb

bl2/bl2_main.c bl2_main:46 NOTICE: BL2: bl2_plat_preload_setup

bl2/bl2_image_load_v2.c bl2_load_images:36 NOTICE: BL2: plat_get_bl_image_load_info

bl2/bl2_image_load_v2.c bl2_load_images:53 INFO: BL2: Doing platform setup

bl2/bl2_image_load_v2.c bl2_load_images:55 NOTICE: BL2: bl2_platform_setup

bl2/bl2_image_load_v2.c bl2_load_images:61 NOTICE: BL2: bl2_plat_handle_pre_image_load

bl2/bl2_image_load_v2.c bl2_load_images:68 INFO: BL2: Loading image id 3

plat/nxp/drivers/sd/sd_mmc.c esdhc_read_data_dma:611 ERROR: SD read error - DMA error = 10000000

plat/nxp/drivers/sd/sd_mmc.c esdhc_read:1302 ERROR: Read error = fffffffb

common/bl_common.c load_image:229 WARNING: Failed to obtain reference to image id=3 (-2)

bl2/bl2_image_load_v2.c bl2_load_images:71 NOTICE: BL2: load_auth_image

bl2/bl2_image_load_v2.c bl2_load_images:73 ERROR: BL2: Failed to load image (-2)

Authentication failure

The attachments are the rcw file and DDR controller registers from Codewarrior.

welcome for any comments . TKS!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello 文炳 项,

For discrete DDR4 parameters configuration, first you need to create a QCVS DDR Memory Controller Configuration project with default configuration parameters, then modify parameters in Properties panel according to your DDR datasheet to generate the initial DDR controller configuration parameters, then use DDRv tool to connect to the target board to do validation, optimization and operational DDR test.

Please refer to https://community.nxp.com/docs/DOC-333349

You could configure your target board as hard-coded RCW first, then do DDR validation with DDRv tool.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to this thread of discussion, the user has 16GB of DDR4. That said, within the Properties page of the CodeWarrior TAP QorIQ Configuration DDR Memory Controller project, what would be the Chip Select 0->Memory Boards->Start Address?

I've got 4 GB of DDR4 memory for an LS1046AFRWY processor and whether I use Start Address of 0x0000 0000, 0x8000 0000, or 0x8 8000 0000, the board_static_ddr() routine ALWAYS return 0x80000000 as the dram_size. As you know, 0x80000000 is 2GB, not 4GB.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As a clarification, our 4GB size of DDR4 memory is split into 2 chips at 2GB per chip so that internally to the DDR controller, the DDR chips should be organized into DRAM0 and DRAM1. So, how do I configure the Chip Select 0->Memory Boards->Start Address to start the DDR Training? Also, I assume that I need to set the Chip Select 0->Memory Boards->Size (in MB) to 4GB. Is this correct?

At the end of the day, the board_static_ddr() return value needs to be 4GB (0x1 0000 0000) so that each "bank" is recognized by the DDR controller: 1 DDR chip as DRAM0 and the other DDR chip as DRAM1.

Please help. Even if I use the above parameters for configuring the DDR controller and then run the DDR training, the board_static_ddr() function ALWAYS sets the return value, which is captured as the dram_size in the ddr.c code as 0x8000 0000, or 2GB.

Thank you,

Scott Welsh

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping

Thank you for reply.

My problem is I dosen't have Codewarrior TAP hardware tools. So i can't run DDRv tool to get the optimization parameters .

No I slow down the DDR rate to 1250MT/s,and use the register value from QCVS DDR Memory Controller Configuration. It can run to up kernel, but fail at init SD card.

So Yiping, could you have some suggestion about how to optimize the parameters without Codewarrior TAP.

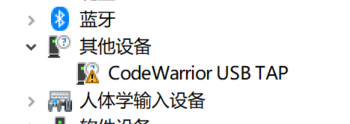

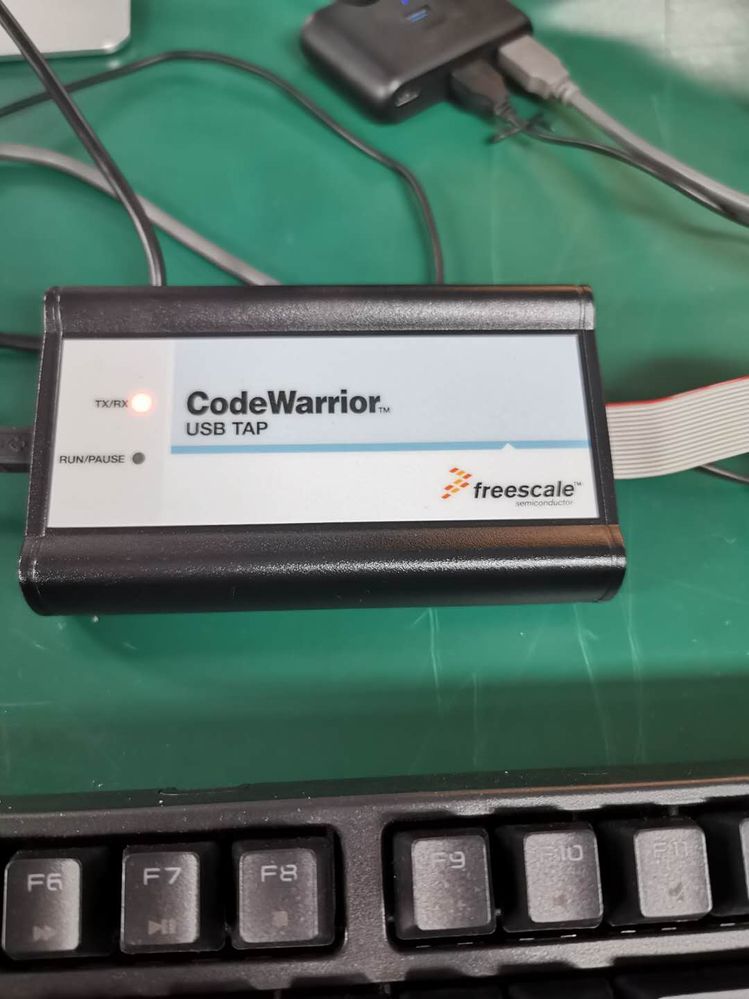

BTY, I have a tools: Codewarrior USB TAP, can it work for LS1046A?

I install CodeWarrior Development Studio for QorIQ LS series - ARM V8 ISA V11.4,but the Codewarrior USB TAP couldn't find the right driver.

Where can I download the right driver?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello 文炳 项,

In your screenshot, it seems that you are using CodeWarrior TAP (only integrates USB port), which only supports PowerPC target board.

Please purchase CodeWarrior TAP and probe tip for Layerscape from CodeWarrior® TAP | NXP .

Regarding USB TAP driver problem.

Please reinstall driver in Freescale\CW4NET_v2019.01_test\Common\CCS\drivers\usb.

If this problem remains, please try to use CodeWarrior TAP Ethernet connection.

Please refer to "Chapter 2 Connecting to Network" in the attached user manual to set up CodeWarrior TAP Ethernet connection.

Thanks,

Yiping

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Yiping

Do you have some suggestion without without of CodeWarrior TAP.

Like change some parameters.

Right now i solw down DDR rate to 1600, and change DDR pll to 1600 in RCW, the BL2 show DDR init successed, buf BL31 vaildation failed.

Then I disable SD DMA operation in BL2, the ATF can run to boot BL31, but failed.

So i continue to slow down ddr rate to 1250MT/s, change DDR pll to 1200 in RCW. It can run untile linux kernel init SD failed.

According to the trace, it failed at get CID with error code -110, in sub function wait_for_app_cmd.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

CodeWarrior TAP is necessary for you to use DDRv tool to do validation and optimization on the custom board.