- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- Product Forums

- :

- 8-bit Microcontrollers

- :

- I2C-bus Status Register Descriptions

I2C-bus Status Register Descriptions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I2C-bus Status Register Descriptions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

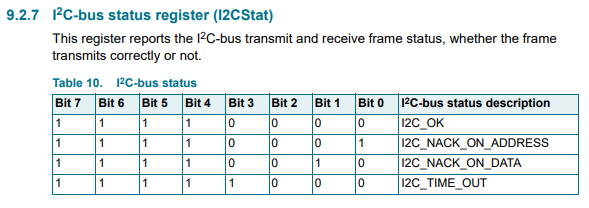

I am working with the MSP430FR2311 that has the SC18IM700 chip. I was writing tests for I2C master and slave communication between two of the same board. One is programmed as a master and the other as a slave. I was getting unexpected behavior when trying to test the I2CSTAT register values. Specifically the I2C_NACK_ON_DATA as seen below.

When sending a write command to the chip and receiving a nack after the address is sent it is being registered as a I2C_NACK_ON_DATA. I would think this should be considered a I2C_NACK_ON_ADDRESS instead. Is my assumption correct? I wasn't able to find proper documentation explaining when these different statuses are supposed to be set. If you could provide a better description of each status or link me to somewhere that describes this that would be best.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

I found out that there was a bug with my slave device that was causing this issue to occur. I was able to resolve the issue after fixing this bug. Thank you for your help on this.

Thanks,

Andrew

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Tomas,

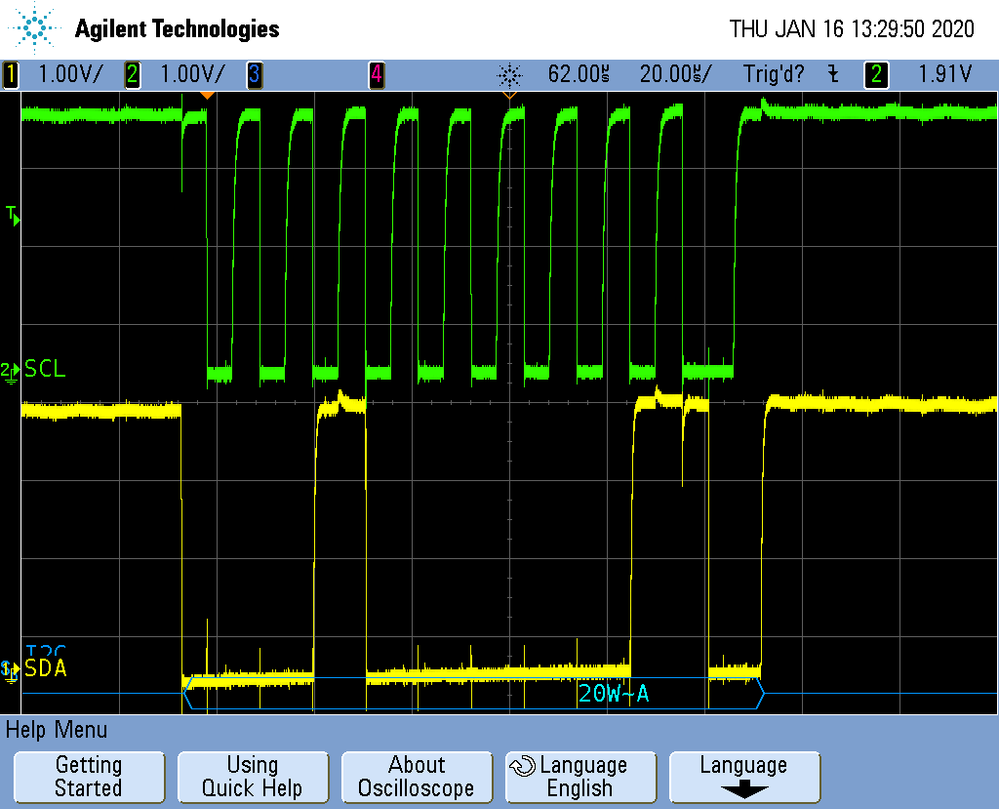

Below is an image showing the NACK on address for a write command. When I check the I2C_STAT register it is set to I2C_NACK_ON_DATA. If I do a read command and the NACK occurs here it is seen as a I2C_NACK_ON_ADDRESS. It should be a I2C_NACK_ON_ADDRESS in both cases. That is what I think.

Thanks,

Andrew

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrew,

I have looked into this and the device seems to respond properly. I just send an I2C address of the non-existing device and read the I2CStat, I read 0xF1 which is I2C_NACK_ON_ADRRESS.

If you wait for a little then read back I2CStat register, would it still be 0xF2? Can you try to run the same test right after power up without doing anything before the test, would you still read 0xF2? What is the UART sequence you did send?

Best regards,

Tomas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andrew,

This is a pretty old device and I do not have any other documents besides the data sheet.

However, I will try to find a board to duplicate the issue. Could you please capture the I2C trace of the NACK of address with a scope and post it here? I want to make I can duplicate the same sequence.

Best regards,

Tomas