- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Behavior of SCU_WDOG_OUT pin

Behavior of SCU_WDOG_OUT pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Behavior of SCU_WDOG_OUT pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

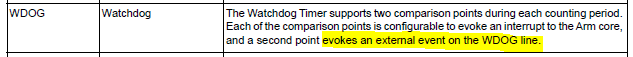

I found following description in datasheet. It means that iMX8QXP will output high signal after watchdog timer is expired.

Is it right? Can I assert SCU_WDOG_OUT signal any other way?

Best Regards,

Kazuma Sasaki.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

"And if hardware had connected the SCU_WDOG_OUT pin from iMX8QXP to PMIC's WDI pin, then during SOC reset, the PMIC will also do hard reset to make a POR reboot for the whole system.”

We also have to configure IMX8QXP_SCU_GPIO0_01_SCU_WDOG0_WDOG_OUT isn't it? If so, which node should use this ball configuration? For example, imx8mp has a wdog1 node for this purpose, is there any equivalent for QXP as well?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

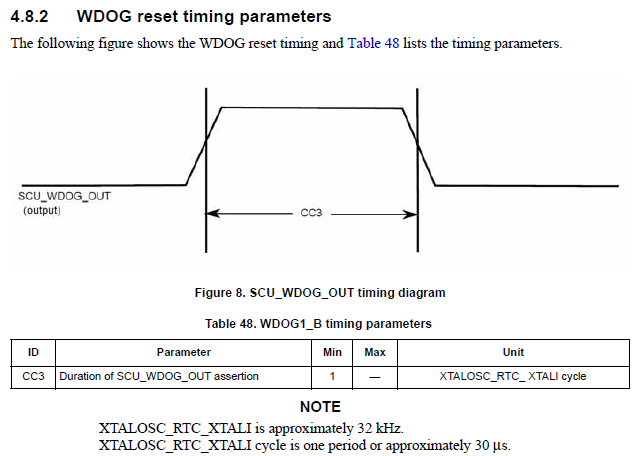

1)It means that iMX8QXP will output high signal after watchdog timer is expired.

> do you mean after watchdog timer is reset?

2)pls find the pic as below about reset case

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Joan,

I appreciate your support.

Currently we are connecting SCU_WDOG_OUT pin to PMIC's WDI pin same as MEK design.

When iMX assert SCU_WDOG_OUT, PMIC will start the reset operation.

therefore, I would like to know the conditions under which SCU_WDOG_OUT is asserted.

iMX8DX contain two watchdog modules in SCU and M4 subsytem.

I don't understand the relevance of both modules to SCU_WDOG_OUT pin.

Best Regards,

Kazuma Sasaki.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

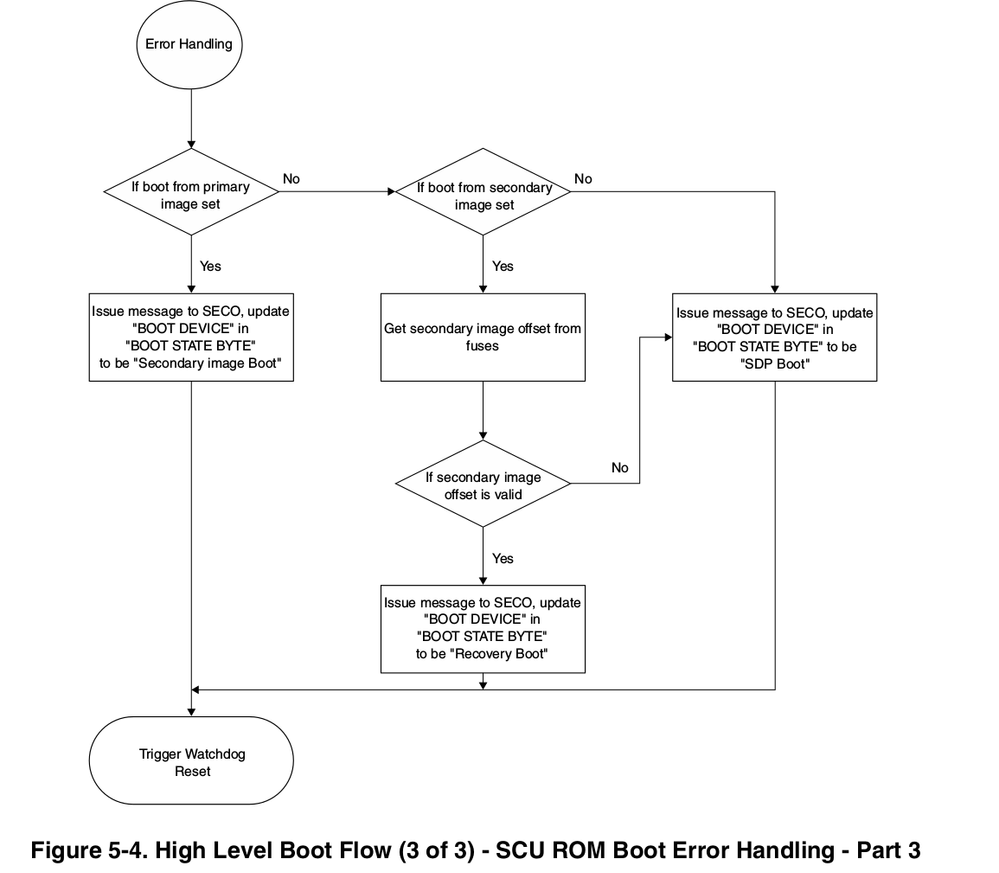

refer to the Reference Manual, After loading an image. If the image is bigger than the size which can be loaded

within the WDOG timeout, depending on the image size and the speed of the boot interface, a WDOG timeout will occur and the chip will reset.

for M4 and SCU, This chip features one configurable Cortex-M4 subsystem and a dedicated Cortex-M4 subsystem within the SCU,The SCU is made of a Cortex-M4 processor and a set of peripherals and interfaces to connect to external PMIC and to control internal subsystems.

one also can refer to the SCFW document as below, pls focus on the

“ote:

In default SCFW, it had already used internel watchdog to make sure SCFW is always running, if SCFW is built as no debug version (M=0 D=0), all SCFW halt will cause SOC reset. And if hardware had connected the SCU_WDOG_OUT pin from iMX8QXP to PMIC's WDI pin, then during SOC reset, the PMIC will also do hard reset to make a POR reboot for the whole system.”