- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX Forums

- :

- i.MX RT

- :

- Optimizing eLCDIF throughput

Optimizing eLCDIF throughput

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Optimizing eLCDIF throughput

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

My LCD is 1280x800 and it does not need Vsync and Hsync. It only uses DE ( data enable.)

The issue I’m having now is that I can’t meet the target of 15 frames per second even if I’m using 16 bits color depth pixel.

How can I optimize my eLCDIF speed so that I can have 15 frames/second. The frame buffers are stored in 8MB non-cacheable SDRAM.

Thank you in advance for your help!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please give the part number/ data sheet of this 1280x800 datasheet. I in fact want to order this LCD and compare the performance. Thank you !

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andre marcus,

I already contact with the AN author, he tell me it is WKS101WX001-WCT.

I attach the datasheet.

Wish it helps you!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any updates Kerry on my issue; I need to wrap up this issue; if the mcu speed can’t drive this LCD I need to go for a faster processor.

Please confirm where this mcu can make it or not. If it can make it please pinpoint the cause of this slow display rate.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andre marcus,

RT is the crossover processor, the process speed already very high in the MCU domain, rt1060 speed can upto 600Mhz.

As you know, our AN12302 also prove the 1280*800 lcd can work with 60 frames/second, but the LCD is the normal LCD, not like your LCD, your LCD even don't connect the HSYNC and VSYCN, I don't know how do your LCD do the related synchronize and whether it can works with high data clock, all HSYNC and VSYNC is connect to 0 is a little

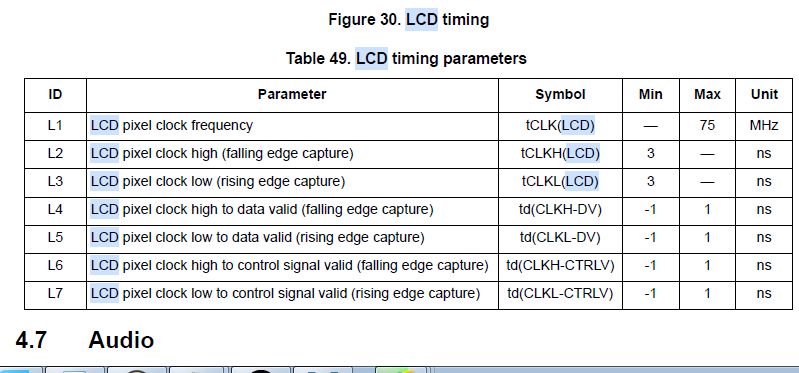

You can check it with your LCD side, when you configure it as 71Mhz, as you know, the LCD module in the RT chip can up to 75Mhz.

Best Regards,

Kerry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The datasheet: https://www.avnet-integrated.eu/fileadmin/user_upload/G101ICE-L01.pdf page 17 shows that Vsync and Hsync needs to be connected to ground( looking at RxIN1 channel). The LCD uses only DE( which goes high when data is valid and low when no data is valid. DE is driven by the eLCDIF.

I would like to know what's slowing down my LCD throughput.

Below is how I am generating 35.25 MHz. I am trying to have only 30 frames per second, but still cant make it.

clock_video_pll_config_t config = {

.loopDivider = 23, //47,

.postDivider = 16,

.numerator = 0,

.denominator = 0,

};

CLOCK_InitVideoPll(&config); /*

* 000 derive clock from PLL2 * 001 derive clock from PLL3 PFD3

* 010 derive clock from PLL5

* 011 derive clock from PLL2 PFD0

* 100 derive clock from PLL2 PFD1

* 101 derive clock from PLL3 PFD1 */

CLOCK_SetMux(kCLOCK_LcdifPreMux, 2);

CLOCK_SetDiv(kCLOCK_LcdifPreDiv, 0);

CLOCK_SetDiv(kCLOCK_LcdifDiv, 0);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

From your description, the issue should still in the LCD time configuration side.

Do you try to set more quick pixel clock frequency?

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I initially set the pixel frequency to 70.5 MHz, then I changed it to 35 MHz. I saw no improvement when I lowered the pixel frequency. When I used 20 MHz I was not able to see anything on the screen.

Contacted the lcd maker, they said vsync and Hsync needs to be set to logic level 0. I tried that but I saw no change in performance.

Cheers

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andre marcus,

Please tell me, how do you change pixel frequency, please give me your 70.5Mhz, 35Mhz, and 20Mhz related configuration code.

BTW, please also check with your LCD maker, what's the max frame per second can your LCD receive and display has no problem.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------